Polarization-doped inn-based tunneling field-effect transistor and manufacturing method thereof

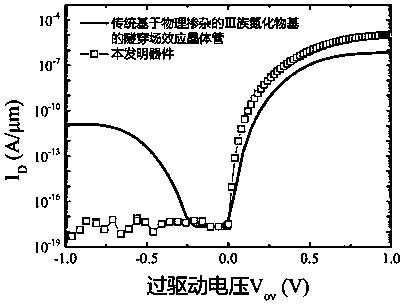

A tunneling field effect and polarization doping technology, applied in the fields of diodes, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of reduced device reliability, increased process complexity, and reduced device performance, and improved reliability. stability, reduce subthreshold swing, and improve the effect of modulation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

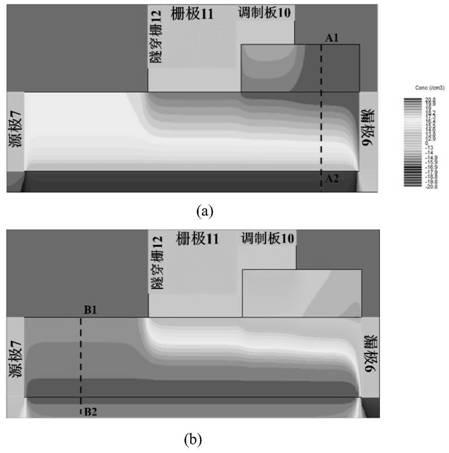

[0062] Embodiment 1: Fabricate a polarization-doped InN-based tunneling field-effect transistor with a polarization inversion layer thickness of 24 nm.

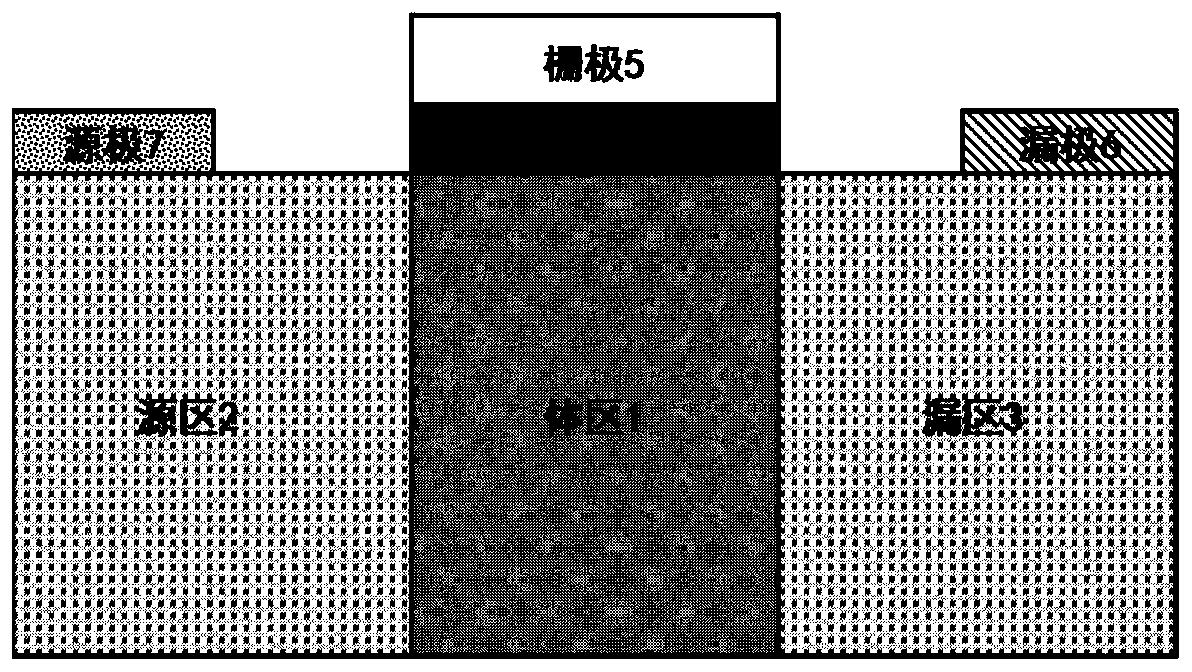

[0063] Step 1. Make a drift layer 2 on the substrate 1, such as image 3 b.

[0064] Use sapphire as the substrate 1, and use metal organic chemical vapor deposition technology to epitaxially unintentionally doped GaN semiconductor material with a thickness of 1000nm in the [0001] crystal direction on the substrate 1 to form a drift layer 2, wherein the process used for epitaxy The conditions are: the temperature is 950° C., the pressure is 40 Torr, the hydrogen gas flow rate is 4000 sccm, the ammonia gas flow rate is 4000 sccm, the gallium source flow rate is 100 μmol / min, and the epitaxy time is 2 h.

[0065] Step 2. Make body region 3, such as image 3 c.

[0066] On the buffer layer 2, the unintentionally doped InN semiconductor material with the [0001] crystal orientation is epitaxed by molecular beam epitaxy technolo...

Embodiment 2

[0088] Embodiment 2: Fabricate a polarization-doped InN-based tunneling field-effect transistor with a polarization inversion layer thickness of 10 nm.

[0089] Step 1. Make drift layer 2 on substrate 1, such as image 3 b.

[0090] Using silicon carbide as the substrate 1, metal organic chemical vapor deposition technology is used on the substrate 1 at a temperature of 950°C, a pressure of 40 Torr, a hydrogen flow rate of 4000 sccm, an ammonia gas flow rate of 4000 sccm, and a gallium source flow rate of 100 μmol / min. The drift layer 2 is formed by epitaxially using the unintentionally doped GaN semiconductor material with a thickness of 750 nm in the [0001] crystal orientation under the process condition of an epitaxial time of 1.5 h.

[0091] Step 2. Make body region 3, such as image 3 c.

[0092] On the buffer layer 2, use molecular beam epitaxy technology at a vacuum degree of less than or equal to 1.0×10 -10 mbar, the RF power is 400W, and the reactant is N 2 1. A ...

Embodiment 3

[0114] Embodiment 3: Fabricate a polarization-doped InN-based tunneling field-effect transistor with a polarization inversion layer thickness of 1.2 nm.

[0115] Step A. Make a drift layer 2 on the substrate 1, such as image 3 b.

[0116] GaN material is used as the substrate 1, and the unintentionally doped GaN semiconductor material with a thickness of 500nm in the [0001] crystal orientation is epitaxially used on the substrate 1 by metal-organic chemical vapor deposition technology to form a drift layer 2, wherein the epitaxy adopts The process conditions are: temperature 950°C, pressure 40Torr, hydrogen flow rate 4000sccm, ammonia flow rate 4000sccm, gallium source flow rate 100μmol / min, epitaxy time 1h.

[0117] Step B. Make body region 3, such as image 3 c.

[0118] On the buffer layer 2, use the molecular beam epitaxy technique to epitaxy the unintentionally doped InN semiconductor material with the [0001] crystal orientation to form the bulk region 3 with a thickn...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More