A ceramic substrate copper cladding and high-power electronic chip all-copper interconnect packaging scheme

A technology of ceramic substrates and electronic chips, applied in circuits, electrical components, electrical solid devices, etc., can solve the problems of reducing thermal and electrical conductivity of packaging, cost, and increasing the risk of packaging failure, so as to improve thermal and electrical conductivity, reduce interface loss, The effect of reducing the temperature of the copper clad process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

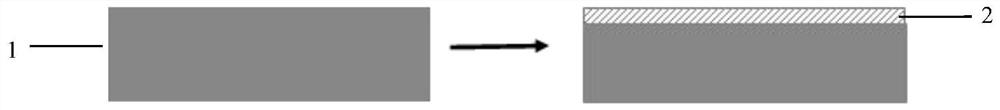

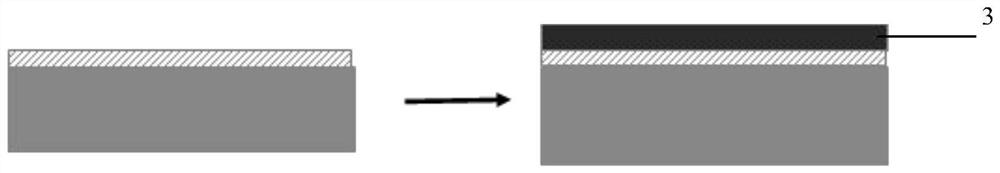

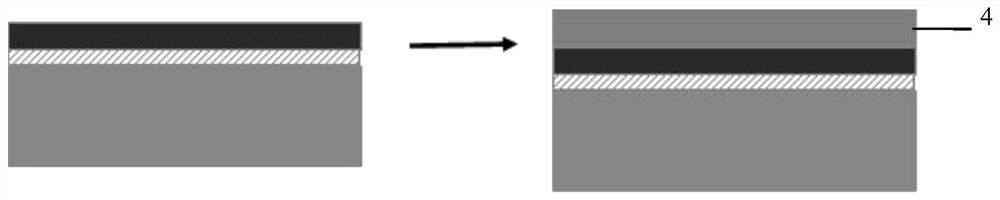

[0027] A preferred method for implementing a new design for copper cladding on a ceramic substrate and packaging, comprising the following preparation steps: vapor deposition of a 100nm Ti / 500nm copper layer on the surface of an alumina ceramic substrate; (2) coating the surface of the layer with a nano-copper cross-linking agent, according to the packaging The design needs to be printed into a circuit; (3) Then, place it in a nitrogen environment at a temperature of 100 ° C and bake for 30 minutes; (4) Place the chip on the baked substrate; (5) Coat the chip pad The nano copper paste is connected with the copper clip; (6) the whole chip is connected to the substrate through a hot pressing process, and a mixed gas of 8% hydrogen and 92% nitrogen is introduced, the pressure is raised to 15MPa, the sintering temperature is 300 ℃, and the sintering is 10min;

[0028] The above packaging results: the chip shearing force is 20MPa, and the thermal cycle test (-55℃~150℃) is more than ...

Embodiment 2

[0030] A preferred method for implementing a new design for copper cladding on a ceramic substrate and packaging, comprising the following preparation steps: vapor deposition of a 100nm Ti / 1000nm copper layer on the surface of an alumina ceramic substrate; (2) coating the surface of the layer with a nano-copper cross-linking agent, according to the packaging The design needs to be printed into a circuit; (3) Then, place it in a nitrogen environment at a temperature of 100 ° C and bake for 30 minutes; (4) Place the chip on the baked substrate; (5) Coat the chip pads with nanometers The copper paste is connected with the copper clip; (6) the whole chip is connected to the substrate through a hot pressing process, 8% hydrogen and 92% nitrogen are introduced, the pressure is raised to 15MPa, the sintering temperature is 300°C, and the sintering is 10min;

[0031] The above packaging results: the chip shearing force is 25MPa, and the thermal cycle test (-55℃~150℃) is more than 500 c...

Embodiment 3

[0033] A preferred method for implementing a new design for copper cladding and packaging on a ceramic substrate, comprising the following preparation steps: vapor deposition of a 500nm copper layer on the surface of an alumina ceramic substrate; (2) coating the surface of the layer with a nano-copper cross-linking agent, and printing according to packaging design requirements (3) Then, place the chip in a nitrogen environment, at a temperature of 100°C, and bake for 30 minutes; (4) Place the chip on the baked substrate; (5) Coat the chip pad with nano-copper paste and Copper clip connection; (6) The whole chip is connected to the substrate through a hot pressing process, 8% hydrogen and 92% nitrogen are introduced, the pressure is raised to 15MPa, the sintering temperature is 300°C, and the sintering is 10min;

[0034] The above package results: the chip shear force is 10MPa.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More