Trench etching method

A trench and etching rate technology, which is applied in the manufacture of electrical components, circuits, semiconductors/solid-state devices, etc., can solve the problems of Poly affecting the trench etching atmosphere, poor etching selectivity, and inapplicability, so as to eliminate Adverse effects, improvement of trench etching quality, and effects of preventing abnormalities

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

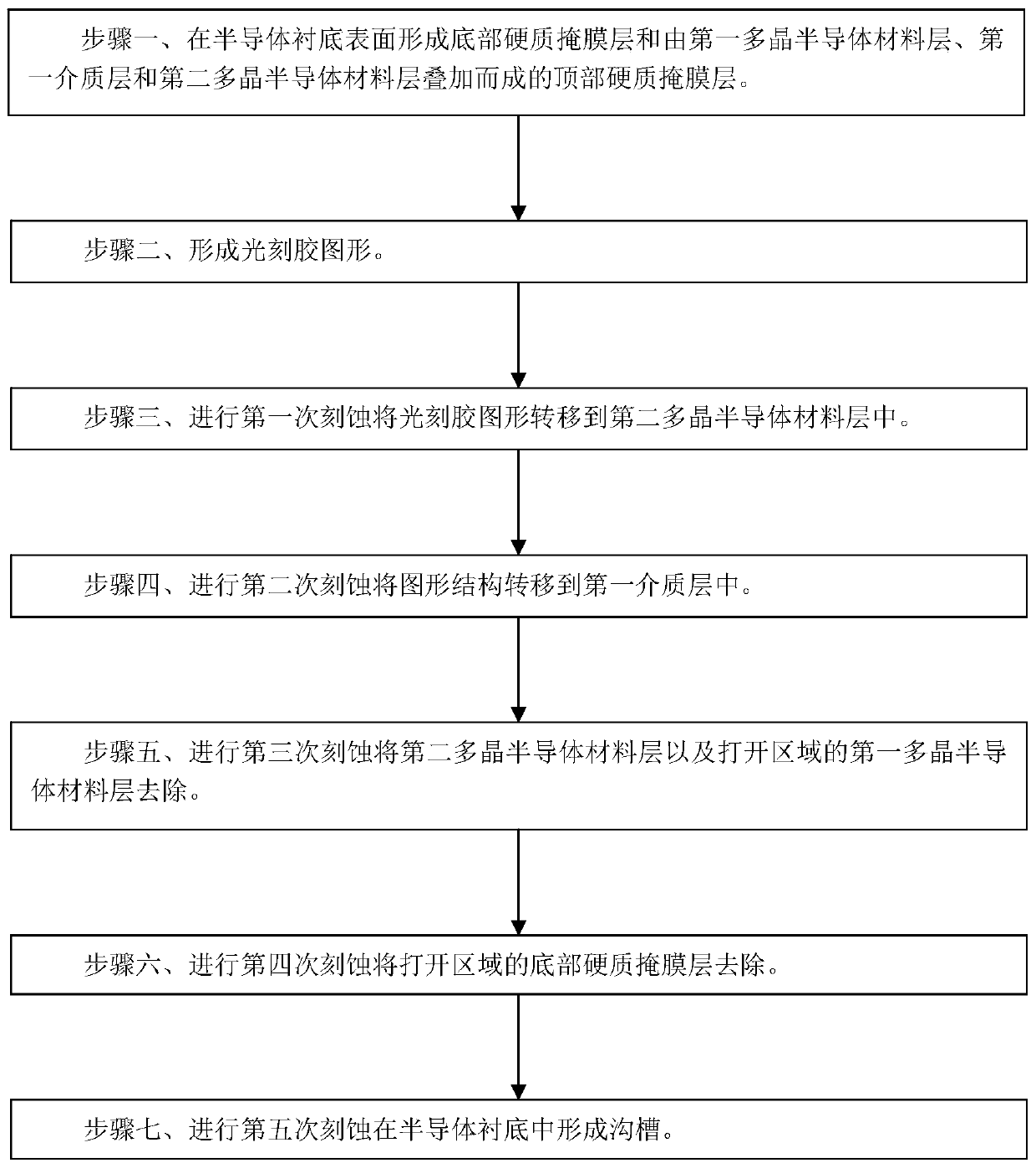

[0042] Such as figure 1 Shown is the flow chart of the etching method of the groove of the embodiment of the present invention; Figure 2A to Figure 2M Shown is a schematic diagram of the device structure in each step of the trench etching method of the embodiment of the present invention; the trench etching method of the embodiment of the present invention includes the following steps:

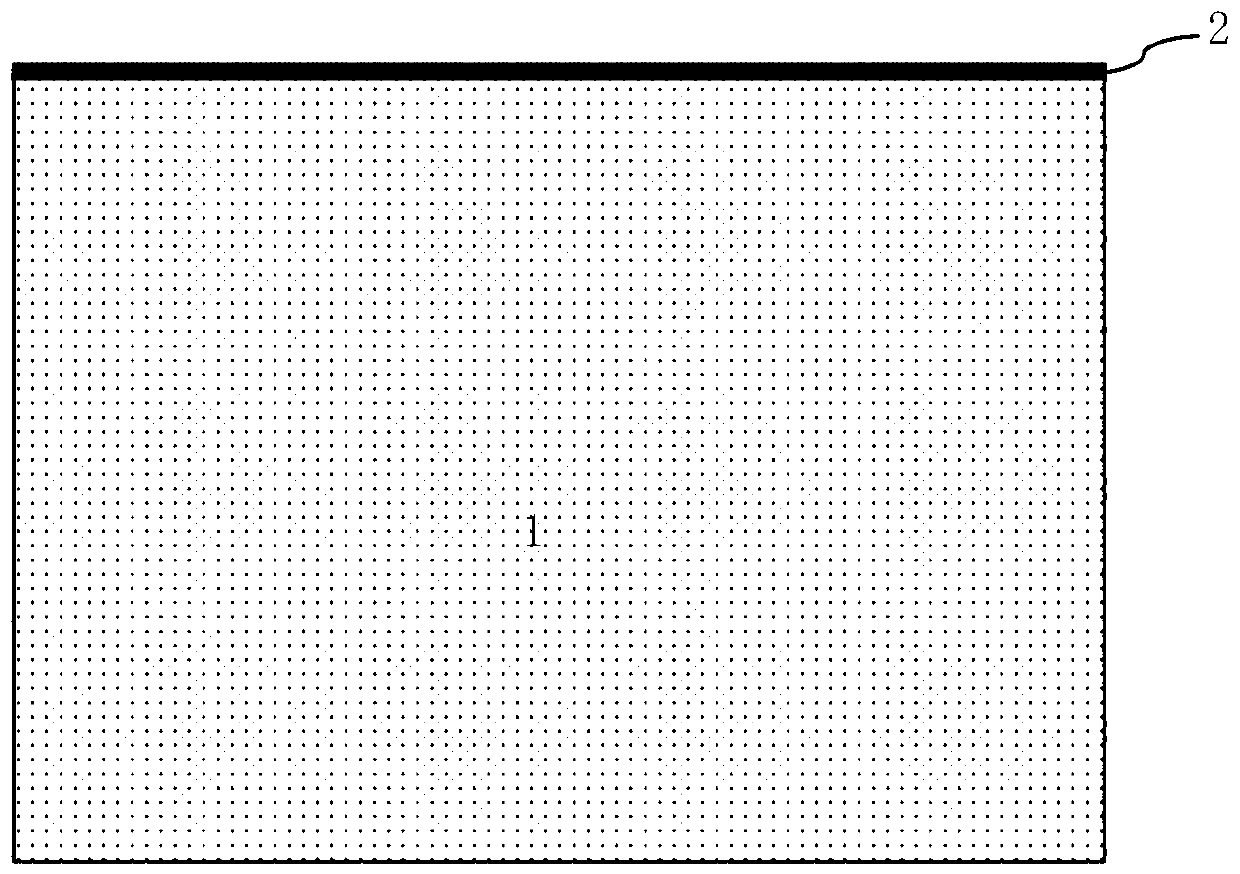

[0043] Step 1, such as Figure 2A As shown, a semiconductor substrate 1 for forming trenches 7 is provided, and a bottom hard mask layer 2 is formed on the surface of the semiconductor substrate 1 .

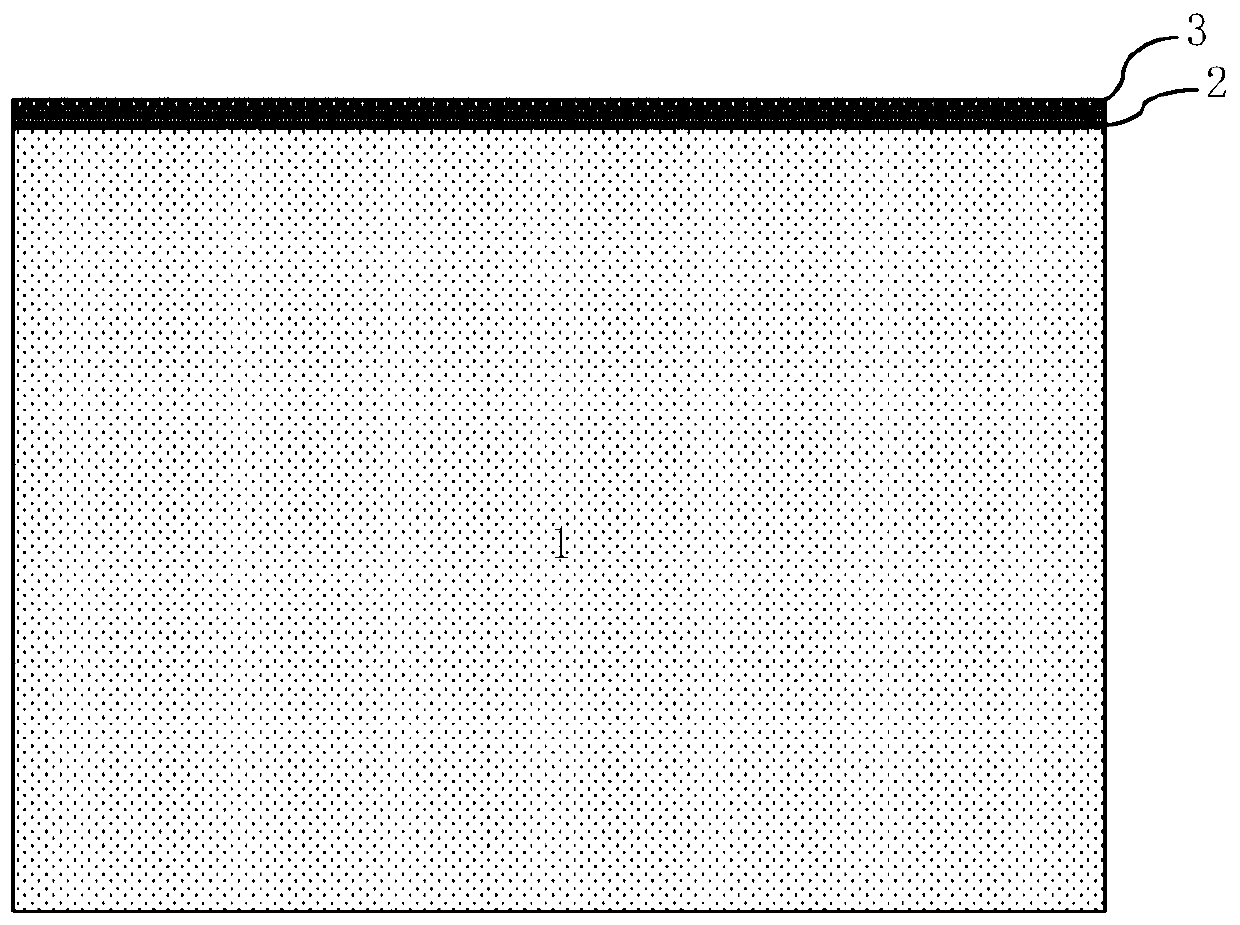

[0044] Such as Figure 2B As shown, a first polycrystalline semiconductor material layer 3 is formed on the surface of the bottom hard mask layer 2 .

[0045] Such as Figure 2C As shown, a first dielectric layer 4 is formed on the surface of the first polycrystalline semiconductor material layer 3 .

[0046] Such as Figure 2D As shown, a second polycrystalline semiconductor material laye...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More