Method for processing core layer of arbitrary-layer interconnected high-density circuit board

A technology of arbitrary layer interconnection and processing method, applied in the direction of printed circuit, printed circuit manufacturing, and the formation of electrical connection of printed components, which can solve the problems of inability to directly manufacture ultra-fine circuits and affect product quality, saving resources and reducing production. cost effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

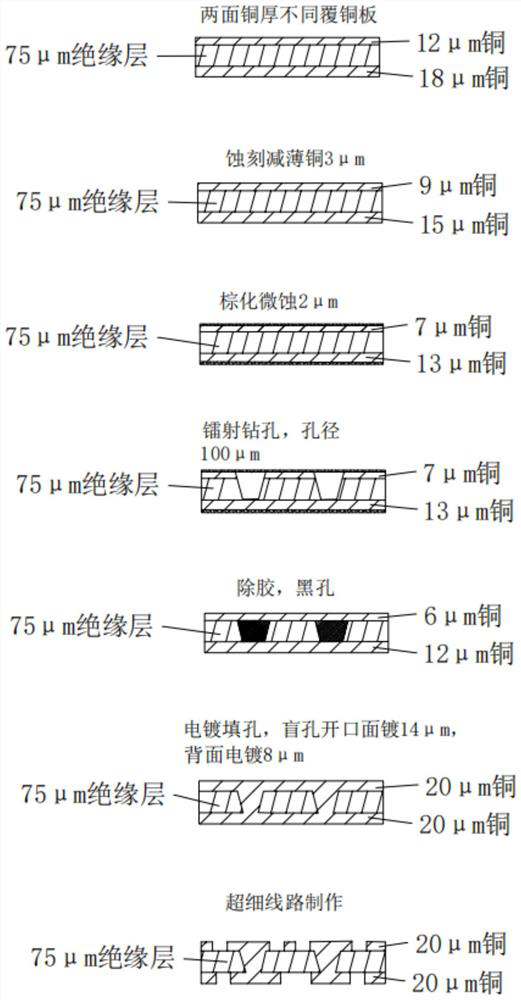

[0039] refer to figure 1 , a method for processing a core layer of a high-density circuit board with arbitrary layers interconnected, comprising the following steps,

[0040] Step 1. Material selection: a double-sided copper-clad laminate, including a dielectric layer with a thickness of 75 μm, an upper copper foil arranged on the top surface of the dielectric layer, and a lower copper foil arranged on the bottom surface of the dielectric layer. The thickness of the upper copper foil is 12μm, the thickness of the lower copper foil is 18μm;

[0041] Step 2. Copper reduction: use a horizontal copper reduction wire to etch the double-sided copper clad laminate in step 1 to reduce the thickness of 3 μm copper. The composition is: concentrated sulfuric acid 4%, hydrogen peroxide 2%, CRICUETCH100 3%, the rest is deionized water, the operating temperature is 30°C, the thickness of the upper copper foil becomes 9 μm after copper reduction, and the thickness of the lower copper foil b...

Embodiment 2

[0053] refer to figure 1 , a method for processing a core layer of a high-density circuit board with arbitrary layers interconnected, comprising the following steps,

[0054] Step 1. Material selection: a double-sided copper-clad laminate, including a dielectric layer with a thickness of 75 μm, an upper copper foil arranged on the top surface of the dielectric layer, and a lower copper foil arranged on the bottom surface of the dielectric layer. The thickness of the upper copper foil is 12μm, the thickness of the lower copper foil is 18μm;

[0055] Step 2. Copper reduction: use a horizontal copper reduction wire to etch the double-sided copper clad laminate in step 1 to reduce the thickness of 3 μm copper. The composition is: 5% concentrated sulfuric acid, 3% hydrogen peroxide, 3% CRICUETCH100, and the rest is deionized water. The operating temperature is 35°C. After copper reduction, the thickness of the upper copper foil becomes 9 μm, and the thickness of the lower copper f...

Embodiment 3

[0067] refer to figure 1 , a method for processing a core layer of a high-density circuit board with arbitrary layers interconnected, comprising the following steps,

[0068] Step 1. Material selection: a double-sided copper-clad laminate, including a dielectric layer with a thickness of 75 μm, an upper copper foil arranged on the top surface of the dielectric layer, and a lower copper foil arranged on the bottom surface of the dielectric layer. The thickness of the upper copper foil is 12μm, the thickness of the lower copper foil is 18μm;

[0069] Step 2. Copper reduction: use a horizontal copper reduction wire to etch the double-sided copper clad laminate in step 1 to reduce the thickness of 3 μm copper. The composition is: 7% concentrated sulfuric acid, 5% hydrogen peroxide, 3% CRICUETCH100, and the rest is deionized water. The operating temperature is 40°C. After copper reduction, the thickness of the upper copper foil becomes 9 μm, and the thickness of the lower copper f...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More