Two-dimensional ferroelectric semiconductor channel ferroelectric dielectric layer field effect transistor and preparation method thereof

A technology of field effect transistors and semiconductors, applied in the field of effect transistors, can solve problems such as incompatibility with silicon-based semiconductor manufacturing processes, difficulty in achieving stable non-volatile storage, and prolonging the remnant polarization of ferroelectrics, achieving good application prospects and improving Device stability, the effect of reducing remanent polarization loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

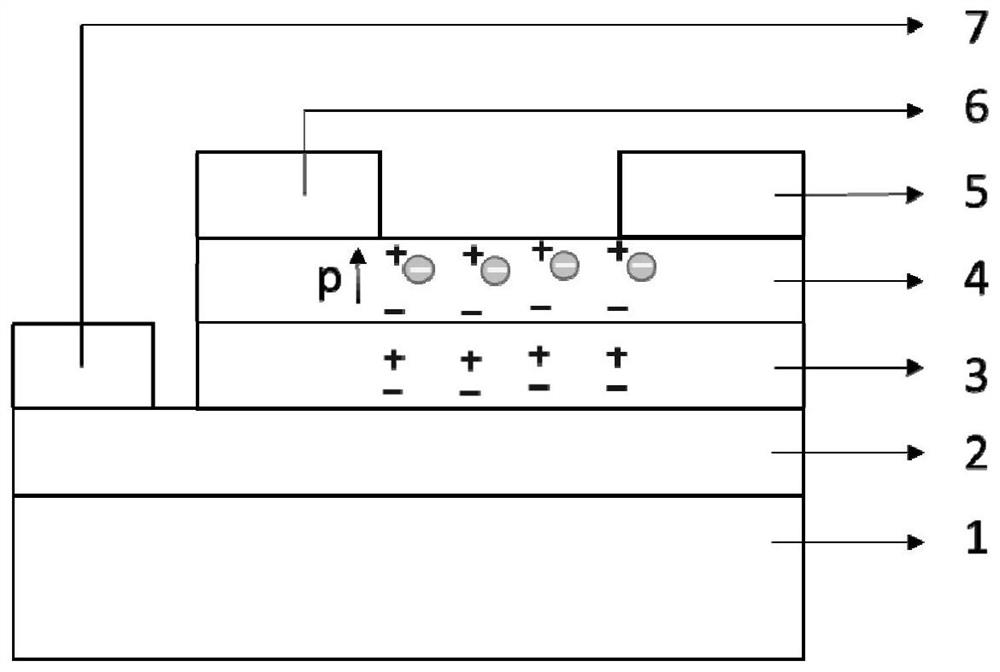

[0028] A two-dimensional ferroelectric semiconductor channel ferroelectric layer effect tube, including an insulating substrate 1, a graphene gate 2, a graphene gate 2, respectively, a graphene gate 2, respectively, a two-dimensional ferroelectric The dielectric layer 3 and the metal gate 7 are provided with a two-dimensional ferroelectric semiconductor channel 4, and a two-dimensional ferric semiconductor channel 4 is provided on a two-dimensional ferroelectric semiconductor channel 4 respectively disposed a metal source 5 and a metal source 5. Metal drain 6, the metal source 5 is disposed on the right side of the metal drain 6, and the ferrous ferroelectric layer 3 and the two-dimensional ferroelectric semiconductor channel 4 are both positive.

[0029] Among them, the insulating substrate is a silica having a thickness of 285 nm; the graphene gate thickness is a single layer. The two-dimensional ferroelectric layer is made of copper indium phosphate sulfur, and the two-dimensio...

Embodiment 2

[0035] A two-dimensional ferroelectric semiconductor channel ferroelectric layer effect tube, including an insulating substrate 1, a graphene gate 2, a graphene gate 2, respectively, a graphene gate 2, respectively, a two-dimensional ferroelectric The dielectric layer 3 and the metal gate 7 are provided with a two-dimensional ferroelectric semiconductor channel 4, and a two-dimensional ferric semiconductor channel 4 is provided on a two-dimensional ferroelectric semiconductor channel 4 respectively disposed a metal source 5 and a metal source 5. Metal drain 6, the metal source 5 is disposed on the right side of the metal drain 6, and the ferrous ferroelectric layer 3 and the two-dimensional ferroelectric semiconductor channel 4 are both positive.

[0036] Among them, the insulating substrate is a silica having a thickness of 285 nm; the graphene gate thickness is a single layer. The two-dimensional ferrometer is made of copper indium phosphate sulfur, and the ferrous ferroelectric...

Embodiment 3

[0042] A two-dimensional ferroelectric semiconductor channel ferroelectric layer effect tube, including an insulating substrate 1, a graphene gate 2, a graphene gate 2, respectively, a graphene gate 2, respectively, a two-dimensional ferroelectric The dielectric layer 3 and the metal gate 7 are provided with a two-dimensional ferroelectric semiconductor channel 4, and a two-dimensional ferric semiconductor channel 4 is provided on a two-dimensional ferroelectric semiconductor channel 4 respectively disposed a metal source 5 and a metal source 5. Metal drain 6, the metal source 5 is disposed on the right side of the metal drain 6, and the ferrous ferroelectric layer 3 and the two-dimensional ferroelectric semiconductor channel 4 are both positive.

[0043] Wherein the insulating substrate is a silica having a thickness of 280 nm; the graphene gate thickness is 5 layers. The two-dimensional ferrotic layer is copper indium phosphate sulfur, and the ferrous ferroelectric semiconductor...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More