Manufacturing method of shield gate MOSFET device with up-down structure

A manufacturing method and shielding grid technology, which are applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of large capacitance area of shielding grid and control grid, reduced reliability of devices, and large input capacitance of devices, etc., to achieve Small overlap area, reduced capacitance, low cost effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] In order to make those skilled in the art more clearly understand the purpose, technical solutions and advantages of the present invention, the present invention will be further described below in conjunction with the accompanying drawings and embodiments.

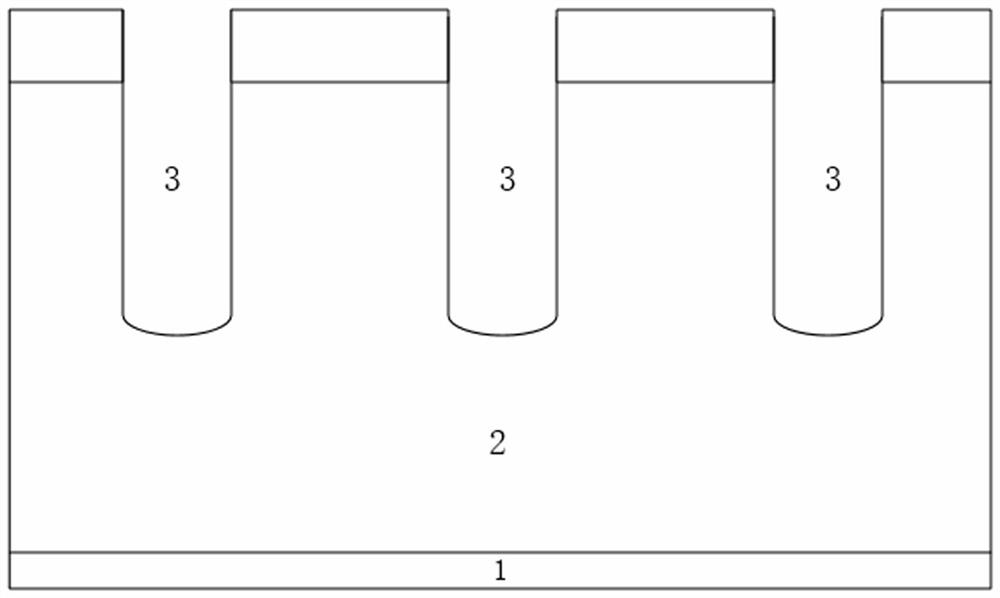

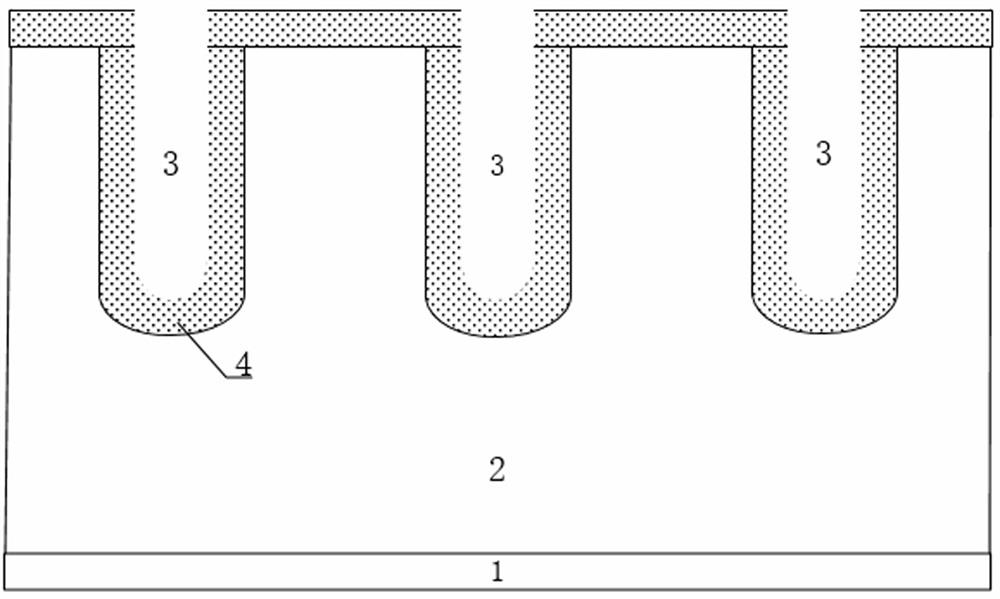

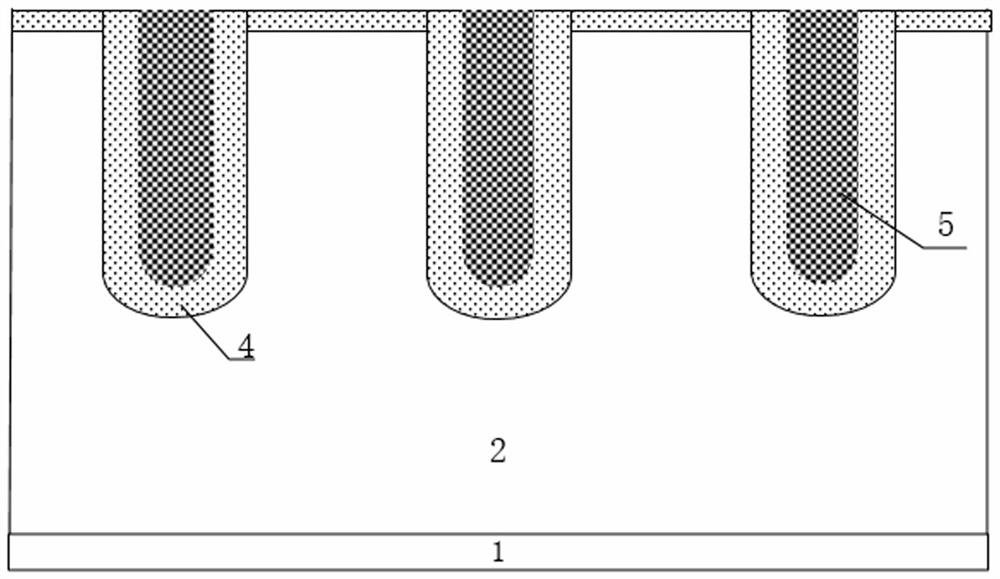

[0038] Such as Figure 1-10 As shown, the present invention proposes a method for manufacturing a shielded gate MOSFET device with a top and bottom structure, especially a relatively unique manufacturing method from the deposition of the shielded gate to the formation of the control gate. In the present invention, after the shield gate is filled and etched back to the silicon surface for the first time, a silicon nitride layer is deposited as a hard mask, and the silicon nitride layer is etched on the top of the trench in the primary cell area, and the field oxide layer is etched. , after performing the second polysilicon etching of the shielding gate, and then using a thermal oxidation process to grow an oxide laye...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More