Josephson junction meeting large wafer size, preparation method and application

A wafer-size, integrated technology, applied in the usage of superconductor elements, manufacturing/processing of superconductor devices, devices containing a node of different materials, etc., can solve the problem of increasing dielectric loss, dielectric loss, increasing loss, etc. problems, to achieve the effect of simple process steps, low dielectric loss, and high integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

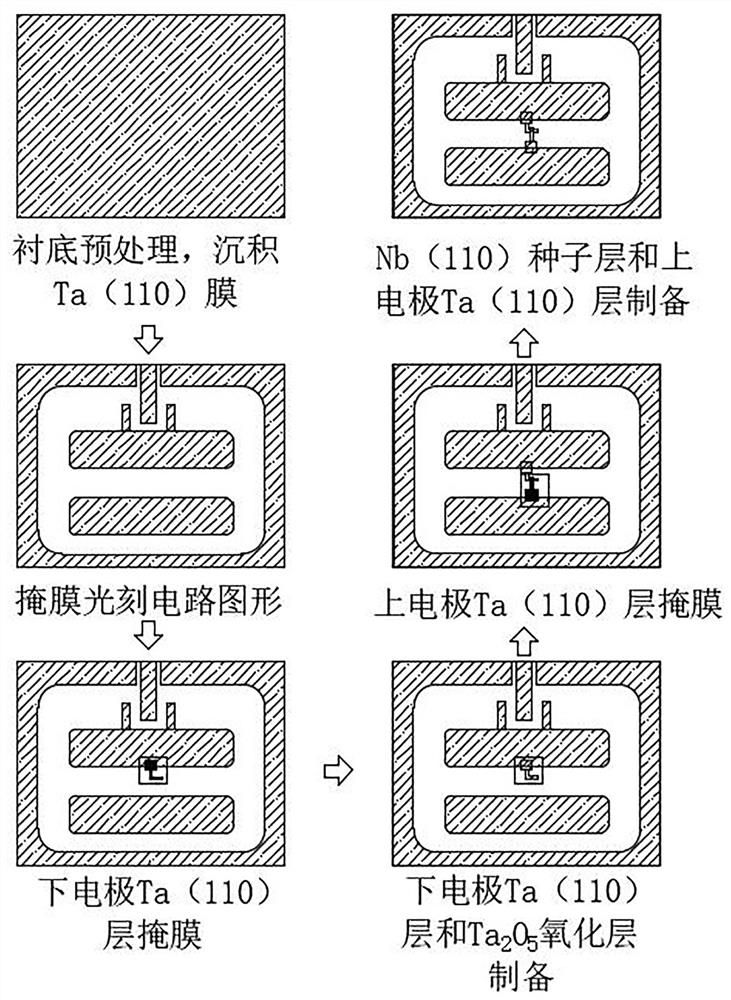

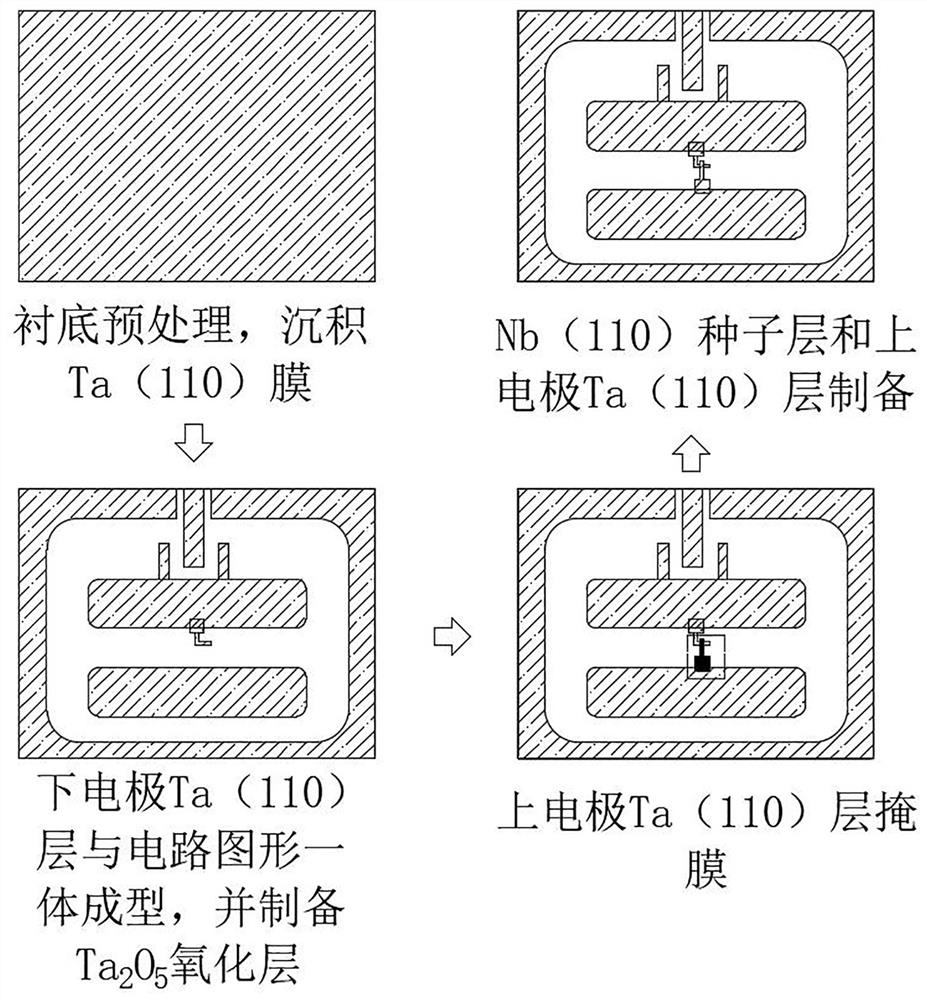

[0072] This embodiment provides a method for preparing a Josephson junction that meets the large wafer size. The lower electrode Ta (110) layer and the superconducting circuit pattern are formed step by step, such as figure 1 As shown, the preparation method specifically includes the following steps:

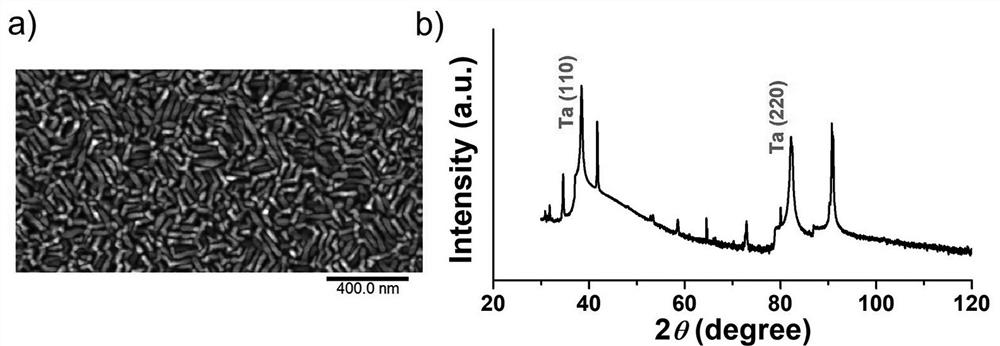

[0073] (I) Surface atomic step treatment, back pre-coating and active oxygen assisted surface cleaning are carried out on the substrate, Ta(110) film is deposited on the C-plane sapphire substrate, and superconducting circuit patterns are formed by photolithography. The Ta(110) film is made of Prepared by magnetron sputtering, the growth temperature is 500°C, the working pressure is 13mTorr, the DC power is 600W, the target base distance is 110mm, and the growth thickness is 100nm;

[0074] The lower electrode Ta (110) layer is prepared by mask photolithography in the overlapping area of the superconducting circuit pattern, and the lower electrode Ta (110) layer is prepared by...

Embodiment 2

[0079] This embodiment provides a method for preparing a Josephson junction meeting a large wafer size. The lower electrode Ta (110) layer and the superconducting circuit pattern are formed step by step. The preparation method specifically includes the following steps:

[0080](I) Surface atomic step treatment, back pre-coating and active oxygen assisted surface cleaning are carried out on the substrate, Ta(110) film is deposited on the C-plane sapphire substrate, and superconducting circuit patterns are formed by photolithography. The Ta(110) film is made of Prepared by magnetron sputtering, the growth temperature is 410°C, the working pressure is 5mTorr, the DC power is 400W, the target base distance is 70mm, and the growth thickness is 50nm;

[0081] The lower electrode Ta (110) layer is prepared by mask photolithography in the overlapping area of the superconducting circuit pattern, and the lower electrode Ta (110) layer is prepared by magnetron sputtering, including: fir...

Embodiment 3

[0086] This embodiment provides a method for preparing a Josephson junction meeting a large wafer size. The lower electrode Ta (110) layer and the superconducting circuit pattern are formed step by step. The preparation method specifically includes the following steps:

[0087] (I) Surface atomic step treatment, back pre-coating and active oxygen assisted surface cleaning are carried out on the substrate, Ta(110) film is deposited on the C-plane sapphire substrate, and superconducting circuit patterns are formed by photolithography. The Ta(110) film is made of Prepared by magnetron sputtering, the growth temperature is 600°C, the working pressure is 8mTorr, the DC power is 700W, the target base distance is 150mm, and the growth thickness is 150nm;

[0088] The lower electrode Ta (110) layer is prepared by mask photolithography in the overlapping area of the superconducting circuit pattern, and the lower electrode Ta (110) layer is prepared by magnetron sputtering, including: ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More