Automatic design method and device of superconducting quantum chip readout cavity and storage medium

A superconducting quantum, design method technology, applied in design optimization/simulation, configuration CAD, geometric CAD, etc., can solve problems such as increasing modeling time, errors, measurement errors, etc., to reduce design work, structure accuracy, and improve Modeling and Simulation Efficiency Effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment

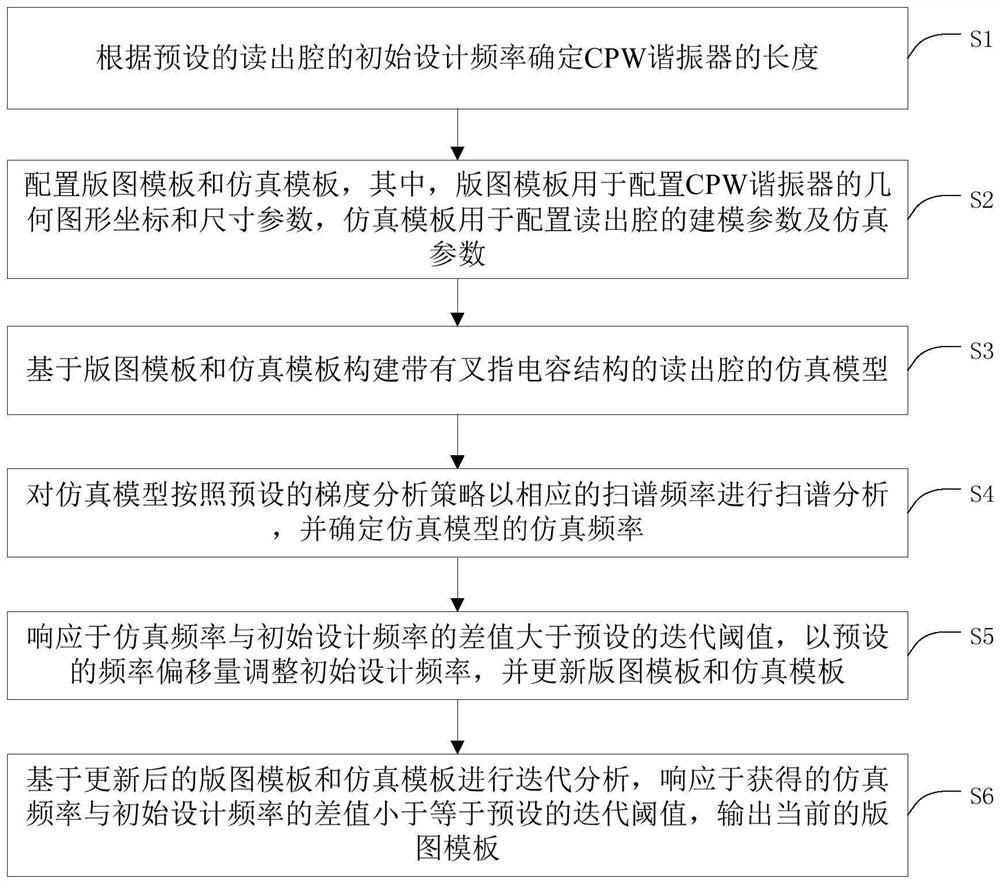

[0042] (1) Template preset

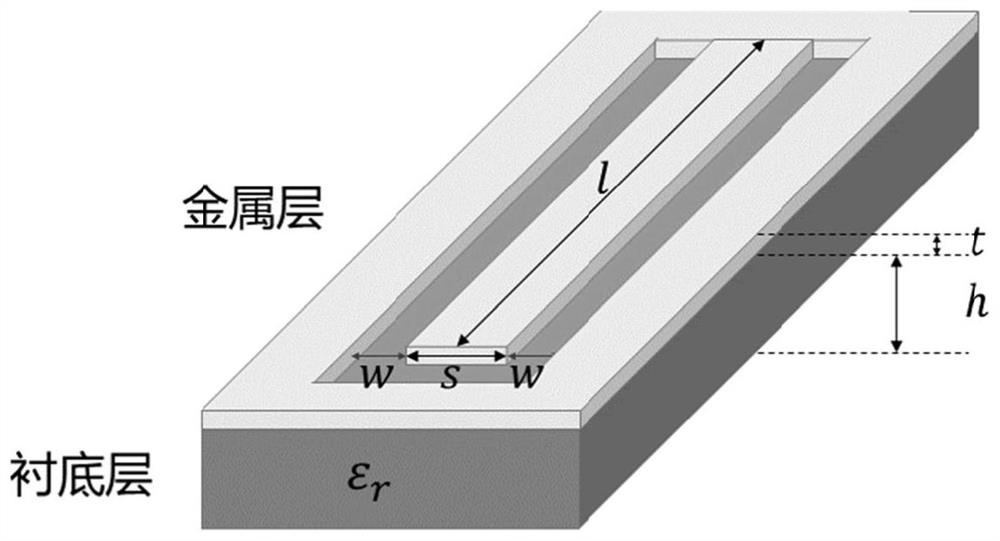

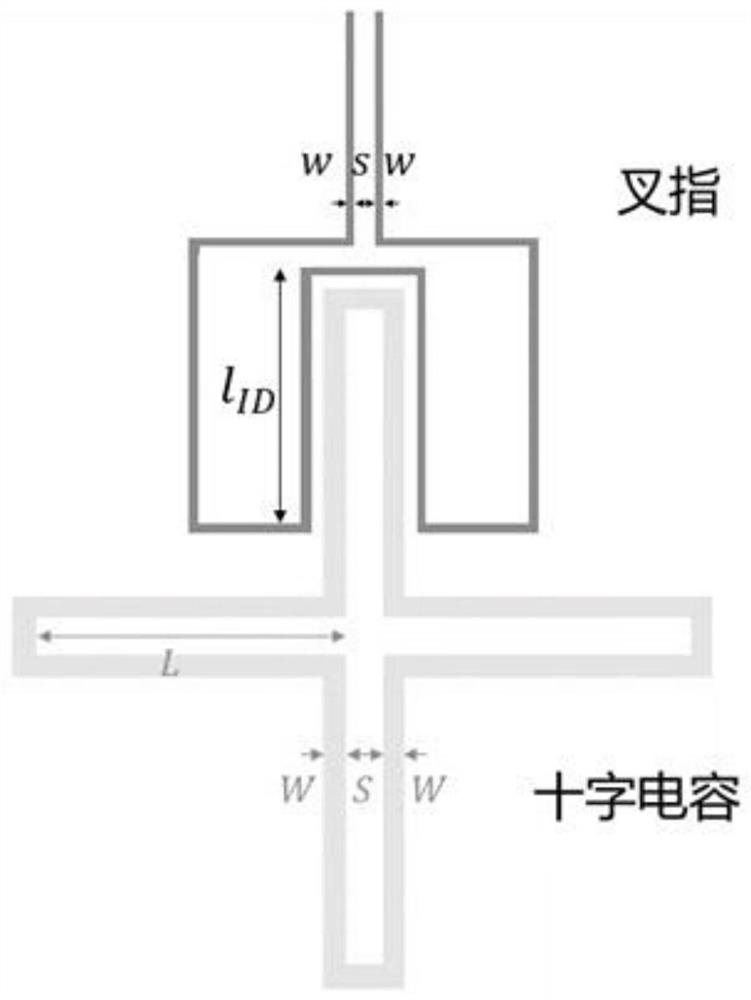

[0043] The template is divided into a layout template and a simulation template. The layout template is used to draw the layout of the readout cavity and extract the coordinates. The main function of the simulation template is to determine the substrate material of the readout cavity to be simulated, so as to determine the metal layer and substrate of the readout cavity. The dielectric constant between them, so as to determine the impedance of the readout cavity; and the coordinates extracted from the layout template are migrated to the simulation model for remodeling. Depending on the selected substrate, the layout template will form a sapphire layout template and a high-resistance silicon layout template, and the corresponding preset CPW center conductor width to ground width ratios satisfy impedance matching respectively (can be determined in the layout template according to the materials in the simulation template automatically generate the def...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More