Preparation process of deep submicron integrated circuit Cu barrier

An integrated circuit, deep sub-micron technology, applied in the manufacturing of circuits, electrical components, semiconductor/solid-state devices, etc., can solve the problems of poor film uniformity, asymmetric thickness of sidewall step coverage, etc., to improve hole filling and thickness uniformity. The effect of improving the resistance to Cu diffusion and improving the ability to resist F diffusion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

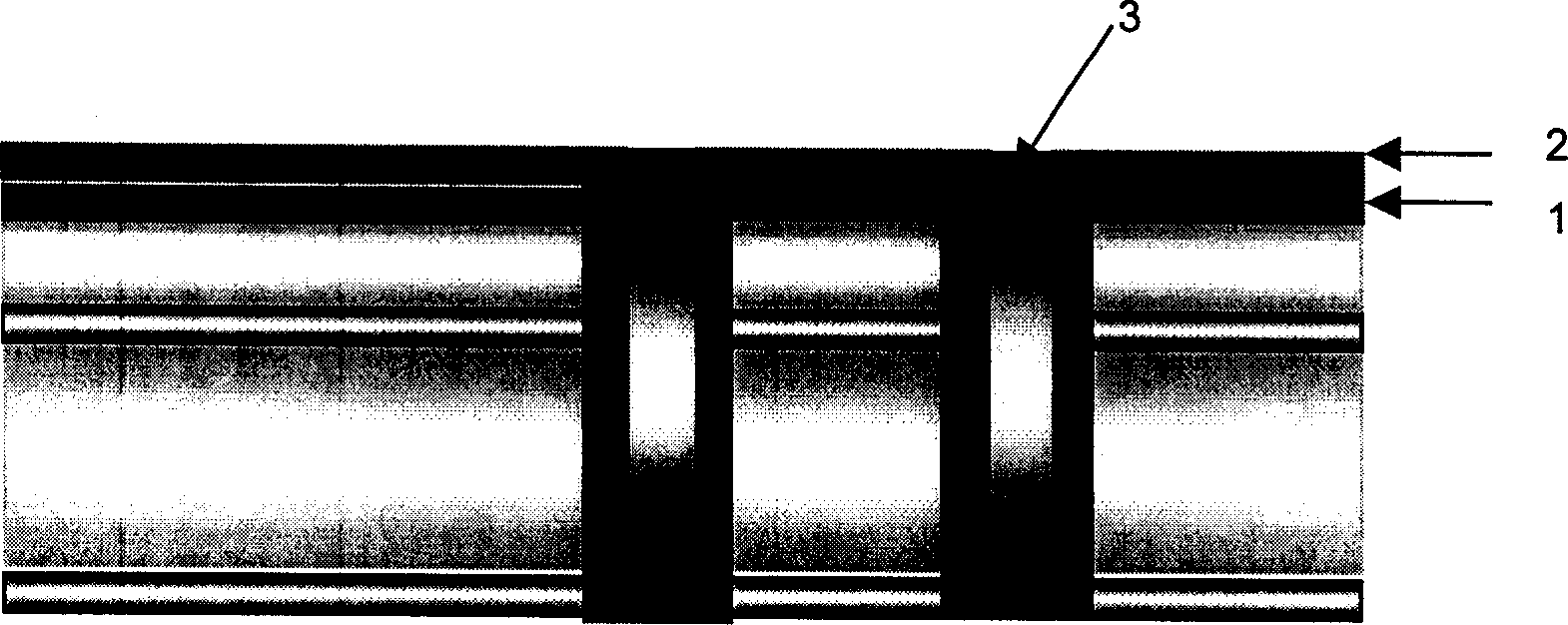

Image

Examples

Embodiment Construction

[0024] Below further describe the present invention by specific embodiment:

[0025] 1. Using multi-chamber ion physical deposition (IPVD) equipment, degas the silicon wafer under low vacuum conditions at a temperature of 350°C for 180 seconds to eliminate water vapor and other impurities on the surface;

[0026] 2. Use Ar 2 and H 2 The plasma pre-treats the surface of the silicon wafer to remove the natural oxide layer in the through hole and the residue left by the previous process. The preprocessing time is 20 seconds;

[0027] 3. Deposit a TaSiN barrier layer with a thickness of 30 nm by ion physics (IPVD) method;

[0028] 4. Deposit Ta on TaSiN by ion physics (IPVD) method, with a thickness of 20nm;

[0029] 5. Next, deposit a Cu seed layer with a thickness of 200nm by ion physics (IPVD) method;

[0030] 6. The silicon wafer with ion physical (IPVD) deposited Cu seed layer is sent into the Cu electroless plating tank, and a 1000nm Cu metal thin film is electroplated....

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More