Focus ring, plasma etching apparatus and plasma etching method

A plasma and etching device technology, applied in the field of focus rings, can solve unresolved problems, achieve the effects of suppressing the reduction of etching rate, high in-plane uniformity, and improved uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

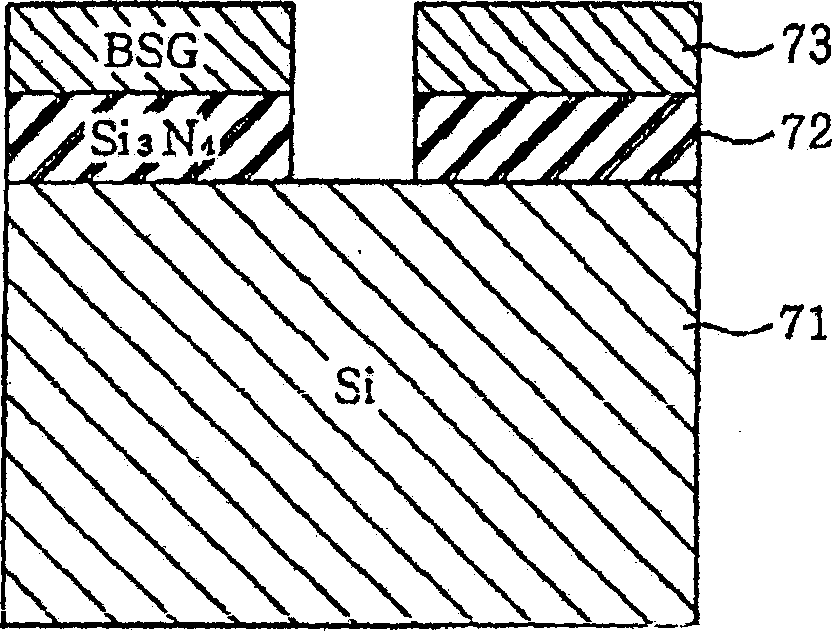

[0049] Next, in order to confirm the effect of this invention, the Example performed is demonstrated. For the focus ring 5 described in the above-mentioned embodiment, the whole surface is processed into a mirror surface, and the average surface roughness Ra is taken as 0.05, and it is installed on figure 1 In the plasma etching device, 1800 pieces with Figure 3A The wafer W on the surface portion shown was grooved individually, and the total etching treatment time was 30 hours. The focus ring 5 was taken out, and the surface was examined. As a result,

[0050] From the inner edge of the focus ring 5 to the area S0 radially outside 5 mm, the average surface roughness Ra is 0.8,

[0051] From the above-mentioned area S0 of the focus ring 5 to the area S1 of 32 mm outside, the average surface roughness Ra is 0.15,

[0052] From the above-mentioned area S1 of the focus ring 5 to an area S2 of 64 mm outside, the average surface roughness Ra was 0.36.

[0053] Figure 5A ~C i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More