Method for manufacturing thin film transistor array panel for liquid crystal display

a technology of thin film transistors and array panels, which is applied in the direction of identification means, instruments, optics, etc., can solve the problems of complex manufacturing process, difficult method implementation, and inability to stand up to physical and chemical variations,

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

fourth embodiment

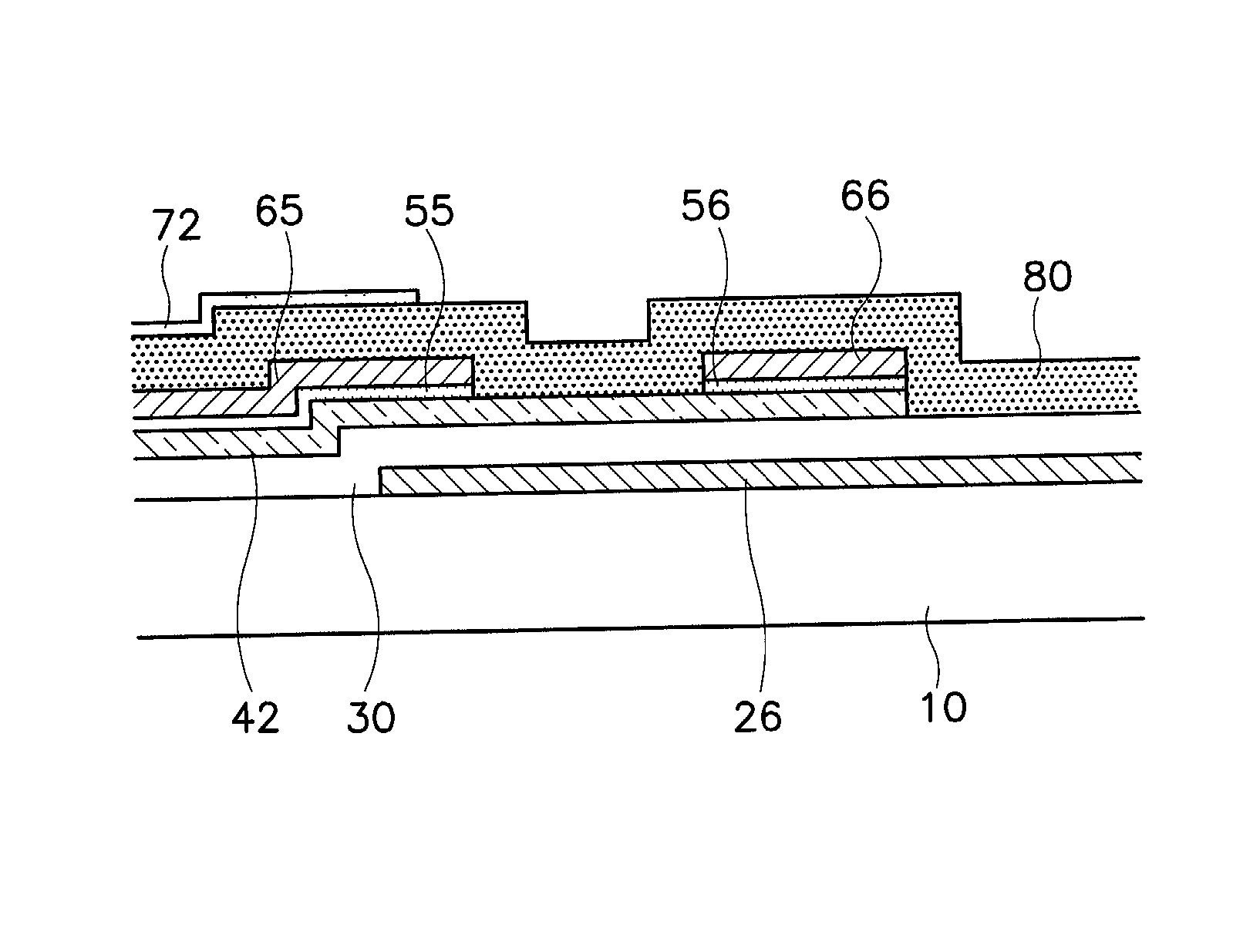

[0100] A passivation layer 80 made of insulating material such as SiNx is formed on the described structure, and has a plurality of openings 83, 84 and 85 respectively exposing the pixel electrode 71 and the third and the fourth pattern 73 and 74 of transparent conductor and openings 81 and 82 exposing the gate insulating layer 30. The openings 81 and 82 separate the semiconductor layer into two portions 42 and 47. It is to prevent a parasitic transistor of the gate line 22 as a gate, the date line 62 as a source and the pixel electrode 71 as a drain from being formed, as shown in FIG. 5. Since, in a previous gate type LCD like the present embodiment, where the pixel electrode 71 is overlapped with the previous gate line, such a parasitic transistor can cause a big problem. On the other hand, the semiconductor layer may form an electrical channel when voltages applied. The two adjacent data lines connected via a semiconductor layer may interfere the signals of the two data lines wit...

first embodiment

[0101] Now, a manufacturing method of a thin film transistor array panel according to the present invention will be described with reference to the FIGS. 6A to 8C and FIGS. 3 to 5 mentioned above.

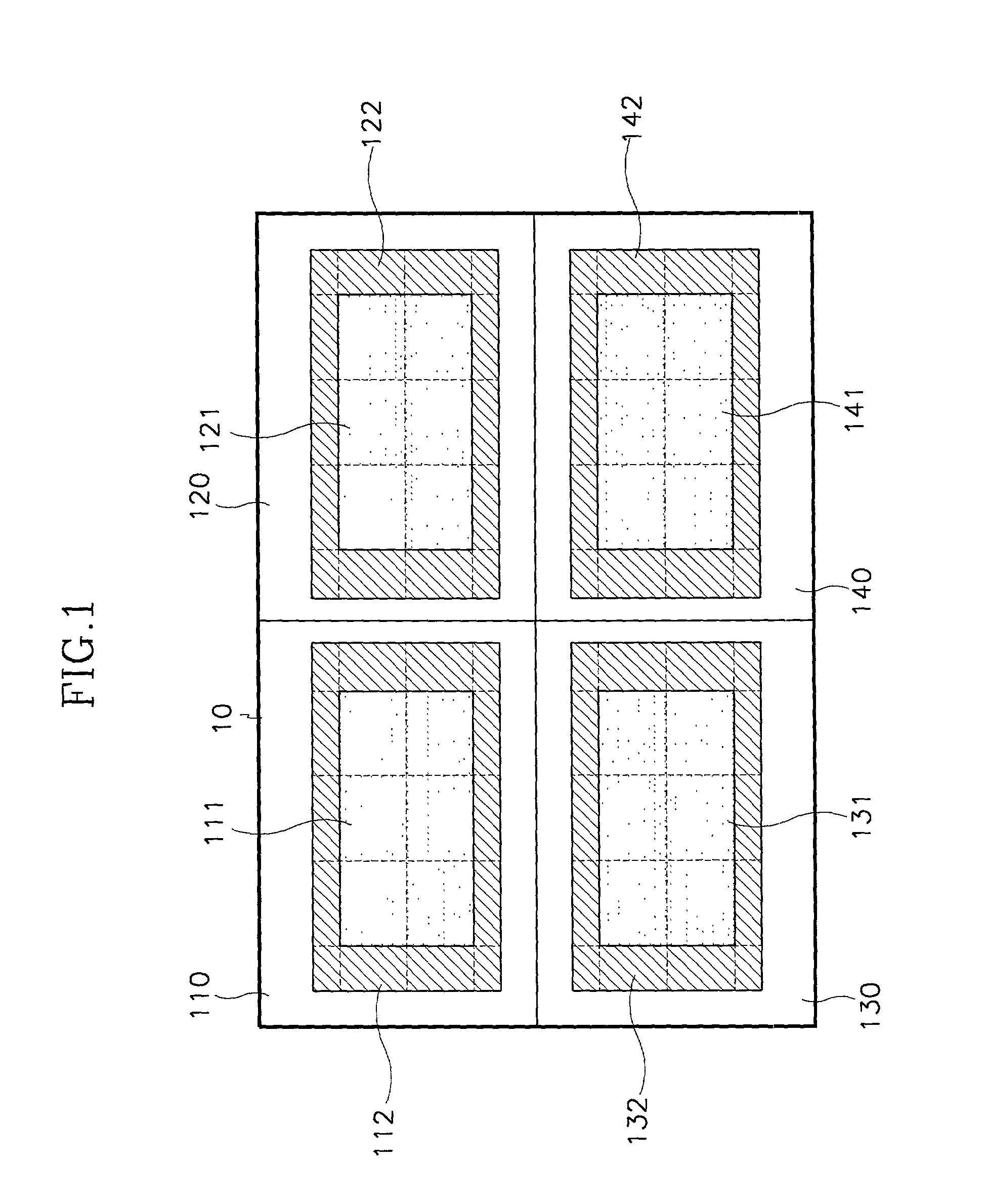

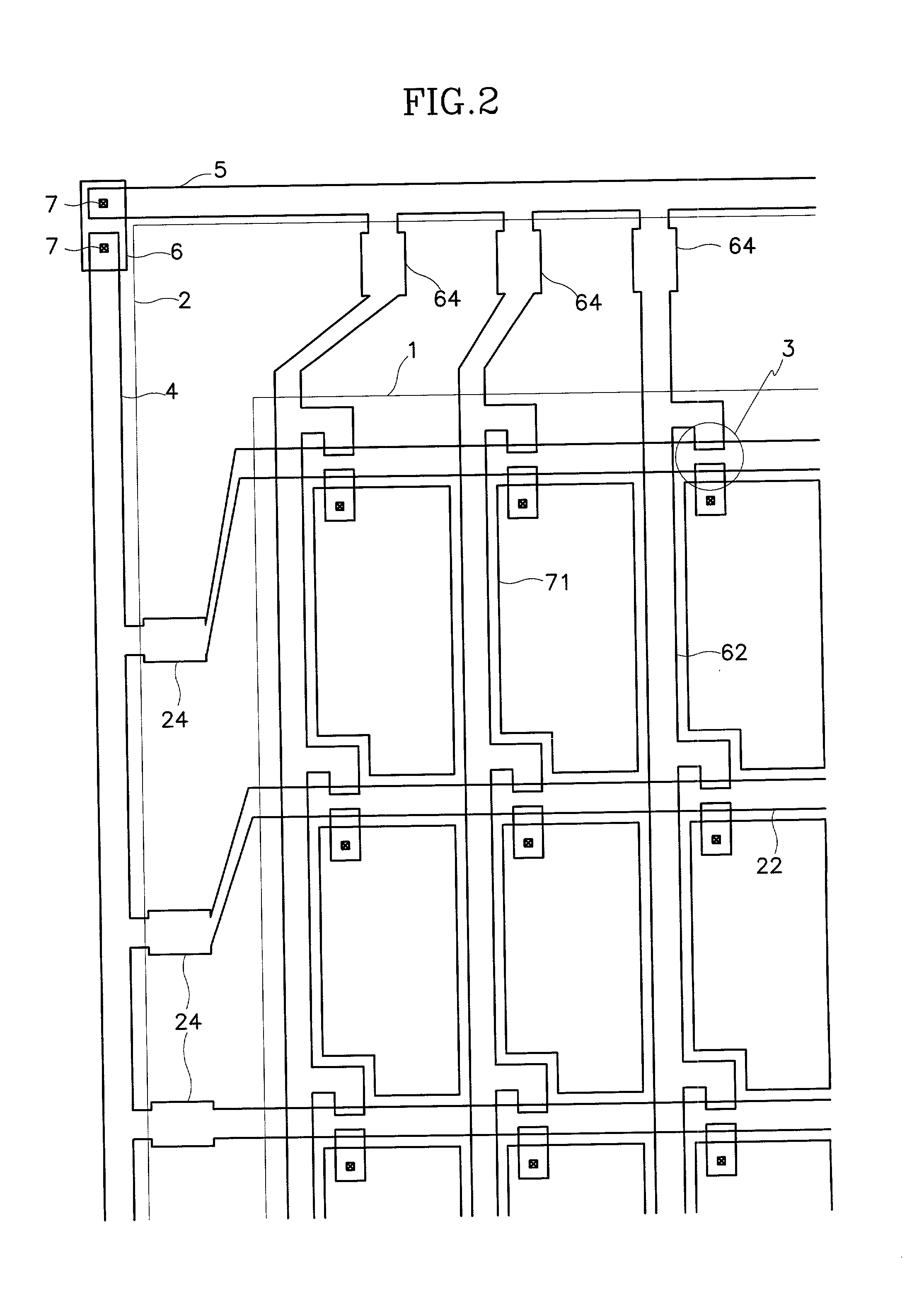

[0102] FIGS. 6A, 7A and 8A are layout views of a TFT panel and are sequentially arranged according to the manufacturing step of the first embodiment of the present invention. FIGS. 6B, 6C, 7B, 7C, 8B and 8C are respectively the cross-sectional views taken along the line VIB-VIB' and VIC-VIC' of the FIG. 6A, VIIB-VIIB' and VIIC-VIIC' of the FIG. 7A and VIIIB-VIIIB' and VIIIC-VIIIC' of the FIG. 8A.

[0103] At first, as shown in FIGS. 6A to 6C, a conductor layer is deposited on a substrate 10 by such methods as sputtering to have a thickness 1,000 .ANG. to 3,000 .ANG., and a gate wire including a gate line 22, a gate pad 24 and a gate electrode 26 is formed by dry etch or wet etch using the first mask. As described above, the gate wire 22, 24 and 26 may be formed of double layers of Al--Nd and M...

second embodiment

[0108] A TFT array panel and a manufacturing method thereof according to the present invention will be described.

[0109] FIG. 9 is a layout view of a TFT panel for an LCD according to the second embodiment of the present invention and an enlarged view of a portion mainly including a pixel and pads of the FIG. 2, and FIGS. 10 and 11 are cross-sectional views respectively taken along the line X-X' and XI-XI' of the FIG. 9.

[0110] As shown in FIGS. 9 to 11, the structure of the TFT array panel of the second embodiment is almost the same as that of the first embodiment except for that around the pads. That is to say, between the pads, the gate insulating layer 30 is removed in the first embodiment, but is not removed in the second embodiment. In addition, in the second embodiment, the passivation layer 80 has an opening 86 marked as slanted creases, exposing the gate insulating layer 30 between the pads. Therefore, the pads are not connected to each other through the semiconductor layer.

[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More