Method of manufacturing semiconductor device to decrease defect number of plating film

a technology of plating film and semiconductor, which is applied in the direction of semiconductor devices, basic electric elements, electrical appliances, etc., can solve the problems of reducing device features, reducing device performance, and narrowing of cu wiring width, so as to reduce the defect number of plated films after cmp, and reduce the defect number of films

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

[0040]Hereafter, an embodiment of the present invention will be described with referring to FIGS. 1 to 3.

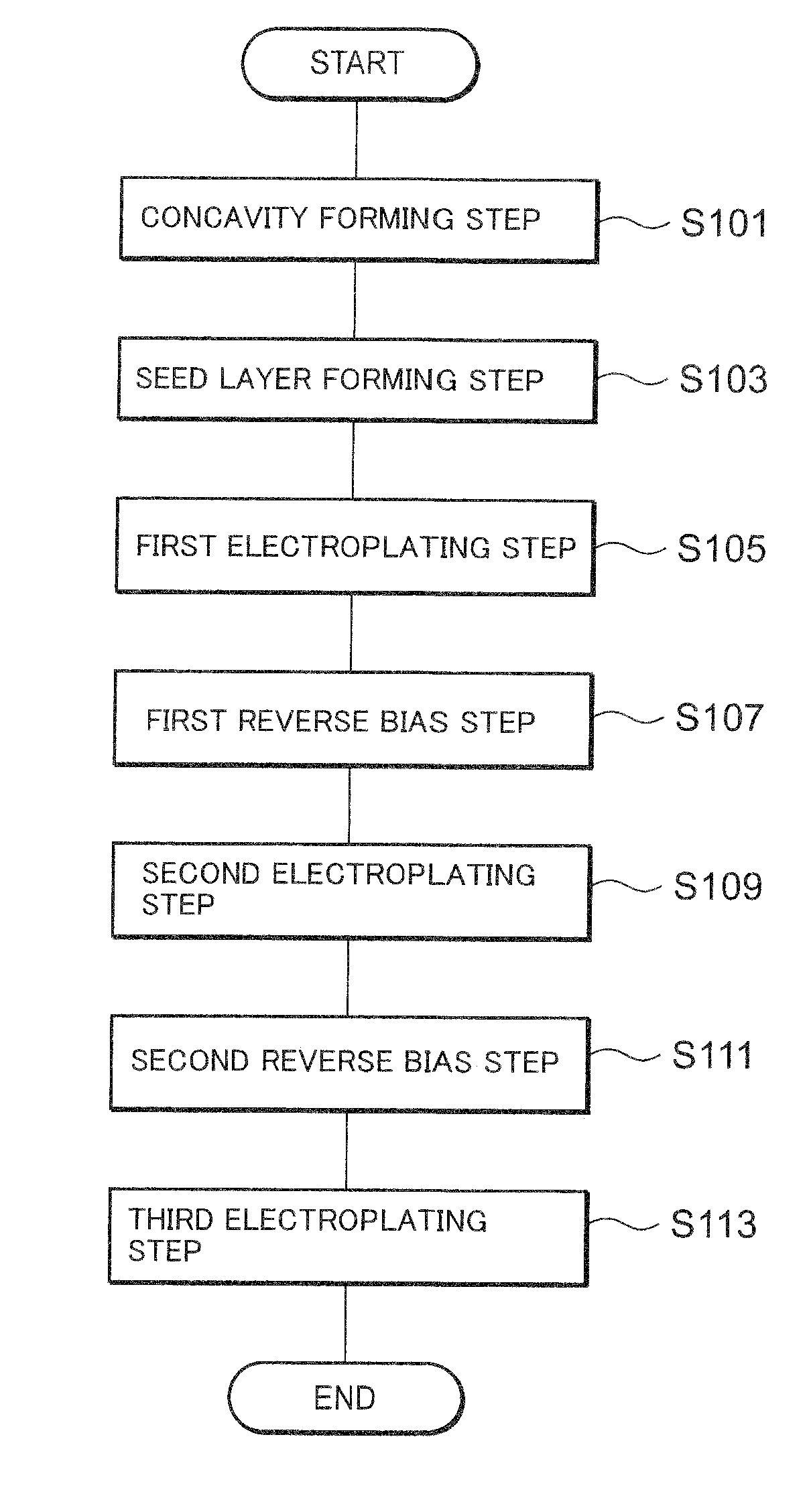

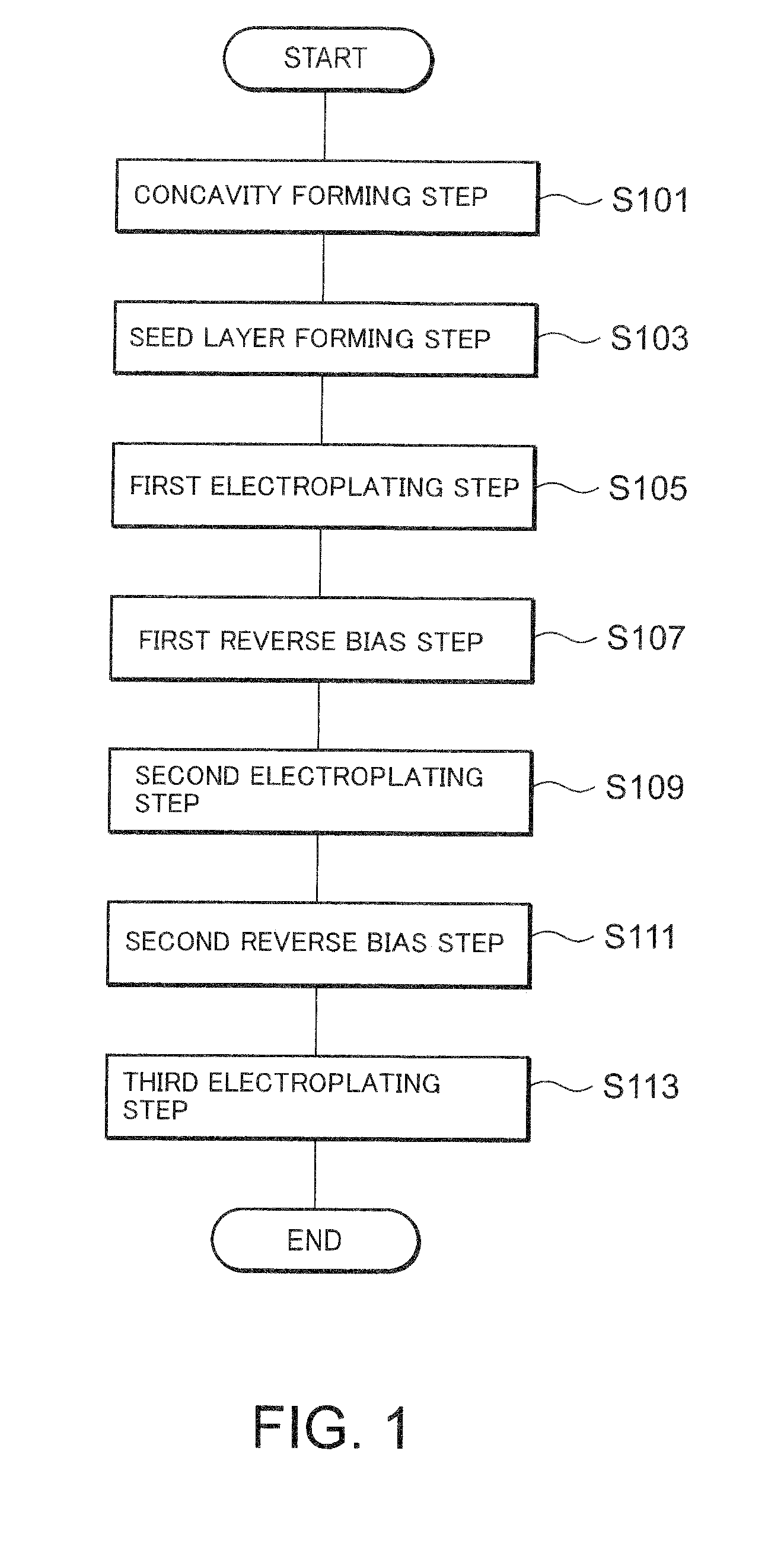

[0041]FIG. 1 is a flowchart for describing a method of manufacturing a semiconductor device in this embodiment. The method of manufacturing a semiconductor device in this embodiment has order of a concavity forming step (S101), a seed layer forming step (S103), a first electroplating step (S105), a first reverse bias step (S107), a second electroplating step (S109), a second reverse bias step (S111), and a third electroplating step (S113), and includes a series of these steps. In addition, a conceptual diagram of a current profile in each plating step is as illustrated in FIG. 3.

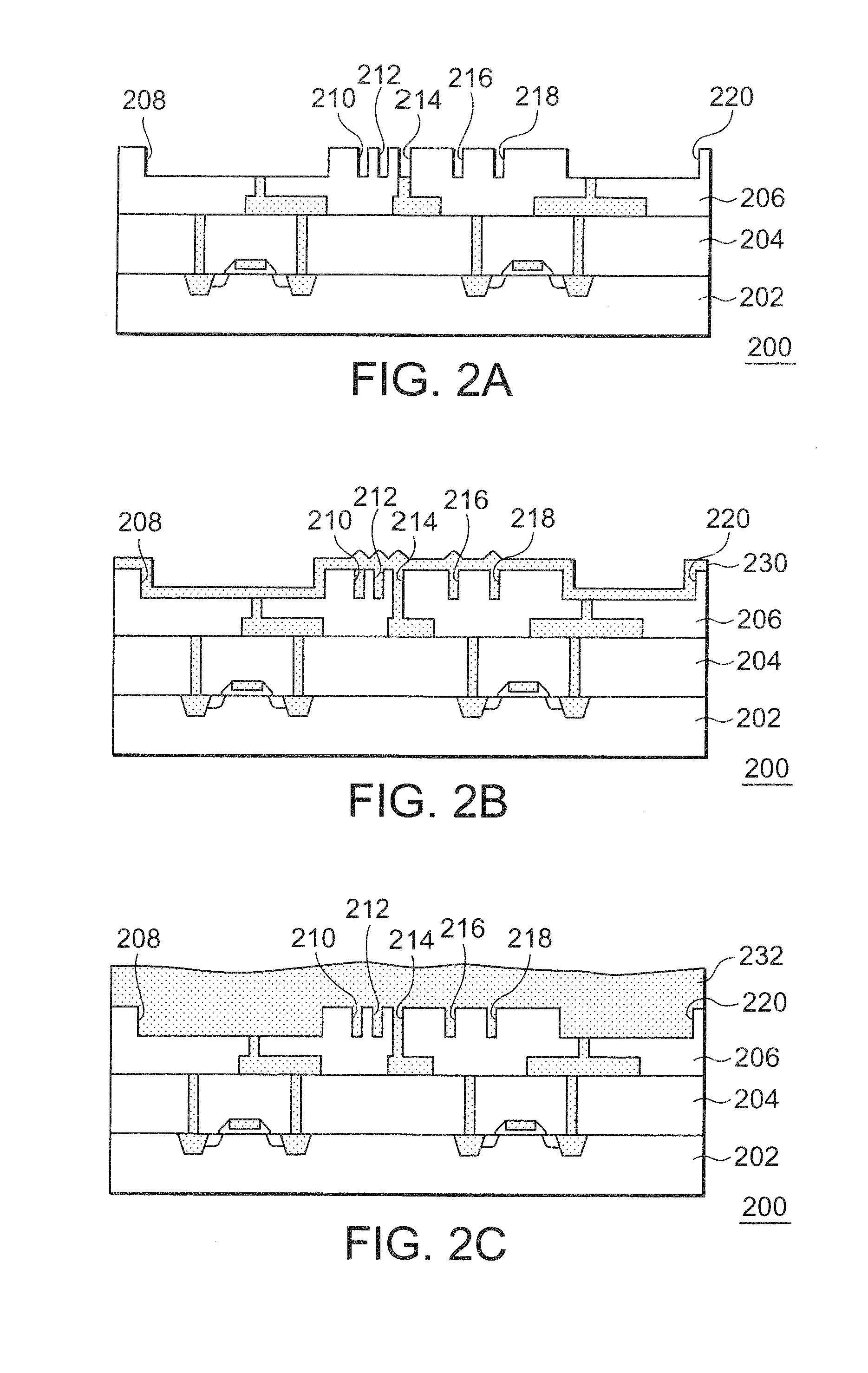

[0042]FIGS. 2A to 2C are step sectional views of illustrating steps of producing a semiconductor device 200 in this embodiment. In this embodiment, a step of forming wiring in an inter-layer insulating film 206 will be described. In FIG. 2, although procedure of forming copper wiring with taking a case of...

example 1

[0077]Cu electroplating was performed in a current profile (this is called a current profile C) illustrates in FIG. 4. In the current profile C, a first electroplating step of filling a fine pattern at a first current density (I1), a first reverse bias step of applying a current at the second current density (I2) after filling of the fine pattern is completed, a second electroplating step of using the third current density (I3), a second reverse bias step of applying a current at the same current density as the second current density (I2), and a third electroplating step of using the same current density as the third current density (I3) were performed successively.

[0078]Here, the first current density (I1) was set in a range of 0.2 A / dm2 to 1 A / dm2 inclusive. Here, in this specification, a current direction that goes to the cathode from an anode is defined as a positive direction. In addition, time of the first electroplating step was made 20 seconds to 200 seconds inclusive. The s...

second embodiment

[0085]A flowchart illustrating a method of manufacturing a semiconductor device in this embodiment and step sectional views expressing steps of producing the semiconductor device are the same as those of the first embodiment. However, it is different from the first embodiment at a point that an absolute value of an integrated current amount at a second reverse bias step is larger than an absolute value of an integrated current amount at a first reverse bias step. Thereby, the defect number in a plated film after a CMP step is further reduced. Hereinafter, this embodiment will be described with focusing on different points from the first embodiment.

[0086]FIG. 8 is a conceptual diagram illustrating a current profile in a plating step in this embodiment. A first electroplating step, a second electroplating step, and a third electroplating step are set as the same conditions as those in the first embodiment. Those preferable ranges are the same as those in the first embodiment. In this ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| current density | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More