Patents

Literature

85results about How to "Reduce defect formation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

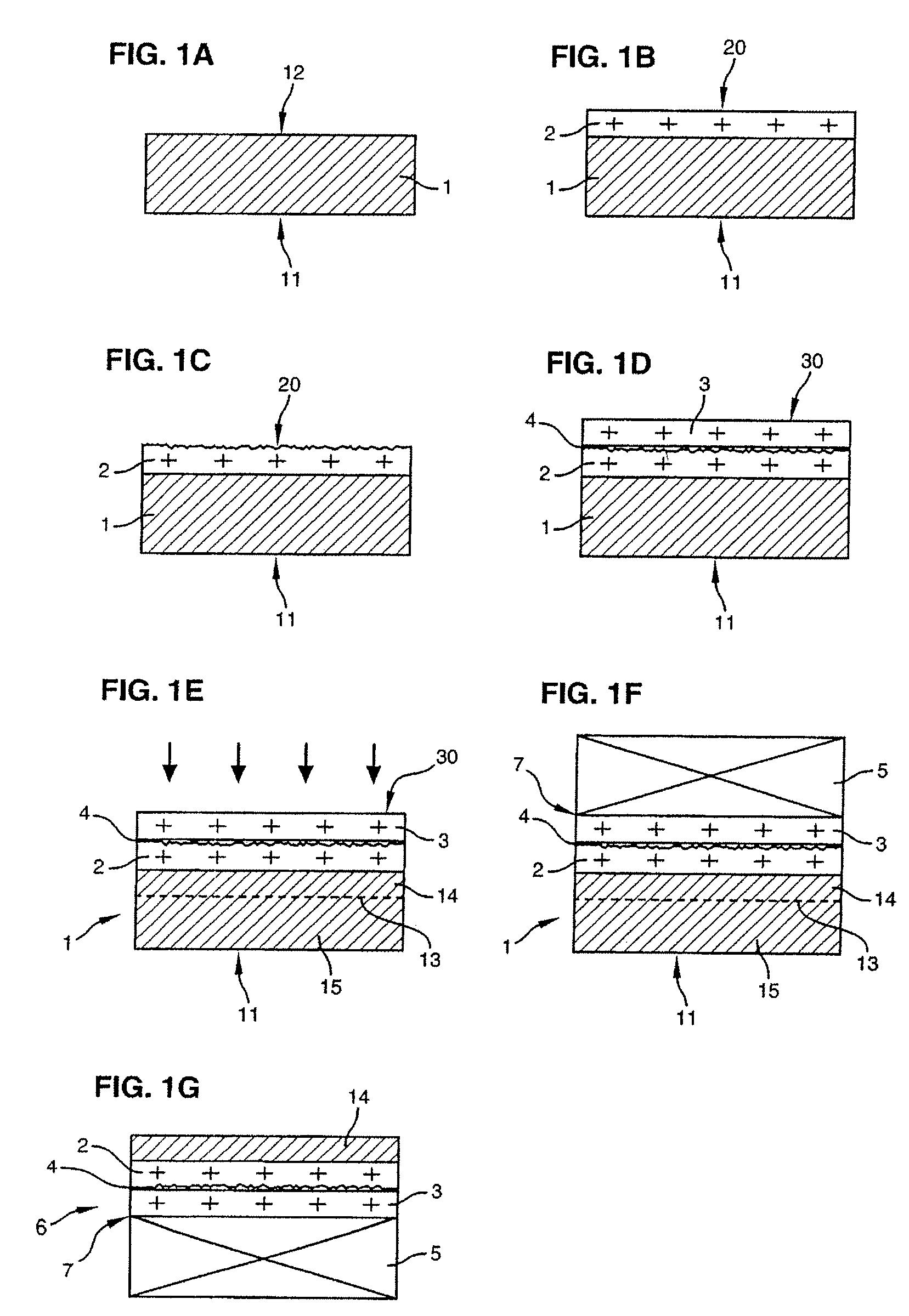

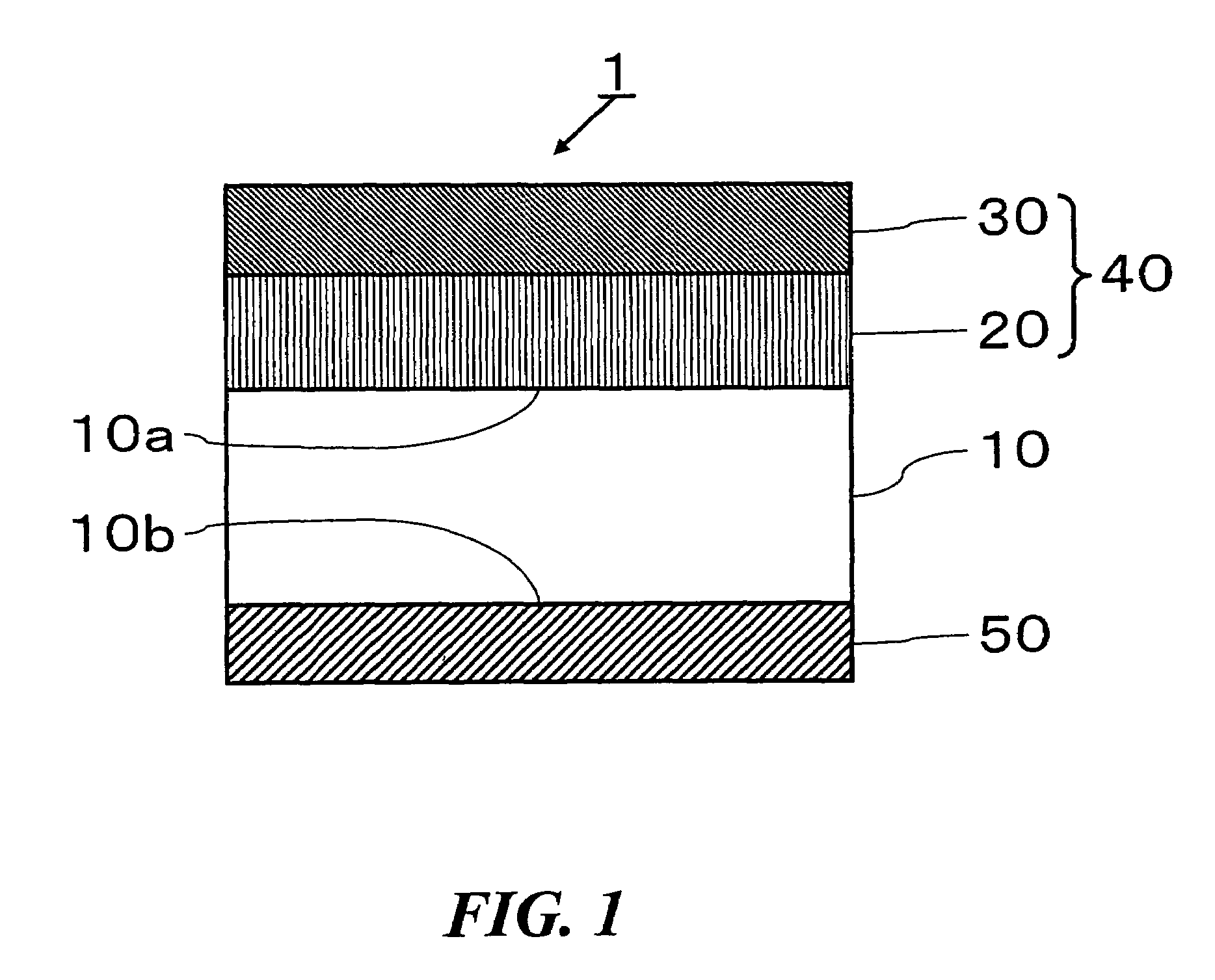

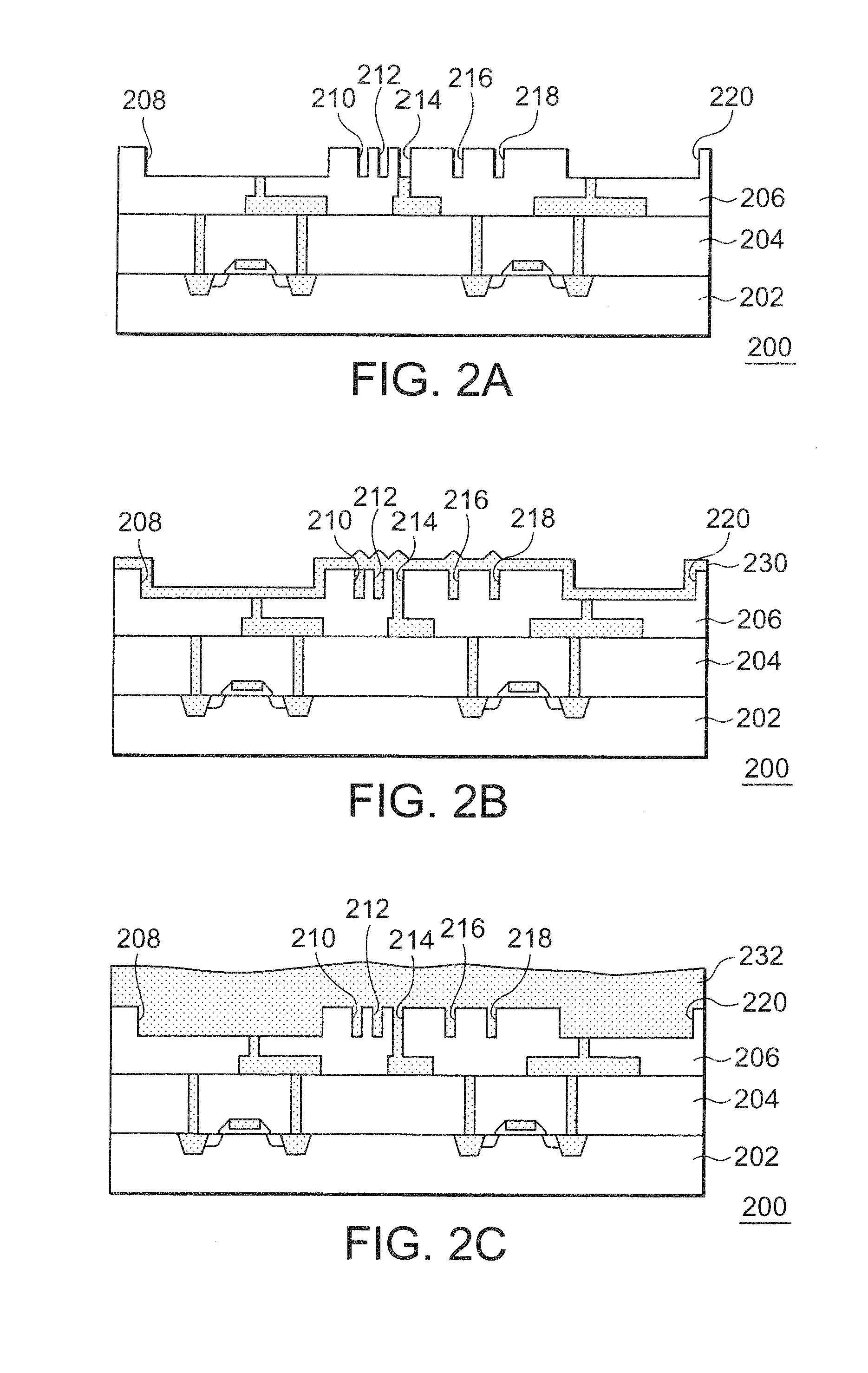

Fabrication of hybrid substrate with defect trapping zone

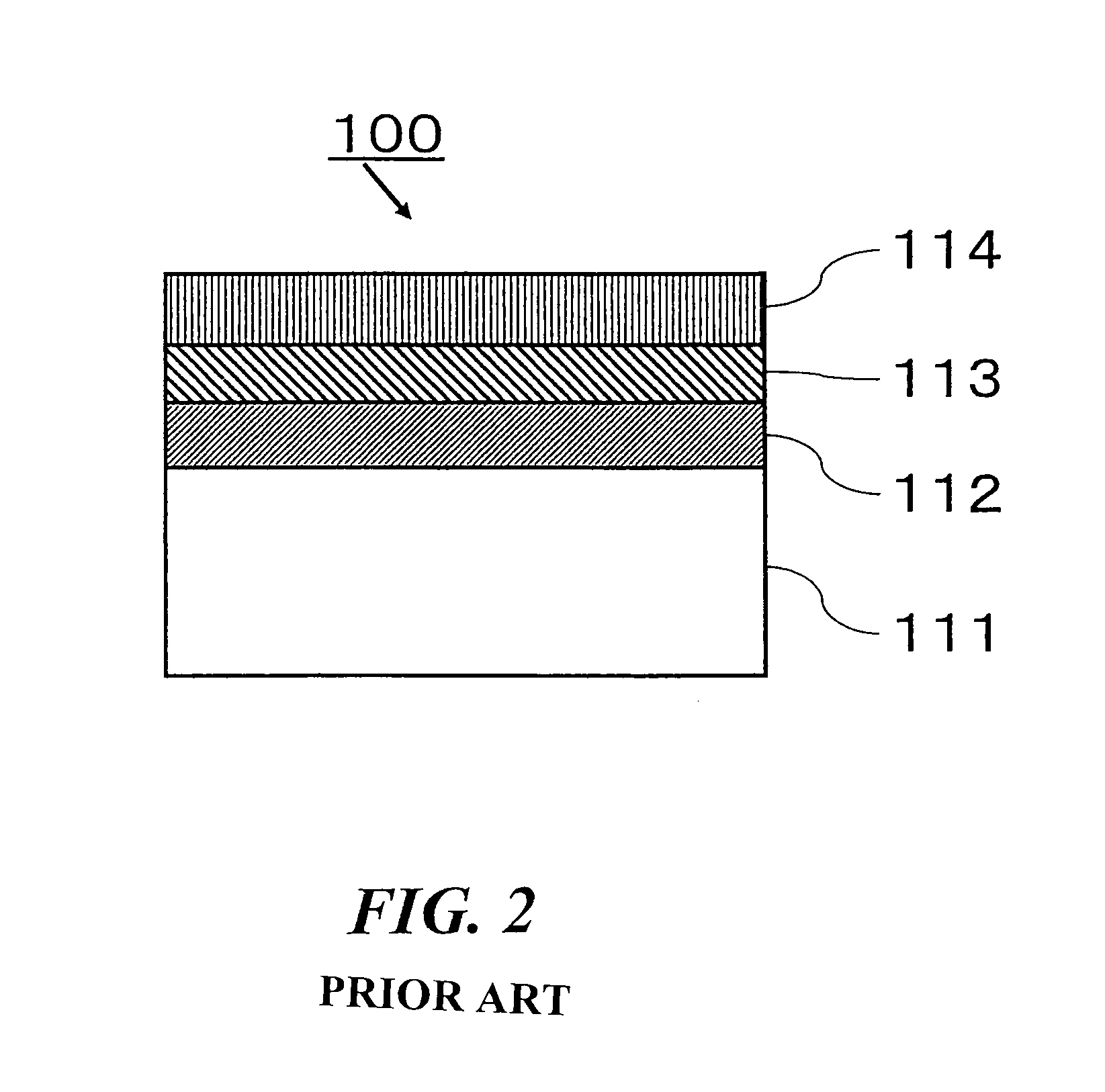

ActiveUS20080171443A1Inhibition formationReduce defect formationSemiconductor/solid-state device manufacturingSemiconductor materialsTrapping

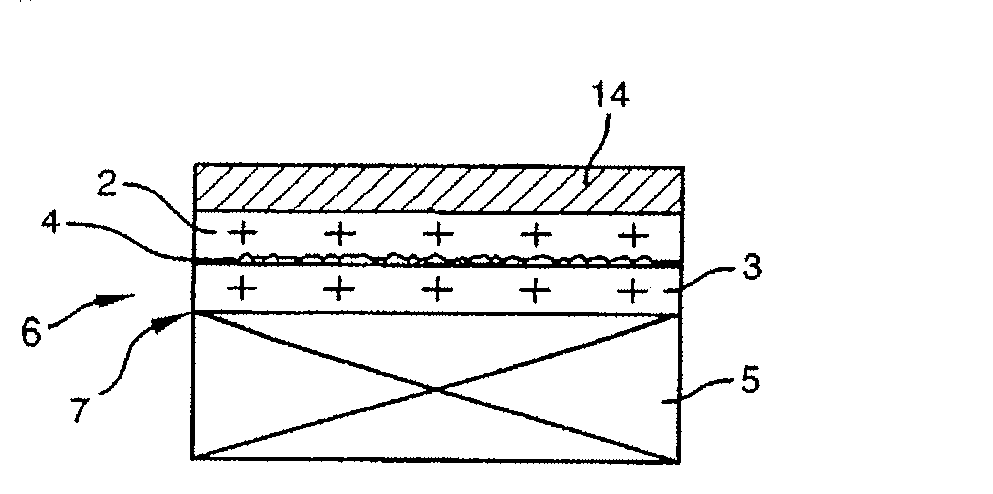

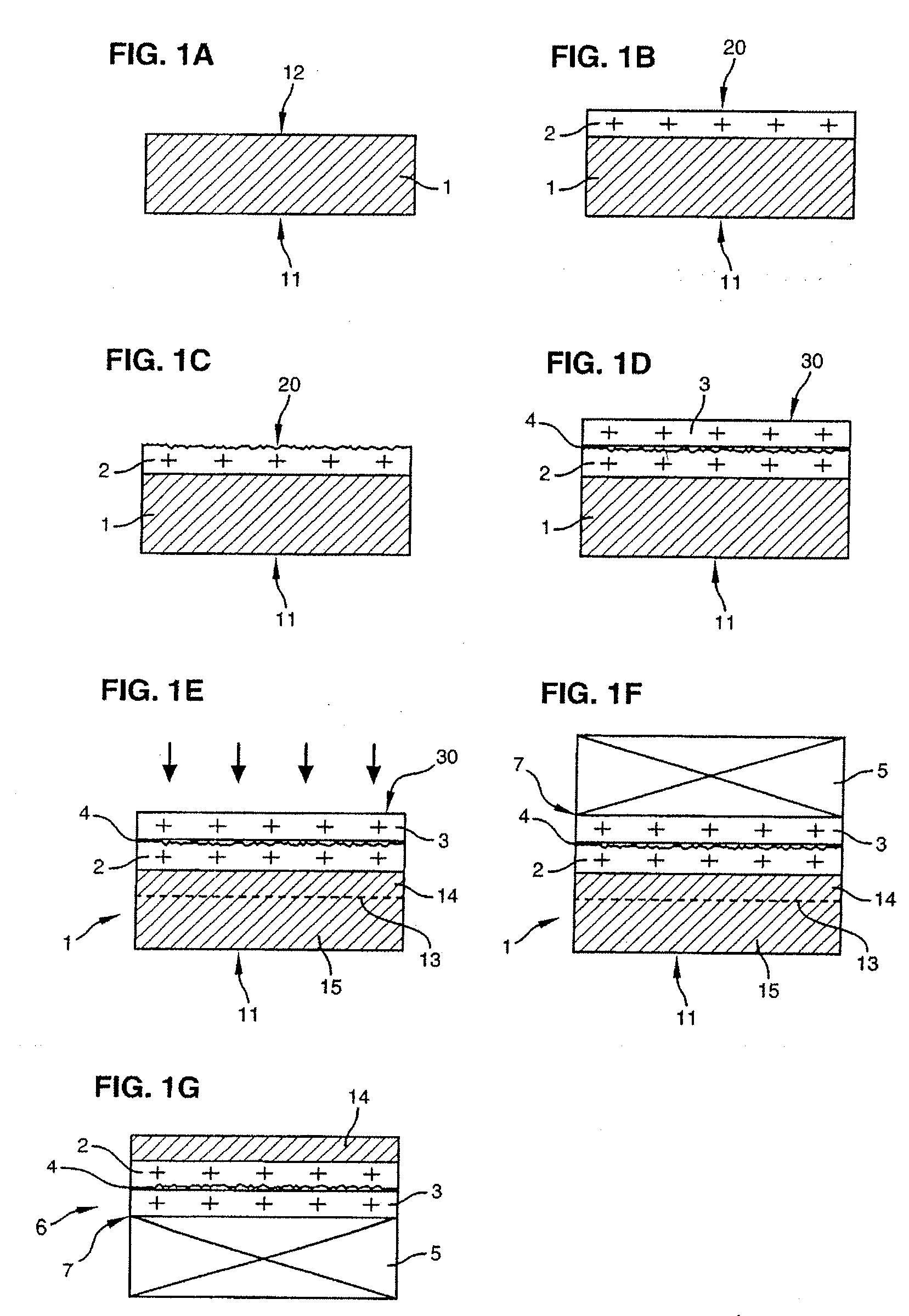

A process for fabricating a hybrid substrate that has a defect trapping zone. The process includes the steps of forming or depositing a first insulator layer on a first substrate of semiconductor material; increasing roughness of the first insulator layer surface; depositing a second insulator layer on the roughened surface of the first insulator to form a trapping zone between the layers; bonding a second substrate onto the second insulator layer by molecular adhesion; and transferring an active layer formed by the implantation of atomic species into one of the substrates. The trapping zone is able to retain gaseous species present at the various interfaces of the hybrid substrate to limit the formation of defects on the surface of the active layer that is transferred.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

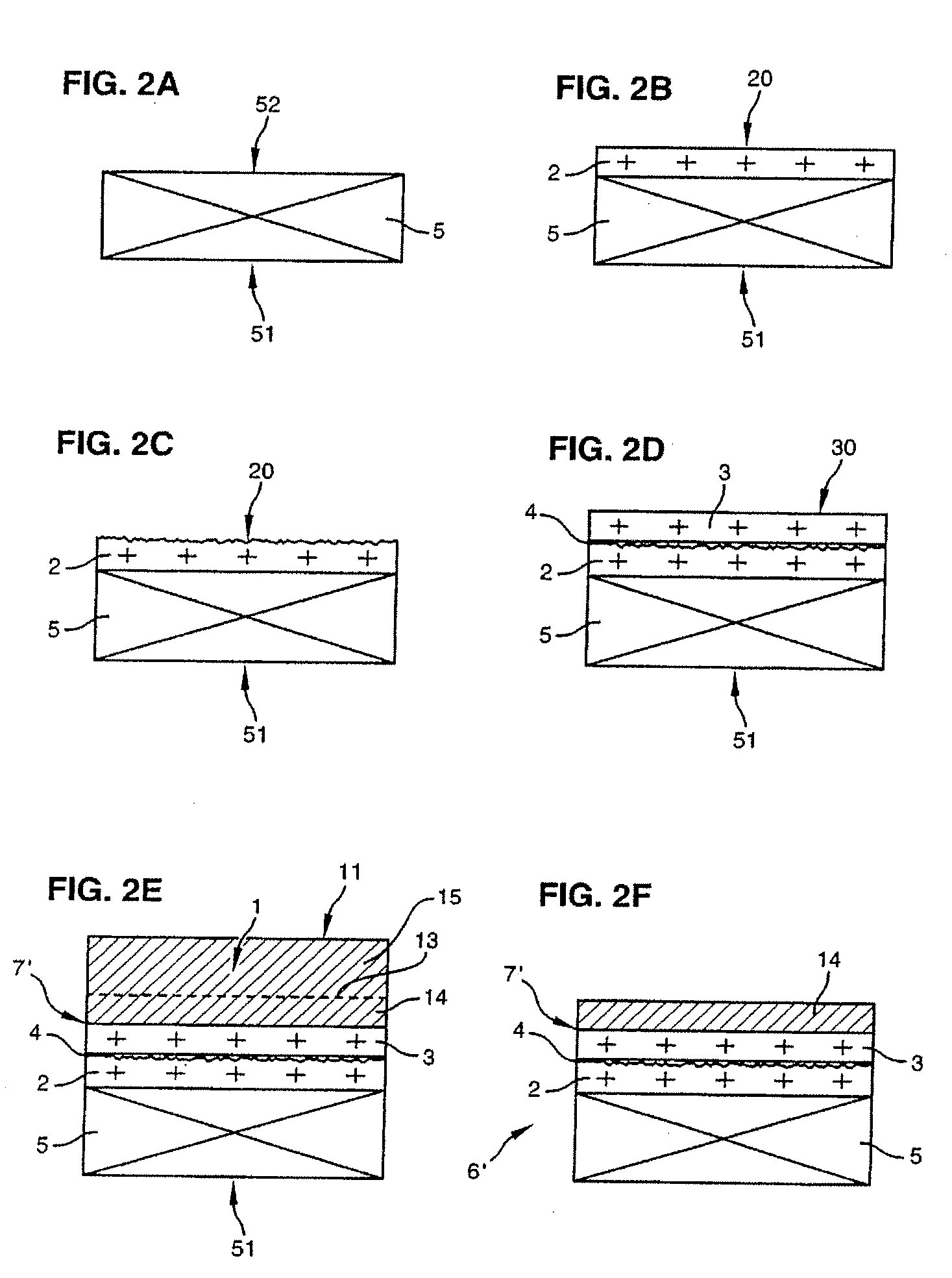

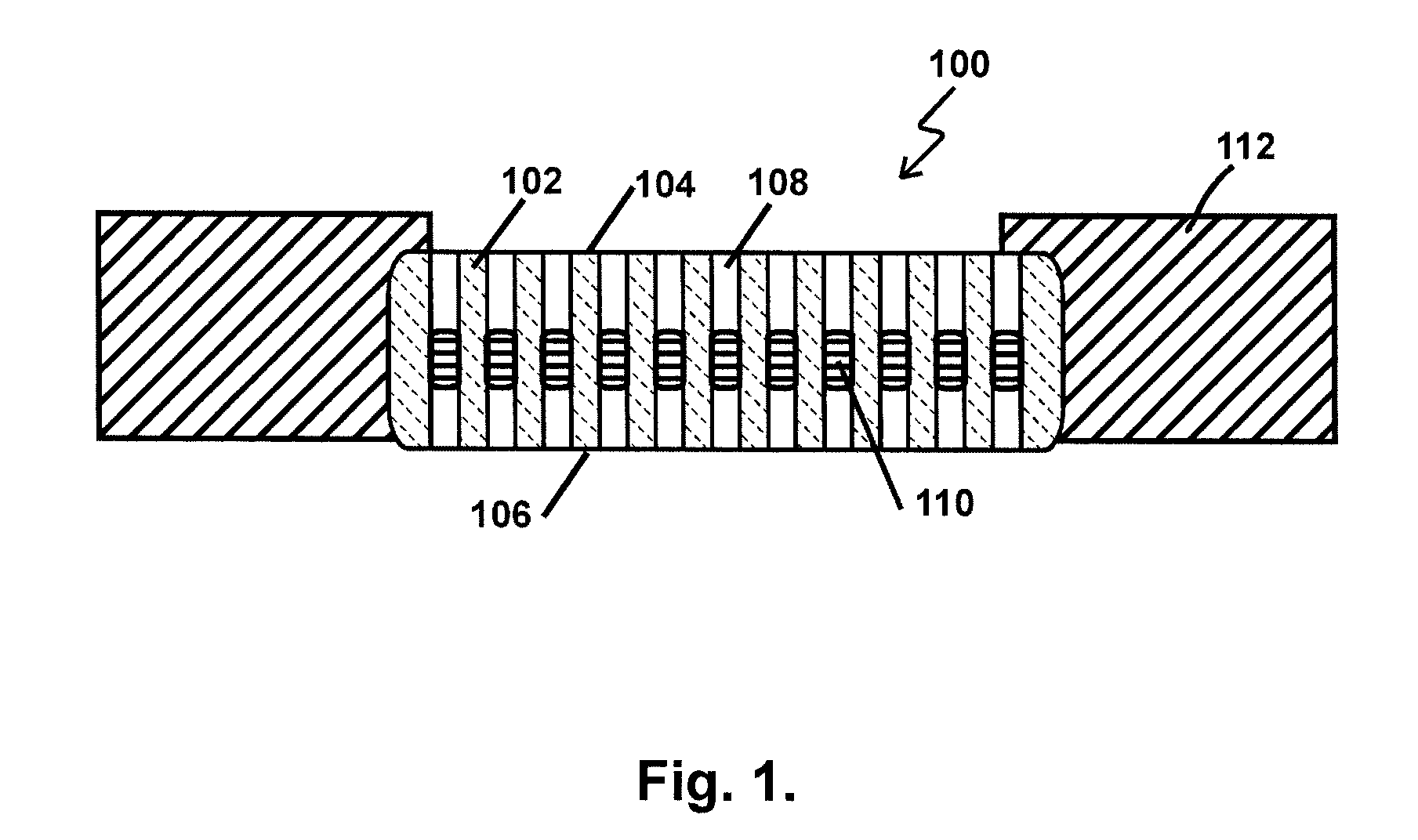

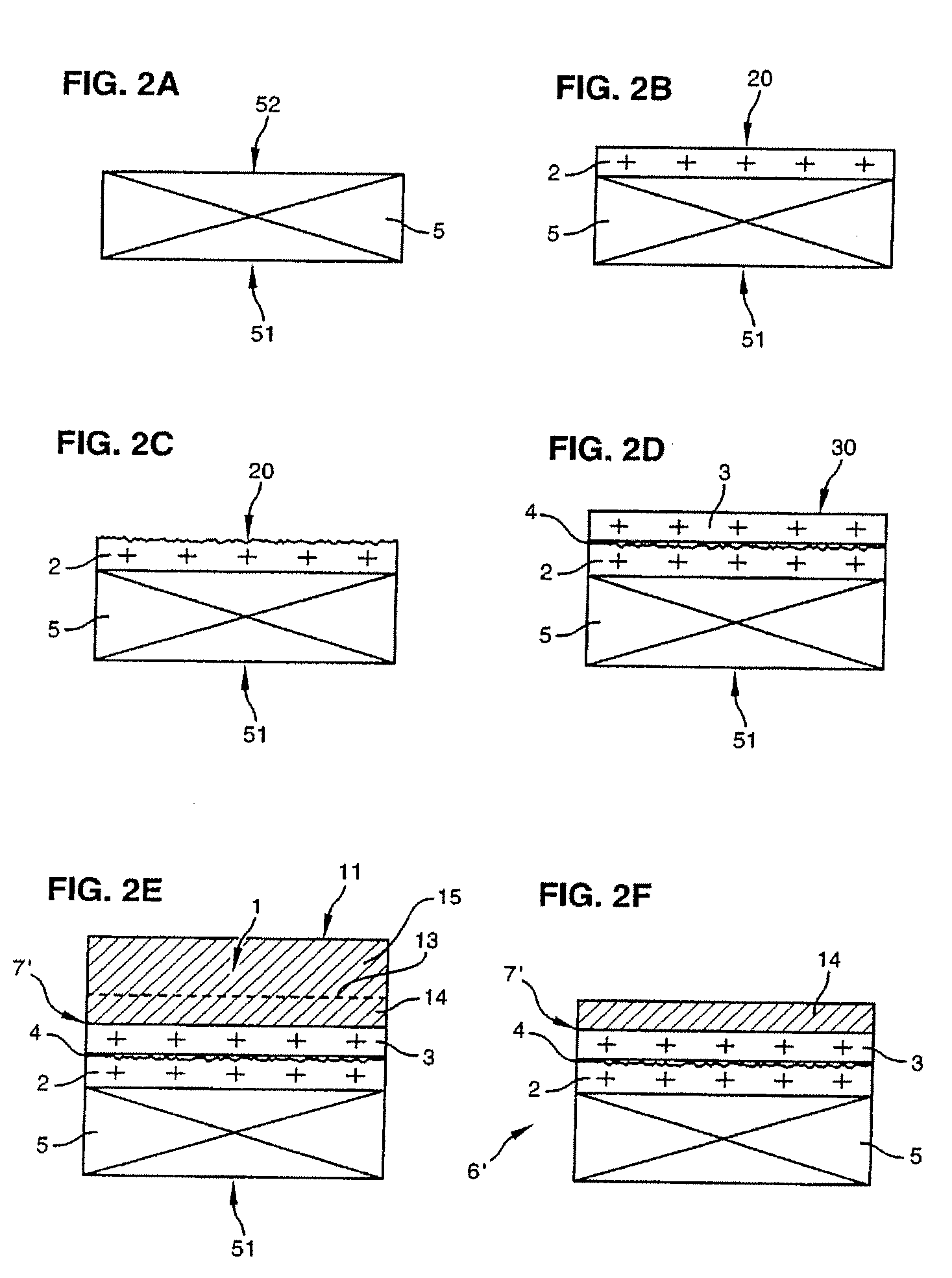

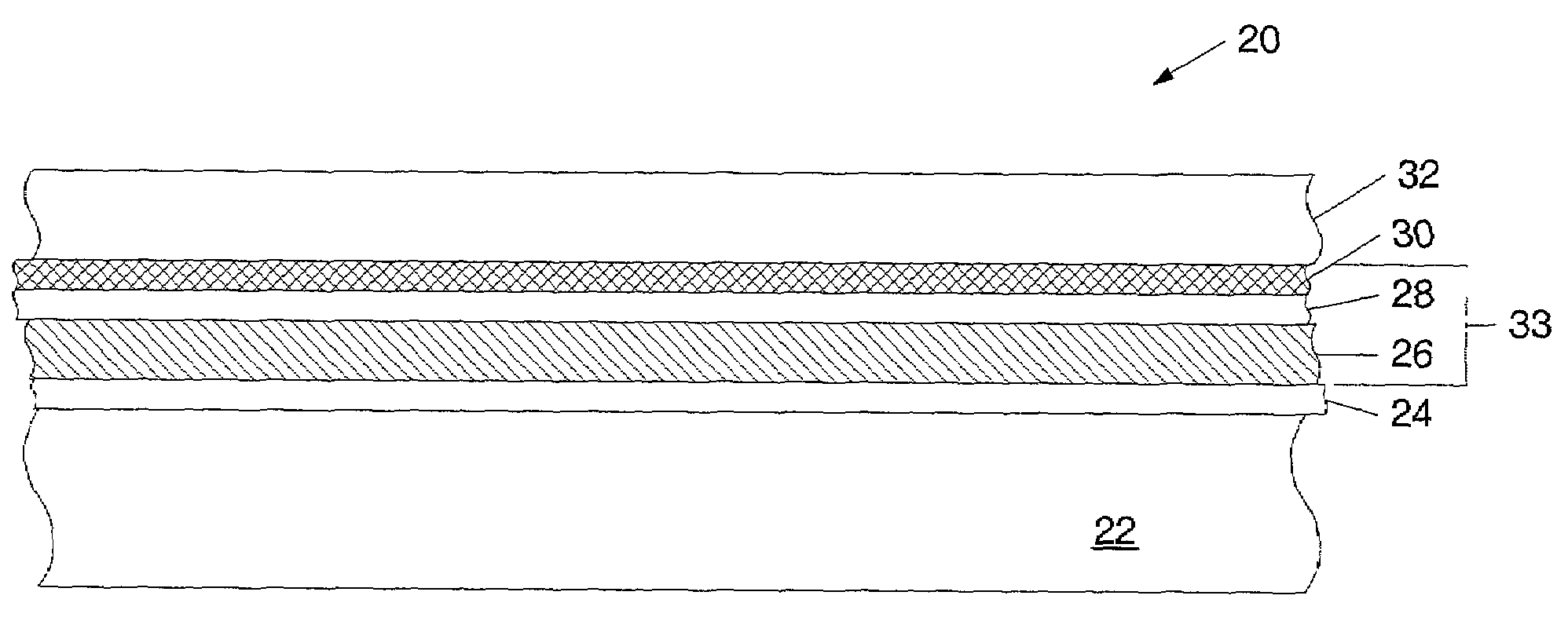

Composite membranes and methods for making same

ActiveUS20070256562A1Increase in H fluxHigh selectivityMembranesSemi-permeable membranesFiltrationActive layer

Composite membranes that are adapted for separation, purification, filtration, analysis, reaction and sensing. The composite membranes can include a porous support structure having elongate pore channels extending through the support structure. The composite membrane also includes an active layer comprising an active layer material, where the active layer material is completely disposed within the pore channels between the surfaces of the support structure. The active layer is intimately integrated within the support structure, thus enabling great robustness, reliability, resistance to mechanical stress and thermal cycling, and high selectivity. Methods for the fabrication of composite membranes are also provided.

Owner:INTEGRATED DEVICE TECH INC

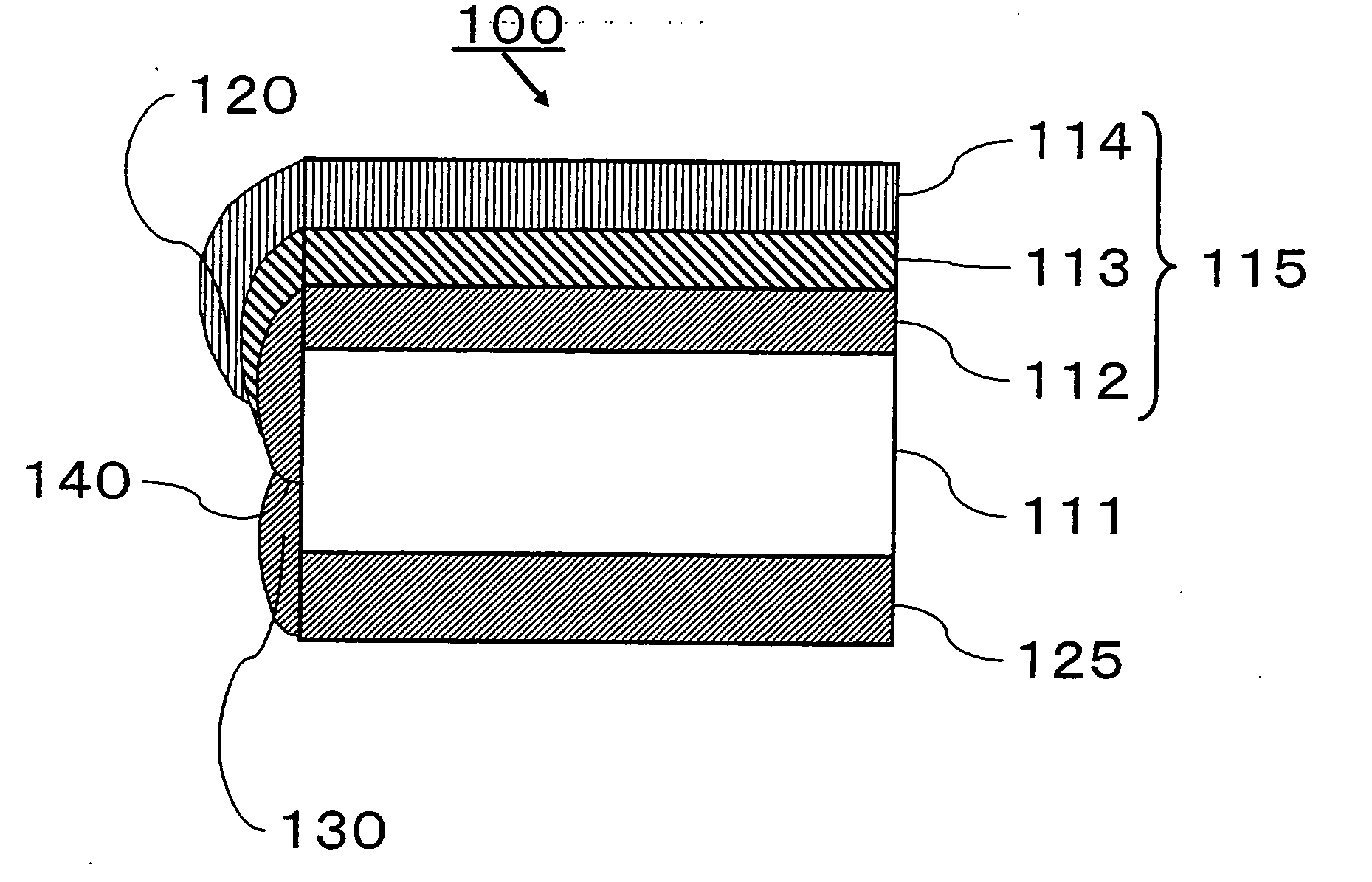

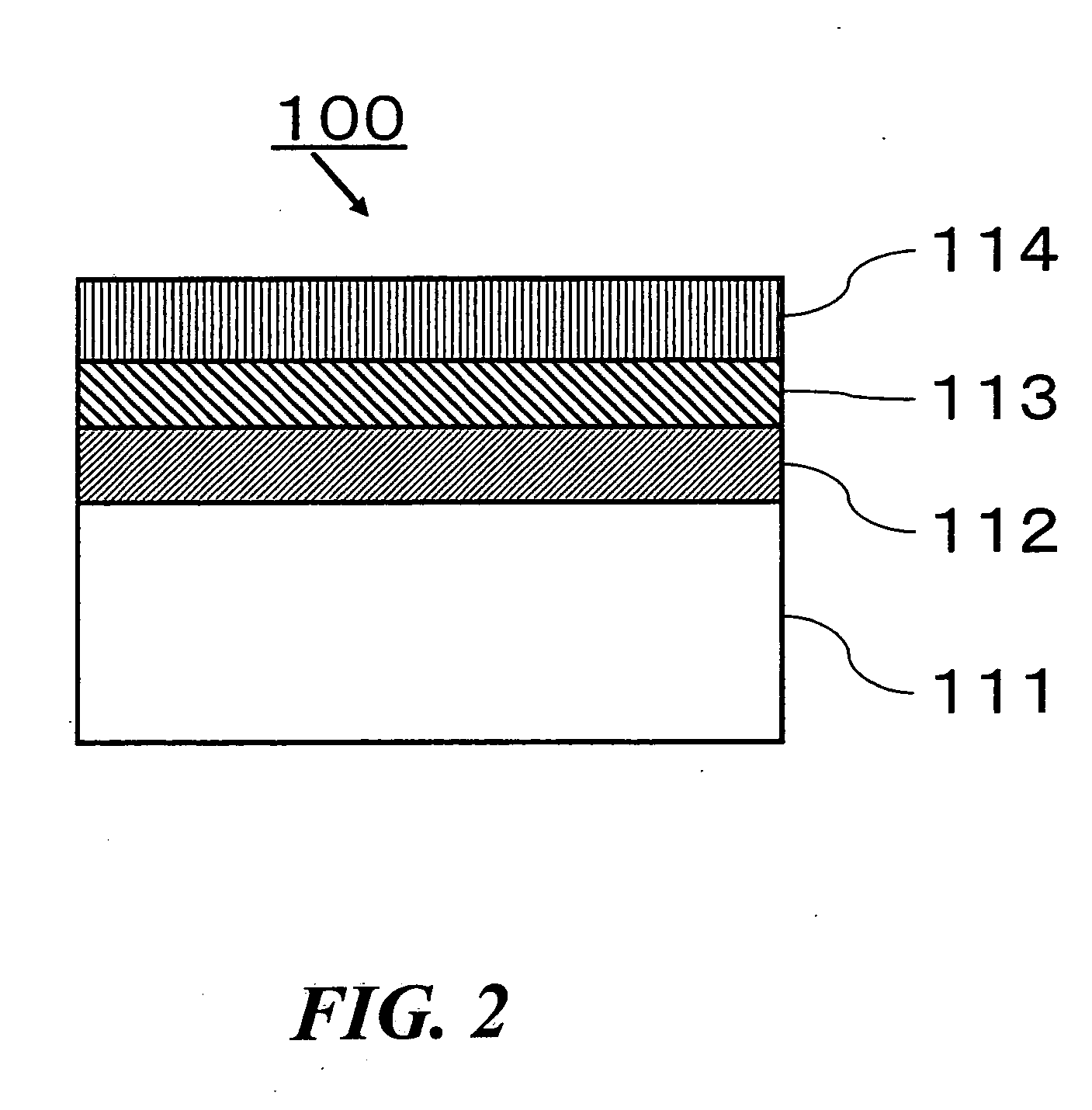

Reflective-type mask blank for EUV lithography

ActiveUS20070160916A1Reduce defect formationRadiation/particle handlingNanoinformaticsLithographic artistElectrical connection

There are provided a substrate with a reflective layer and an EUV mask blank, which can prevent particles from adhering to a surface of the reflective layer or an absorbing layer, or into a reflective layer or an absorbing layer during formation thereof by eliminating electrical connection between a film formed on a front surface of the substrate and a film formed on a rear surface of the substrate. A substrate with a reflective layer, which is usable to fabricate a reflective mask blank for EUV lithography, comprising a chucking layer formed on a rear surface opposite a surface with the reflective layer formed thereon, the chucking layer serving to chuck and support the substrate by an electrostatic chuck, wherein the reflective layer has no electrical connection to the chucking layer.

Owner:ASAHI GLASS CO LTD

Fabrication of hybrid substrate with defect trapping zone

ActiveUS7632739B2Inhibition formationReduce defect formationSemiconductor/solid-state device manufacturingSemiconductor materialsTrapping

A process for fabricating a hybrid substrate that has a defect trapping zone. The process includes the steps of forming or depositing a first insulator layer on a first substrate of semiconductor material; increasing roughness of the first insulator layer surface; depositing a second insulator layer on the roughened surface of the first insulator to form a trapping zone between the layers; bonding a second substrate onto the second insulator layer by molecular adhesion; and transferring an active layer formed by the implantation of atomic species into one of the substrates. The trapping zone is able to retain gaseous species present at the various interfaces of the hybrid substrate to limit the formation of defects on the surface of the active layer that is transferred.

Owner:SOITEC SA

Super-fine TiC0.7N0.3 base metal ceramic and preparing method

This invention has publicized one kind of superfine cermet and its preparation method. Each composition ingredient weight percent of this cermet is: Mo2C: 8-13wt %; WC: 10-15wt %; TaC: 5-8wt %; NiCo:10.5-14.5wt % (also Co: Ni = 60: 40); the reminder is TiC0.7N0.3. This cermet uses the superfine TiC0.7N0.3 solid solution as raw material powder, and deoxidation process the superfine powder, it solved the technical difficult problems of preparation superfine cermet such as wet milling easy to to be agglomeration, compaction easy to dehiscence and easy to form holes after being sintered because powder granularity thin and breath. The processed powder adopt optimization wet milling craft, and add stearic acid mountain ash grain fat dispersing agent; Suppressed under 300 -400MPa pressure to shape; do dewaxing under 10-15Pa higher than vacuum degree; sinter vacuum degree is higher than 1-5X10-2Pa, sinter temperature is 1400degree C-1,480degree C, then holding 1-1.5h; do the hot isostatic pressing processing at 1,350degree C, holding 90-120min, the argon pressure is 70-120MPa. The prepared cermet has crystal grain size 0.5mum and the typical core - link structure, its hardness is>=93HRA, anti-curved intensity>=2200MPa, it may used as half precision work and precision work cutting tool material.

Owner:SICHUAN UNIV

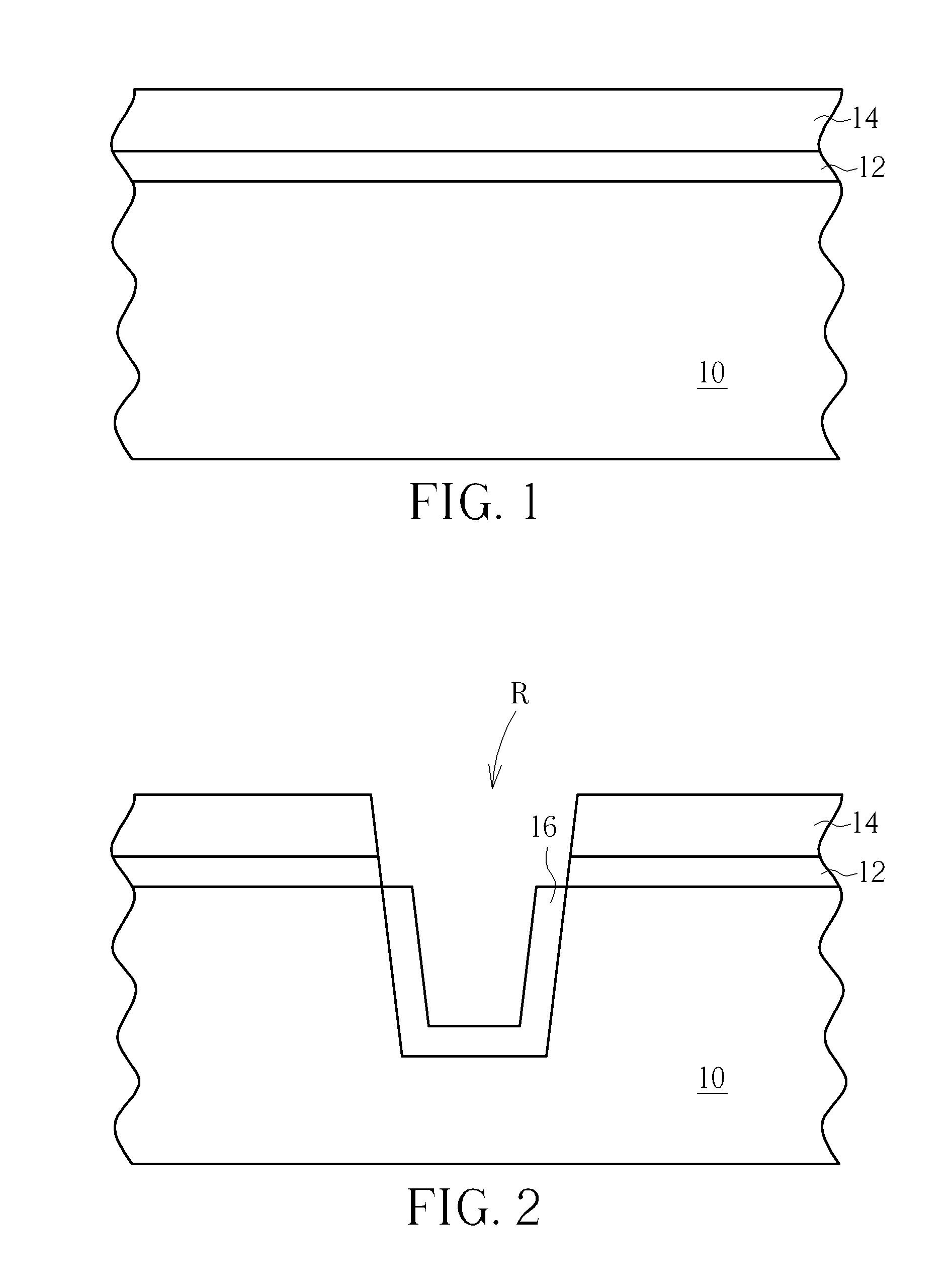

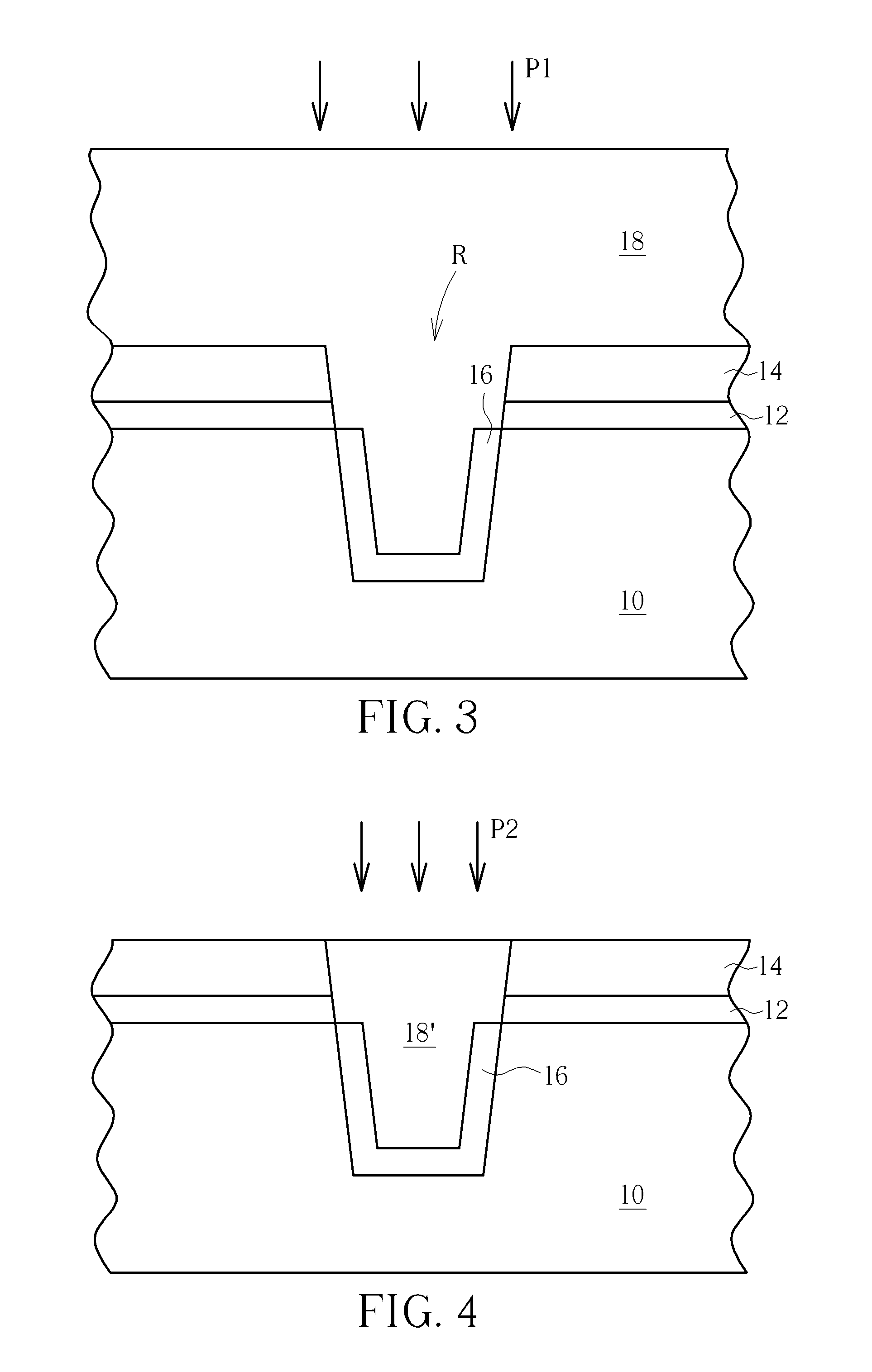

Method of fabricating dielectric layer and shallow trench isolation

ActiveUS20140134824A1Excellent gap fillingNot to damageSemiconductor/solid-state device manufacturingOxygen plasmaCompound (substance)

A method of fabricating a dielectric layer includes the following steps. At first, a dielectric layer is formed on a substrate, and a chemical mechanical polishing (CMP) process is performed on the dielectric layer. Subsequently, a surface treatment process is performed on the dielectric layer after the chemical mechanical polishing process, and the surface treatment process includes introducing an oxygen plasma.

Owner:UNITED MICROELECTRONICS CORP

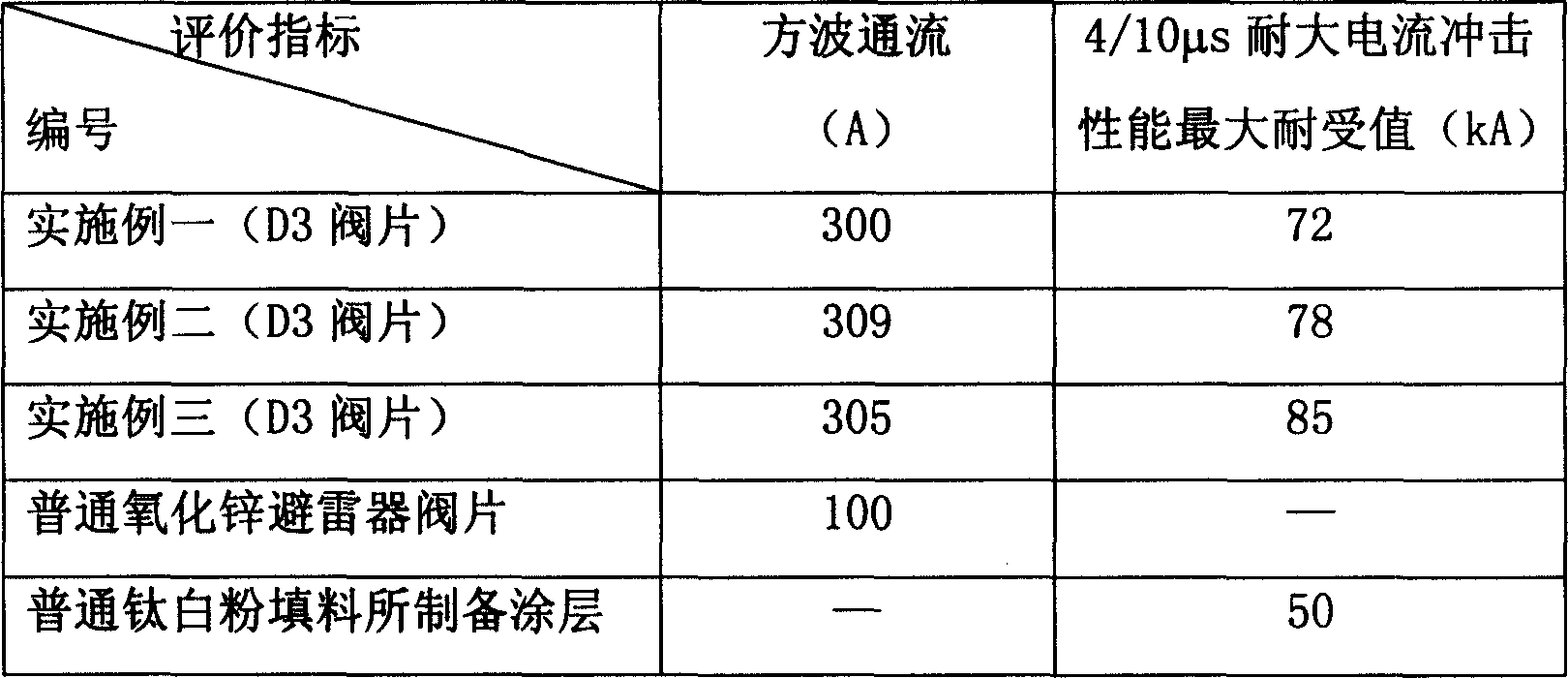

Method for preparing high throughflow nanometre composite lightning arrester valve plate

ActiveCN1571078AImprove flow capacitySimple processOvervoltage protection resistorsNanometreVaristor

The invention relates to and provides a method for preparing high throughflow nano composite arrester varistor, and its characteristic: it adopts nano ZnO material as the main material, adds nano powder additive in 5-20wt% to mix them fully, makes press forming by a two-way press to form the varistor, then sinters at 900-1100 deg.C to make a main body of ZnO varistor; sprays aluminum on the main body and coats an inorganic high resistance layer on the side of the ZnO varistor, where the high resistance layer is mainly made of lead oxide or chrome oxide; then coats the side with heavy current-withstanding nano insulating composite coating prepared of nano functional fillings and epoxy oxazolidinone resin in the ratio of 20-30 to 70-80 (wt%), uniformly roll-coats the prepared nano insulating composite coating on the side, dries at a high temperature of 300 deg.C, and makes it.

Owner:上海上纳电工器材有限公司

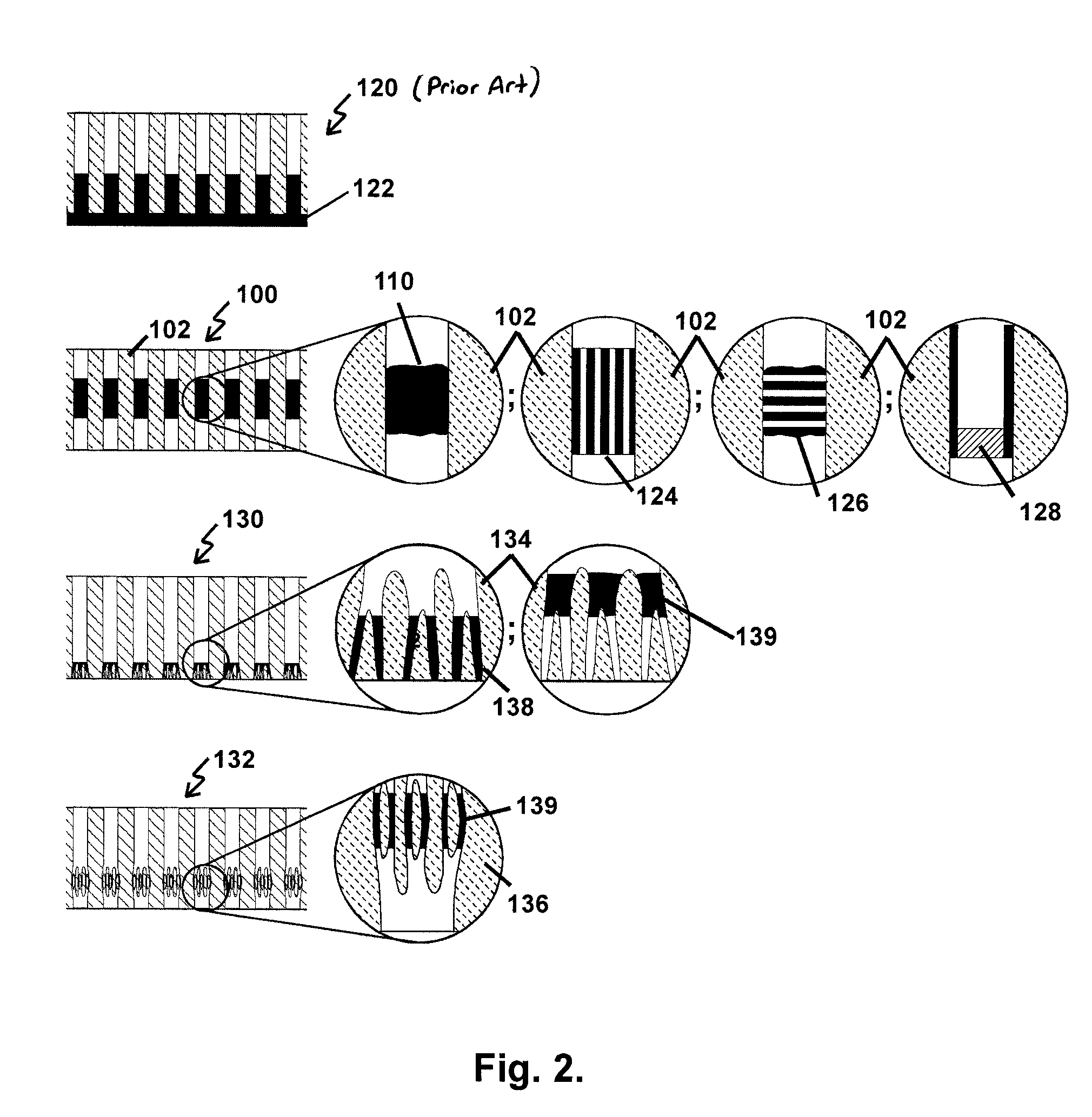

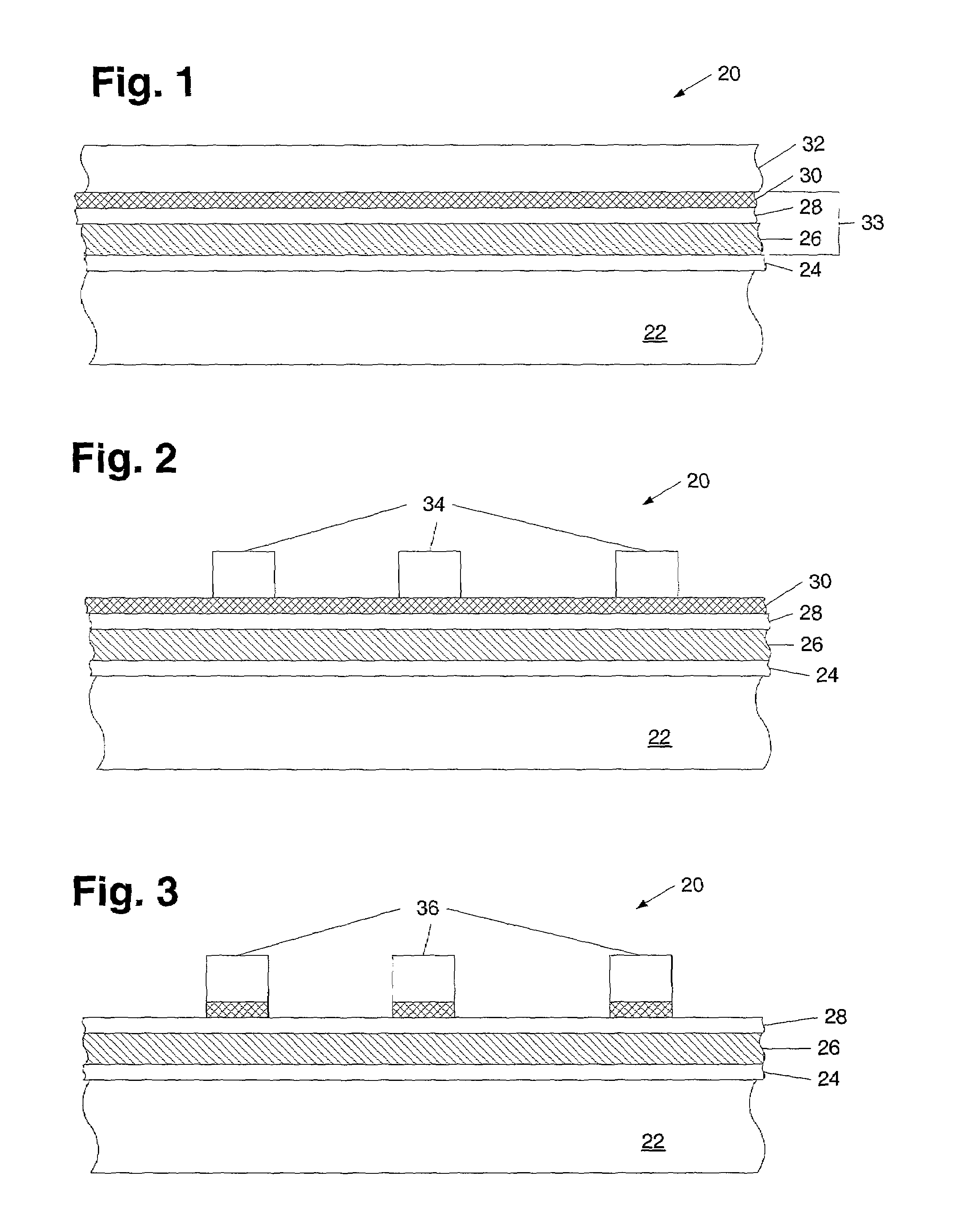

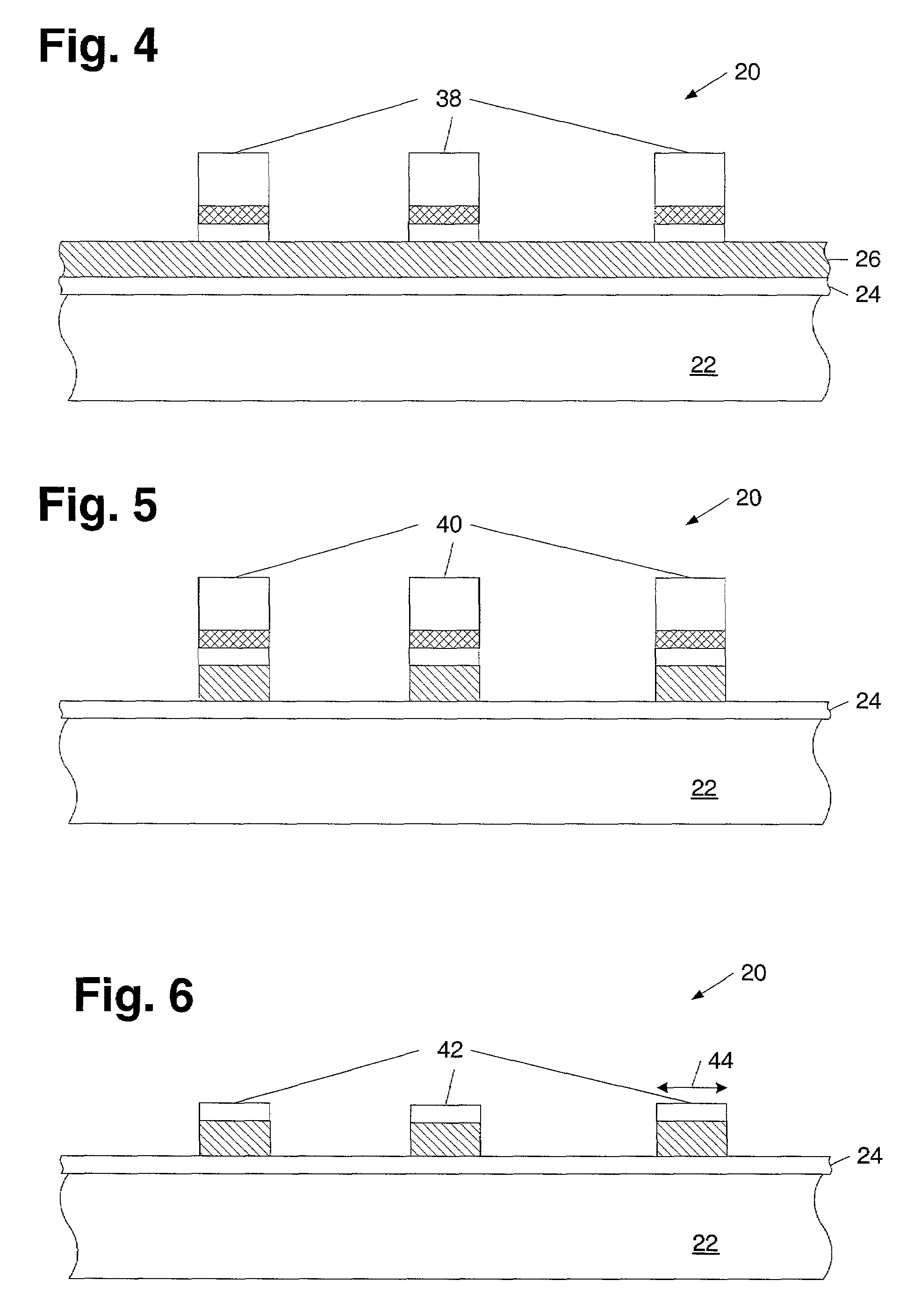

Reducing defect formation within an etched semiconductor topography

InactiveUS7129178B1Reduce formationReduce removalSemiconductor/solid-state device manufacturingNoble gasTopography

A method is provided which includes etching one or more layers in an etch chamber while introducing a noble gas heavier than helium into the etch chamber. In a preferred embodiment, the introduction of such a noble gas may reduce the formation of defects within an etched portion of the semiconductor topography. Such defects may include bilayer mounds of nitride and a material comprising silicon, for example. In some embodiments, the method may include etching a stack of layers within a single etch chamber. The stack of layers may include, for example, a nitride layer interposed between an anti-reflective layer and an underlying layer. In addition, the single etch chamber may be a plasma etch chamber designed to etch materials comprising silicon. As such, the method may include etching an anti-reflective layer in a plasma etch chamber designed to etch materials comprising silicon.

Owner:MONTEREY RES LLC

Method for preparing anti-wear, anti-corrosion nano composite epoxy asphalt repair paint

InactiveCN1821325AEffective dispersionReduce defectsAnti-corrosive paintsEpoxy resin coatingsEpoxySlurry

The present invention discloses the preparation process of antiwear, anticorrosive nanometer composite epoxy asphalt repair paint. The repair paint has organic surfactant coated nanometer level functional powder in 2-15 wt% added, and the nanometer level functional powder is one or two selected from titania, silica, zinc oxide, nickel oxide, alumina, chromium oxide, manganese oxide and barium sulfate. The nanometer level powder is first dispersed in small amount of epoxy resin through ball milling, sand grinding or high speed emulsification to form slurry, and the slurry is then mixed with the main epoxy asphalt repair paint component to obtain the antiwear, anticorrosive nanometer composite epoxy asphalt repair paint. The composite epoxy asphalt repair paint is used in repairing coated film and has high anticorrosive performance and high scratch resistance.

Owner:SHANGHAI UNIVERSITY OF ELECTRIC POWER

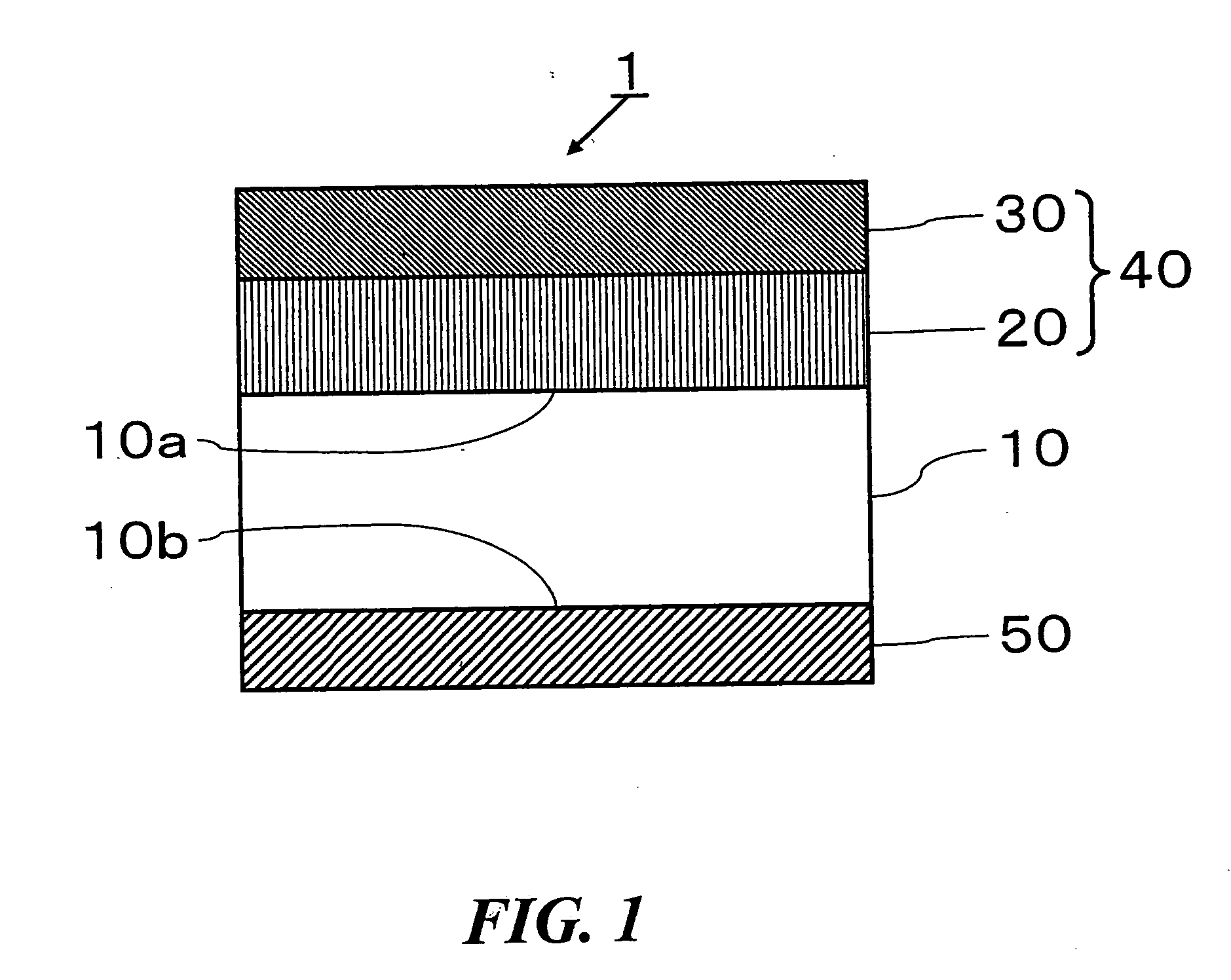

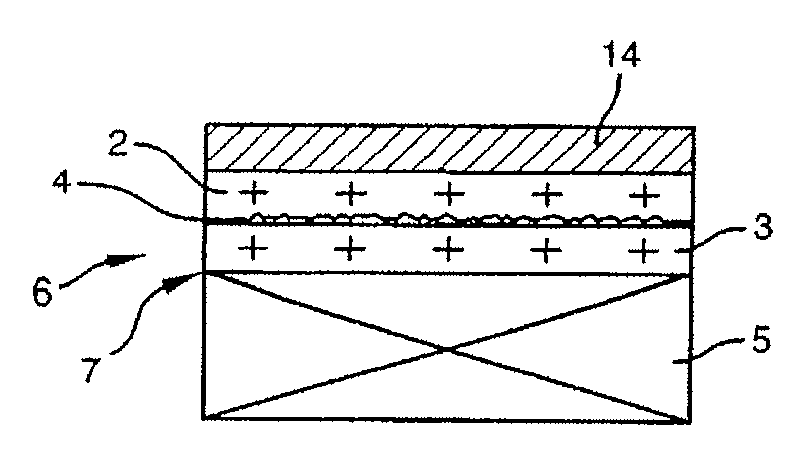

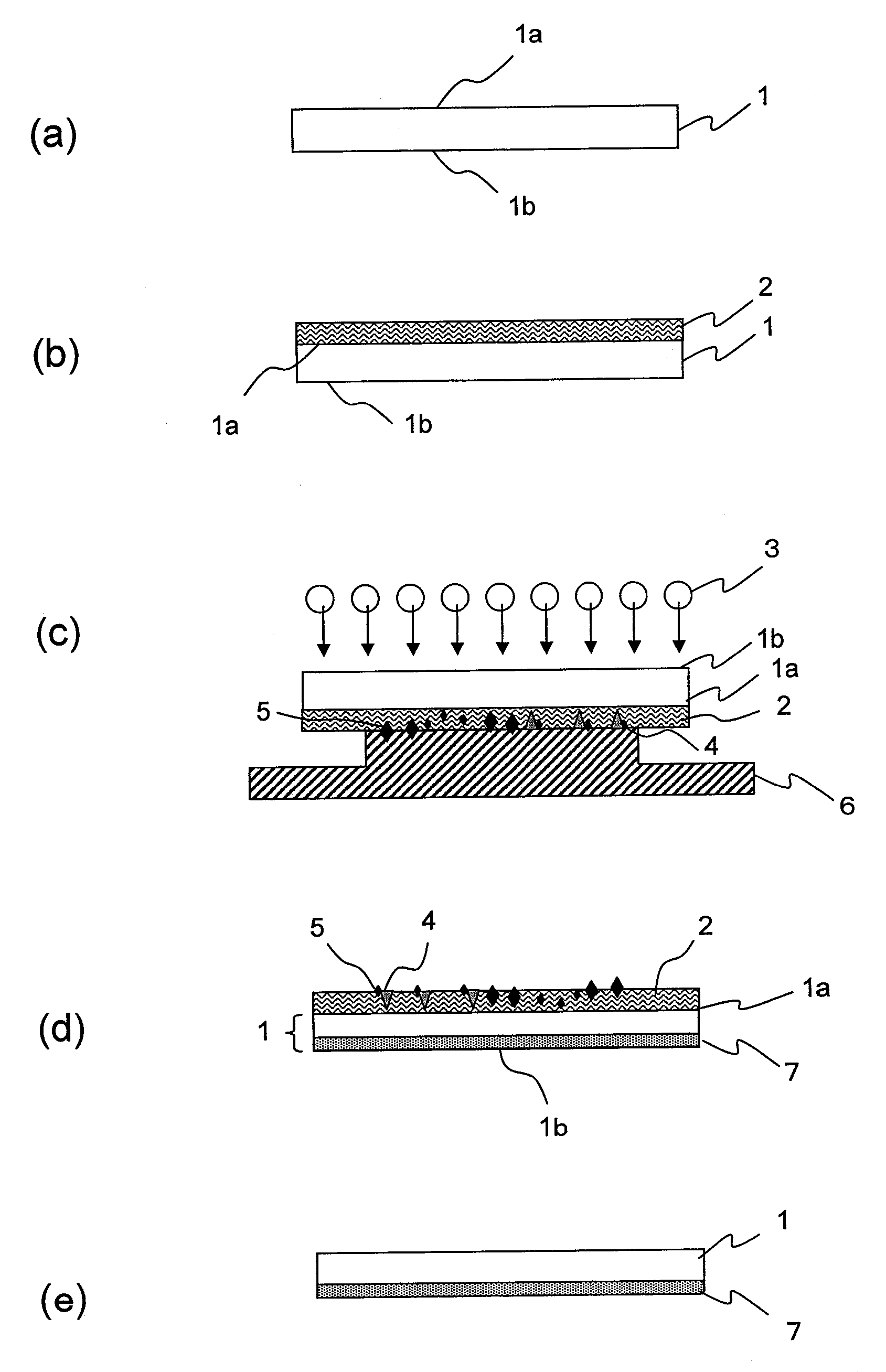

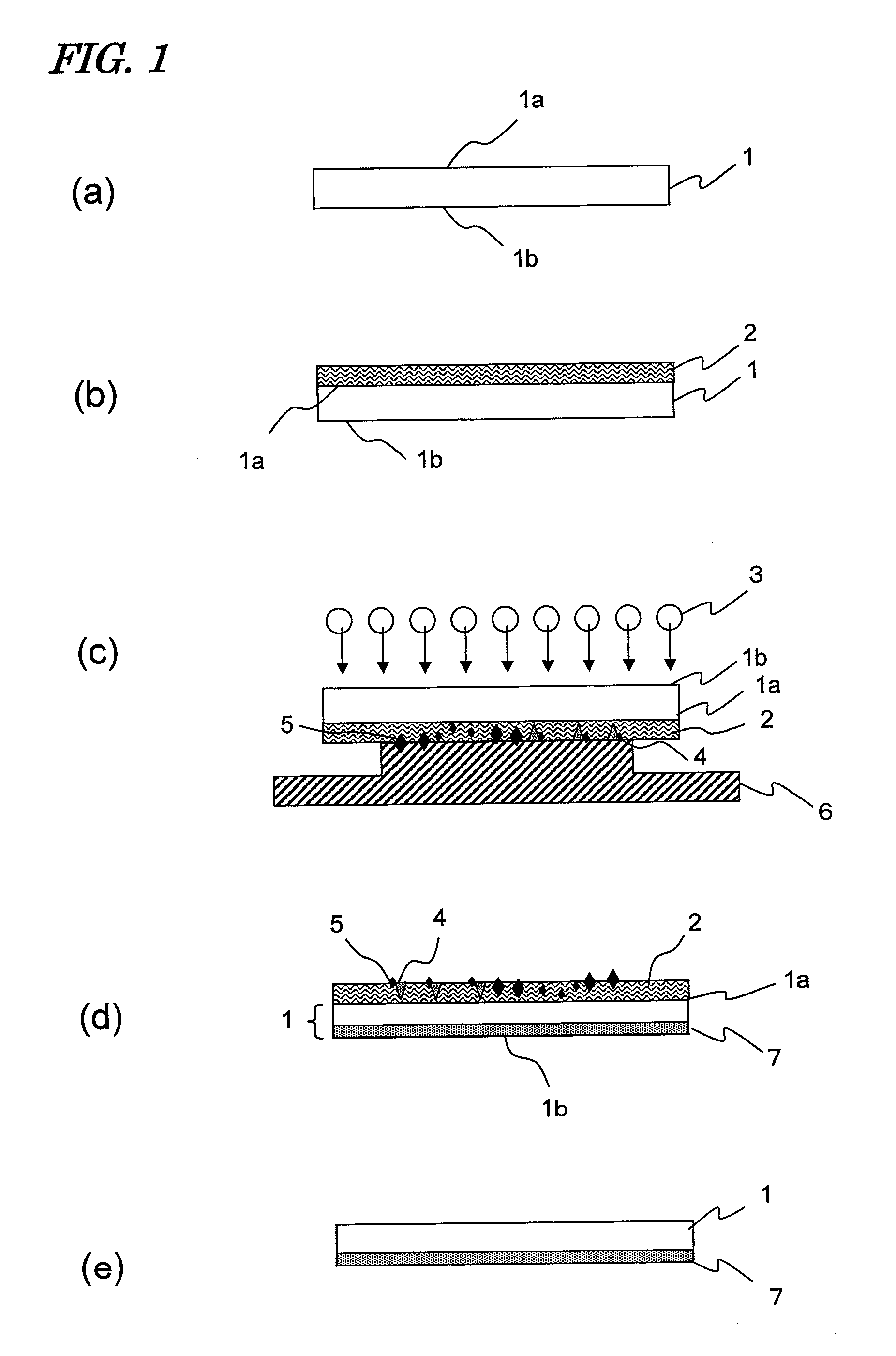

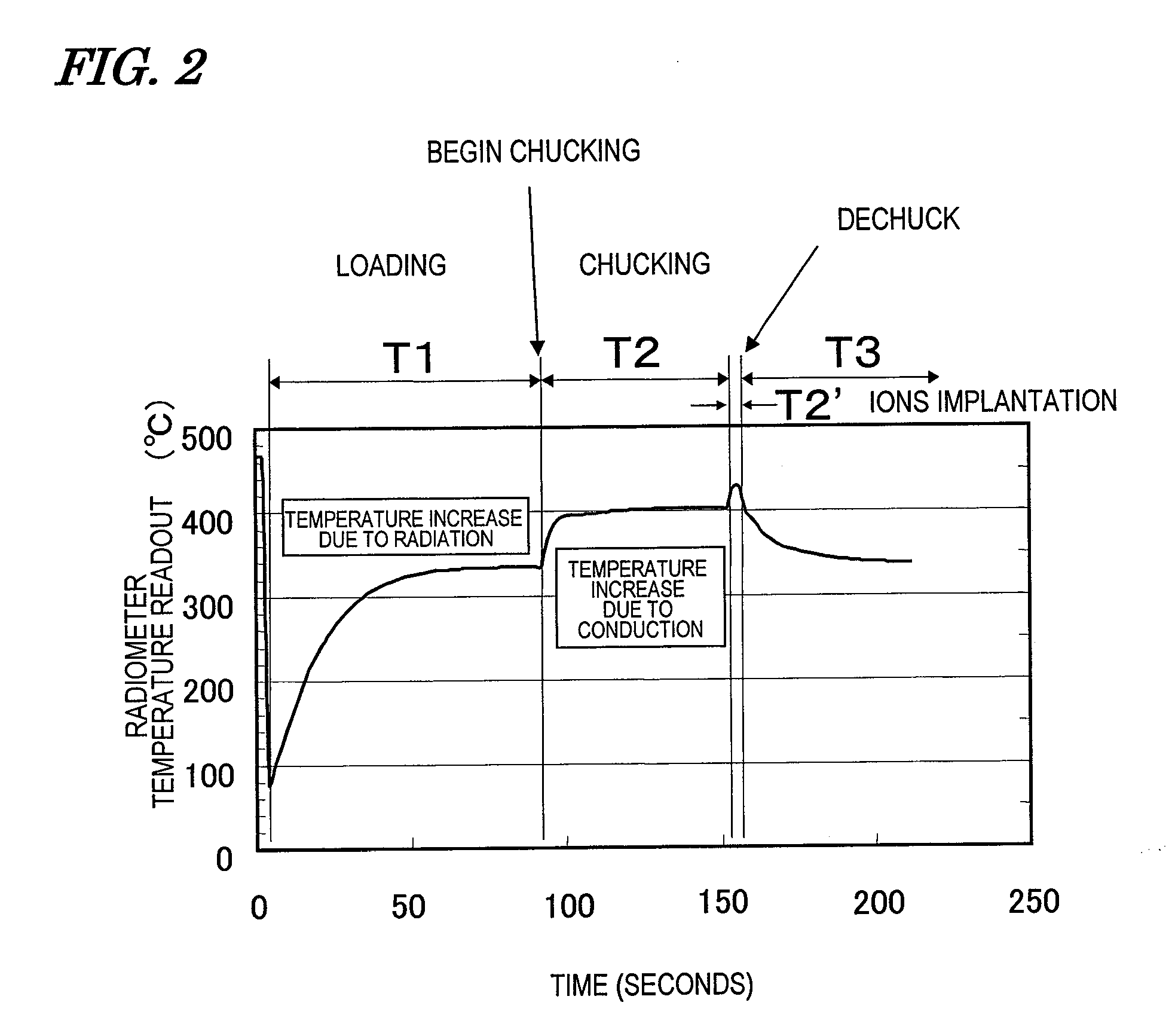

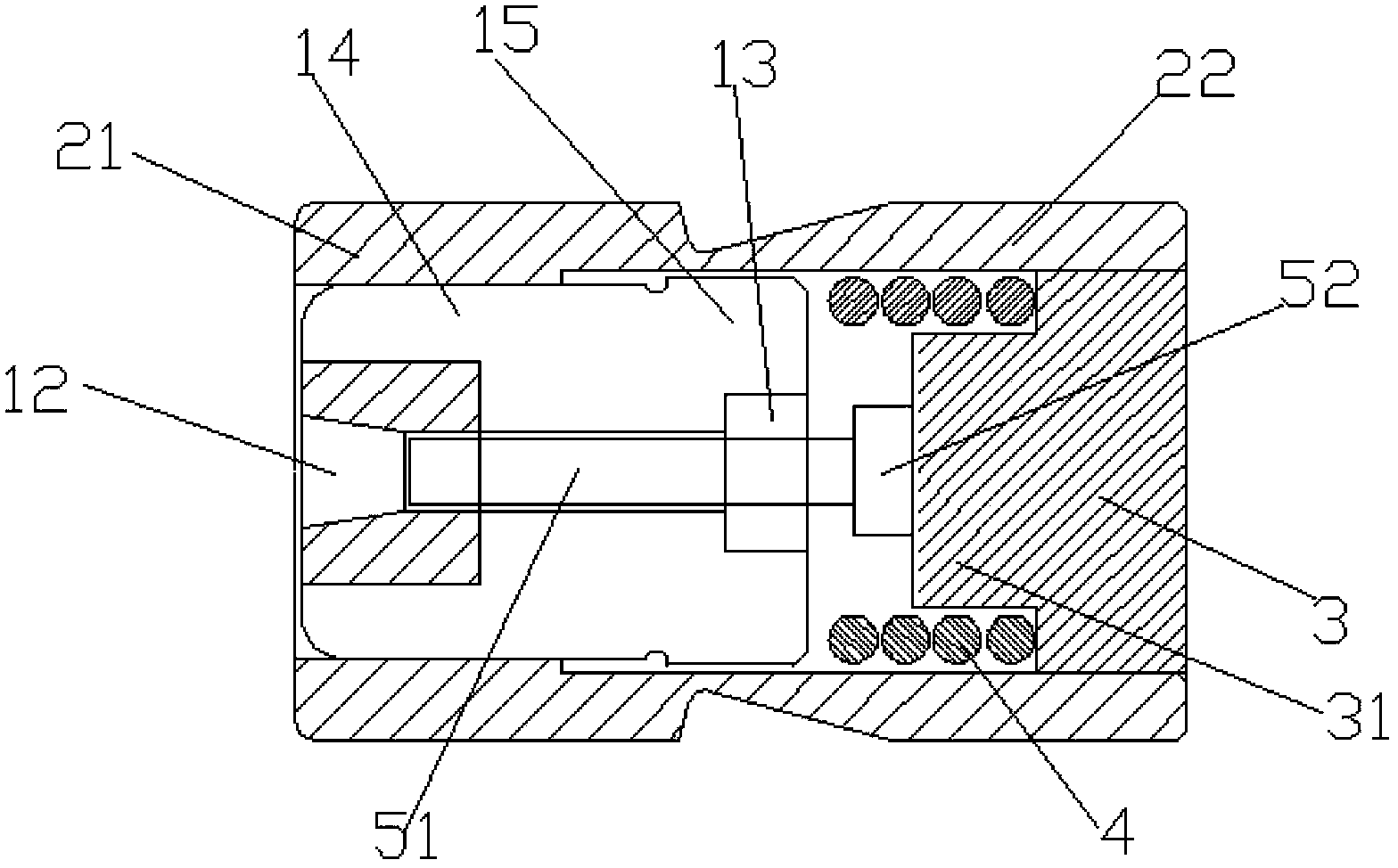

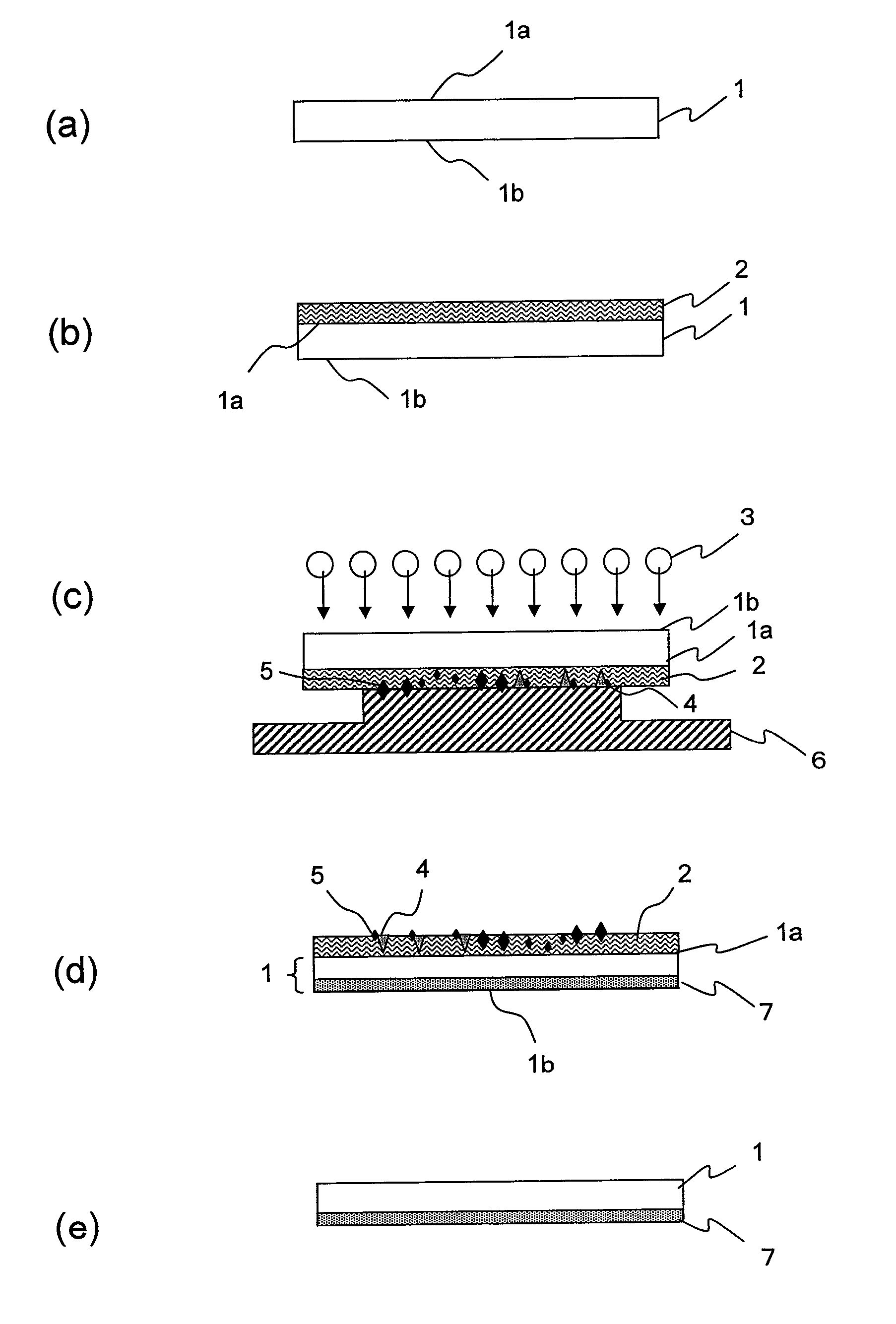

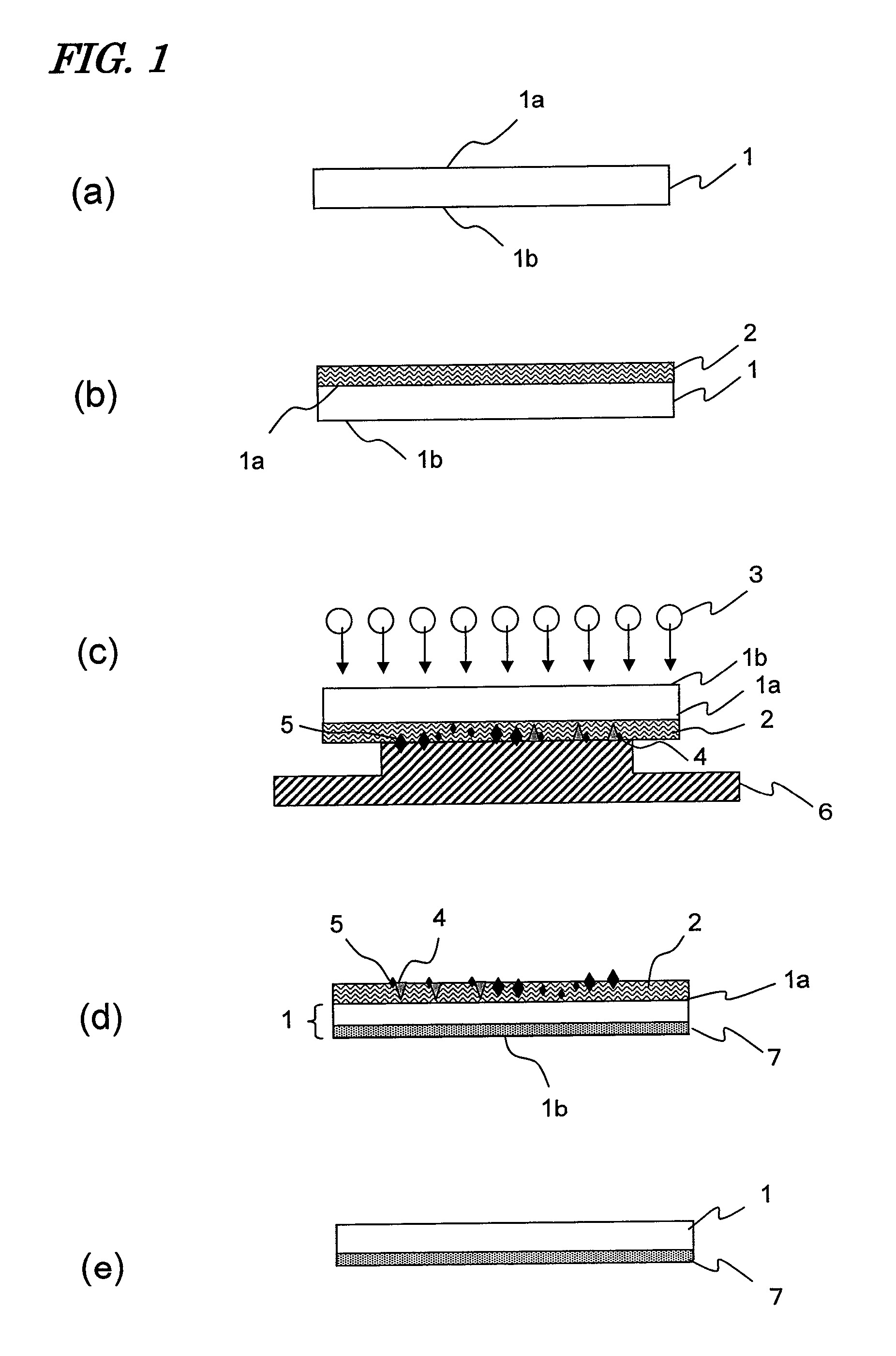

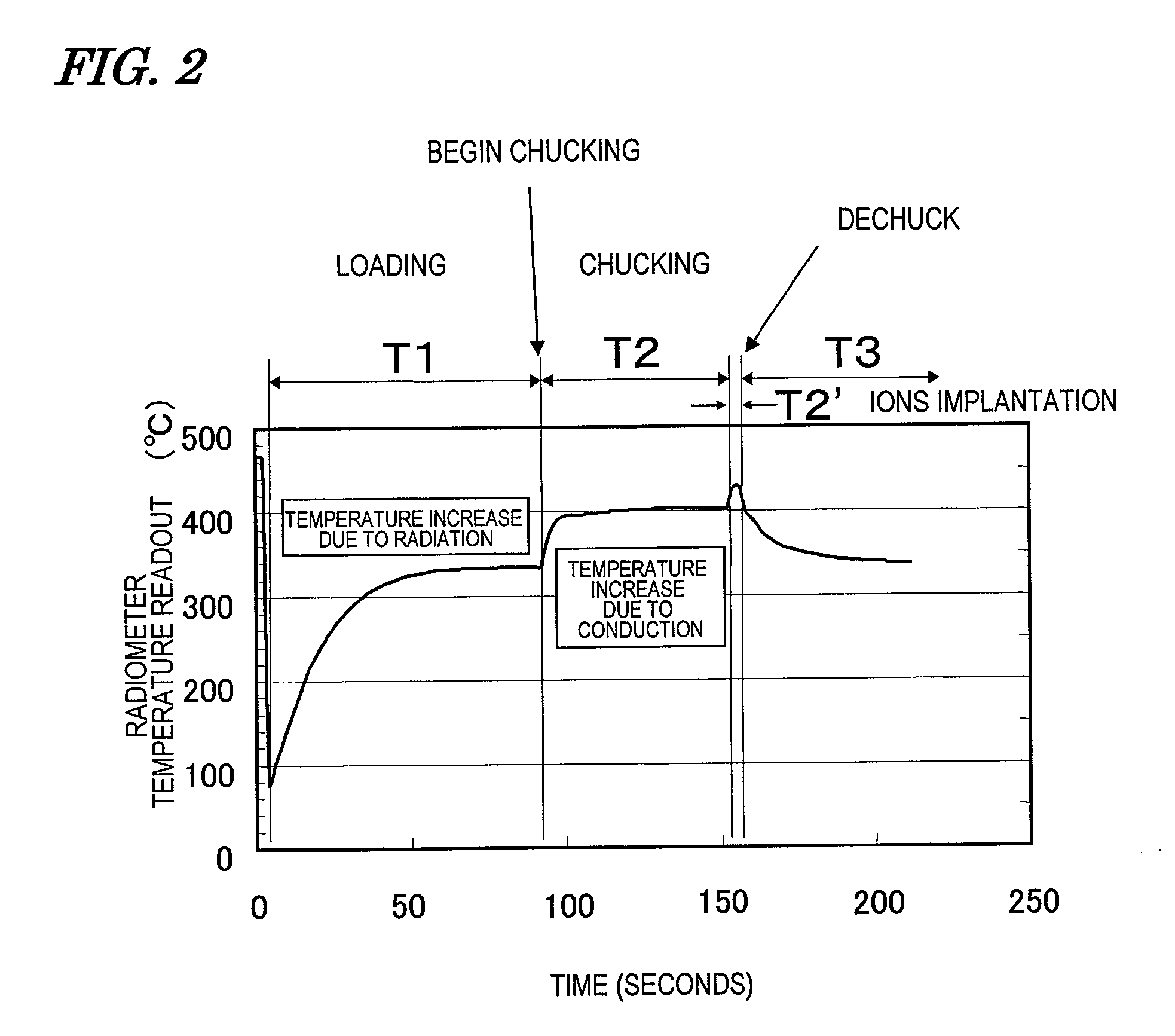

Method for manufacturing semiconductor device

ActiveUS20100093161A1Reduce formation of defectReduce defect formationLiquid surface applicatorsElectric discharge tubesEngineeringSemiconductor

On one face of a semiconductor wafer 1 having a first face (principal face) 1a and a second face (rear face) 1b, a protection film 2 is formed. When allowing the semiconductor wafer 1 to be attracted onto an attracting face of an electrostatic chuck 6 which is heated to 400° C. or more, the semiconductor wafer 1 is attracted onto the attracting face via the protection film 2. While heating the semiconductor wafer 1 to 400° C. or more, an ion implantation is performed for the face of the semiconductor wafer 1 on which the protection film 2 is not formed. Thereafter, the protection film 2 is removed from the semiconductor wafer 1.

Owner:PANASONIC CORP

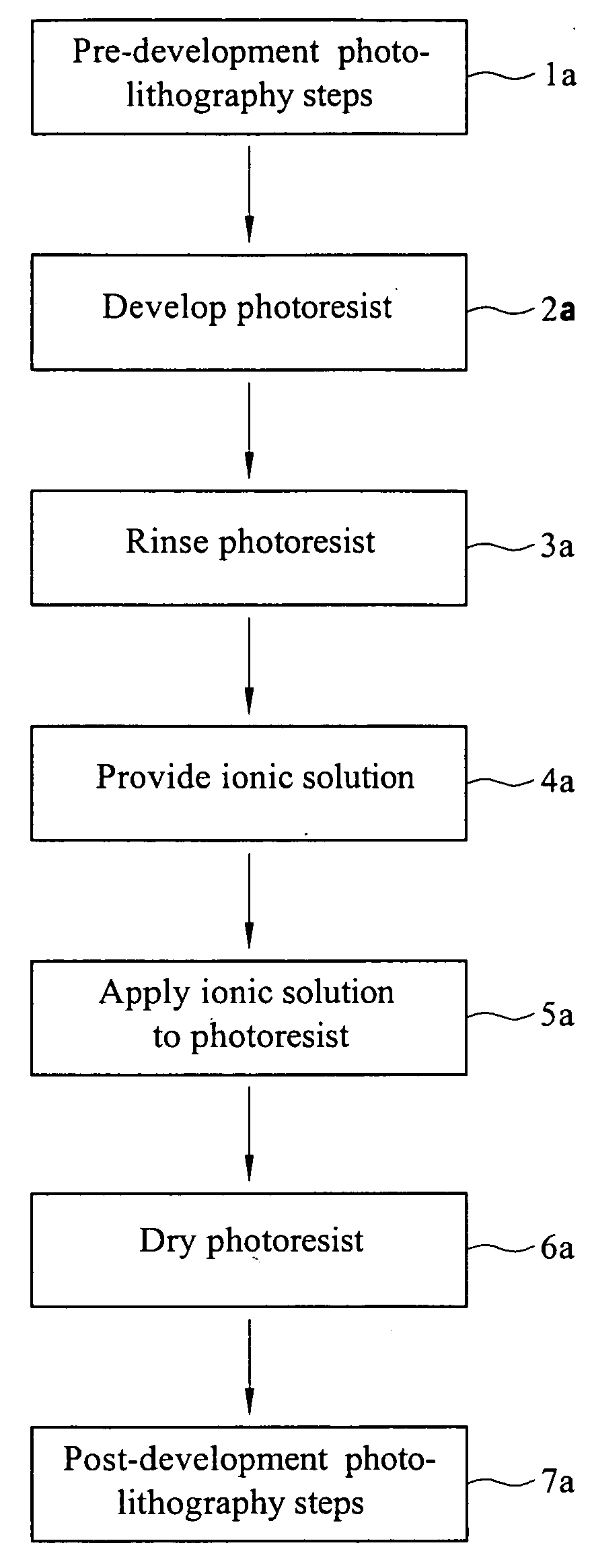

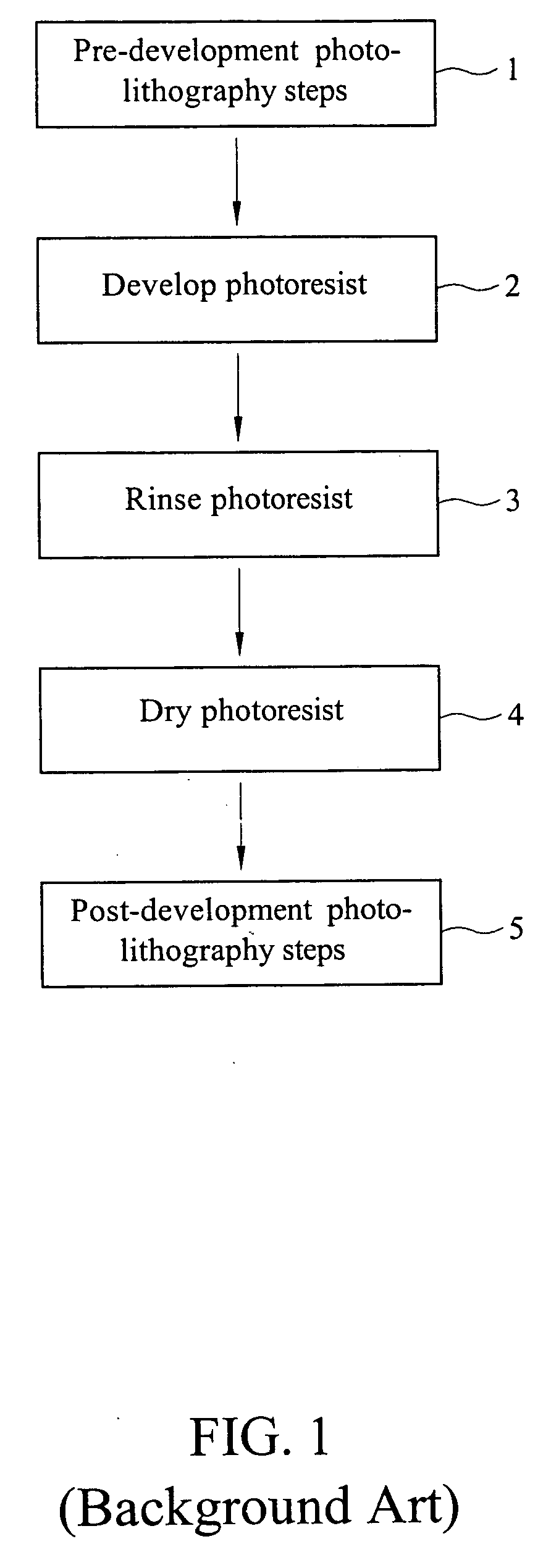

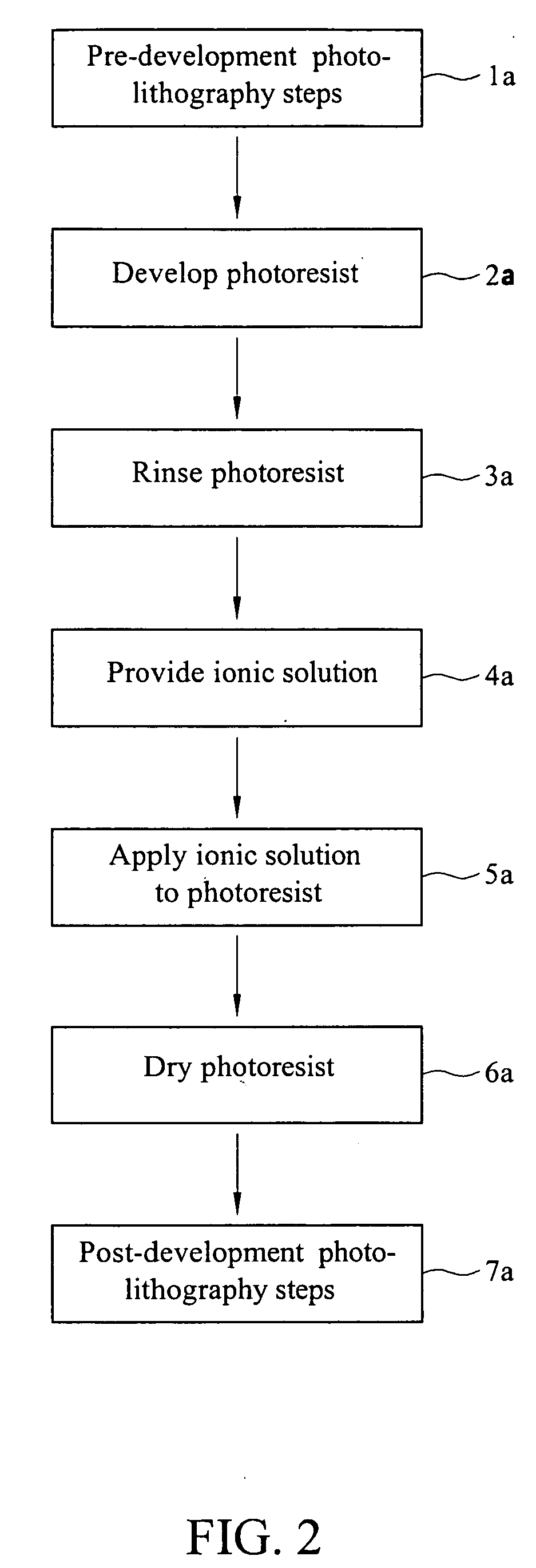

Method for reducing wafer charging during drying

InactiveUS20060115774A1Eliminating and reducing accumulationReduce defect formationPhotomechanical apparatusSemiconductor/solid-state device manufacturingEngineeringPhotolithography

A novel method for eliminating or reducing the accumulation of electrostatic charges on semiconductor wafers during spin-rinse-drying of the wafers is disclosed. The method includes rinsing a wafer; applying an ionic solution to the wafer; and spin-drying the wafer. During the spin-drying step, the ionic solution neutralizes electrostatic charges on the wafer as the wafer is rotated. This reduces the formation of defects in devices fabricated on the wafer, as well as prevents or reduces electrostatic interference with processing equipment during photolithographic and other fabrication processes.

Owner:TAIWAN SEMICON MFG CO LTD

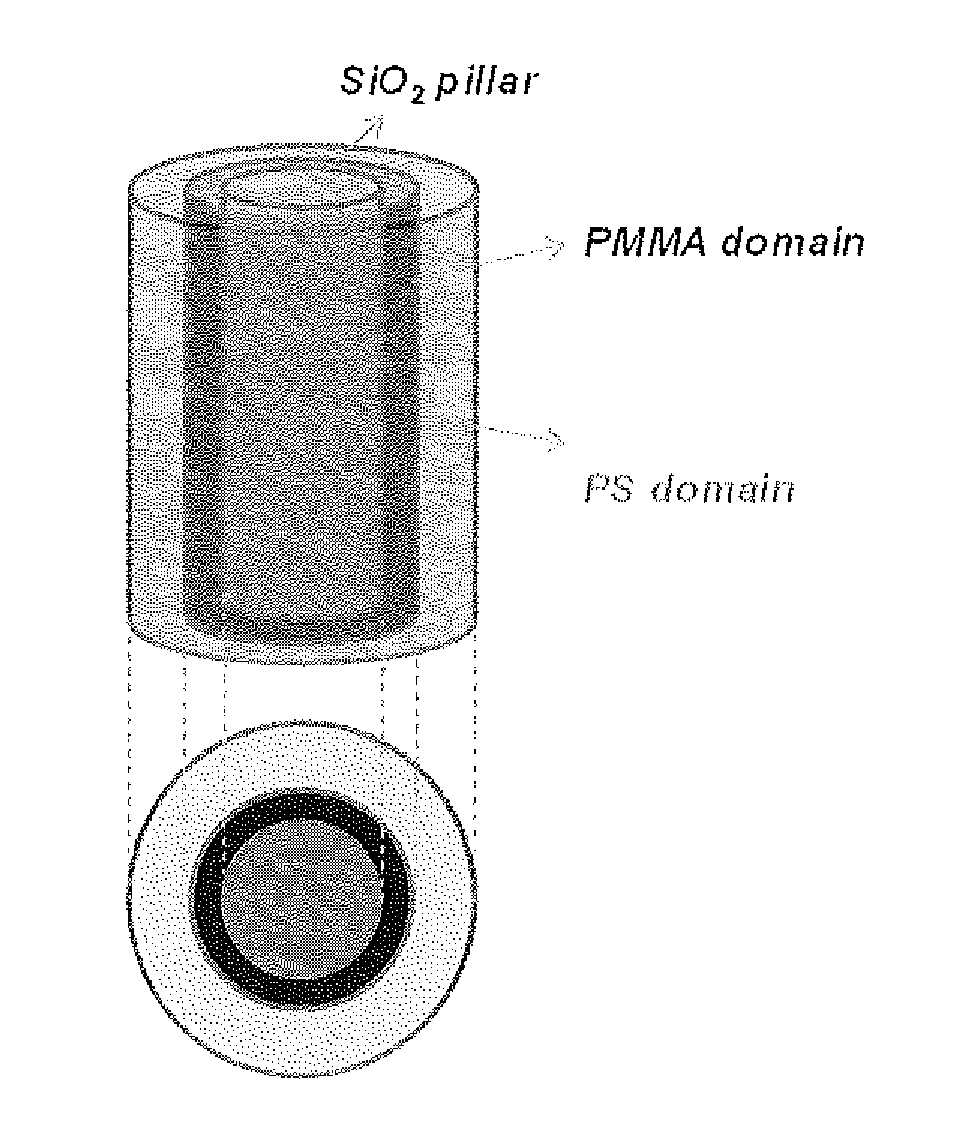

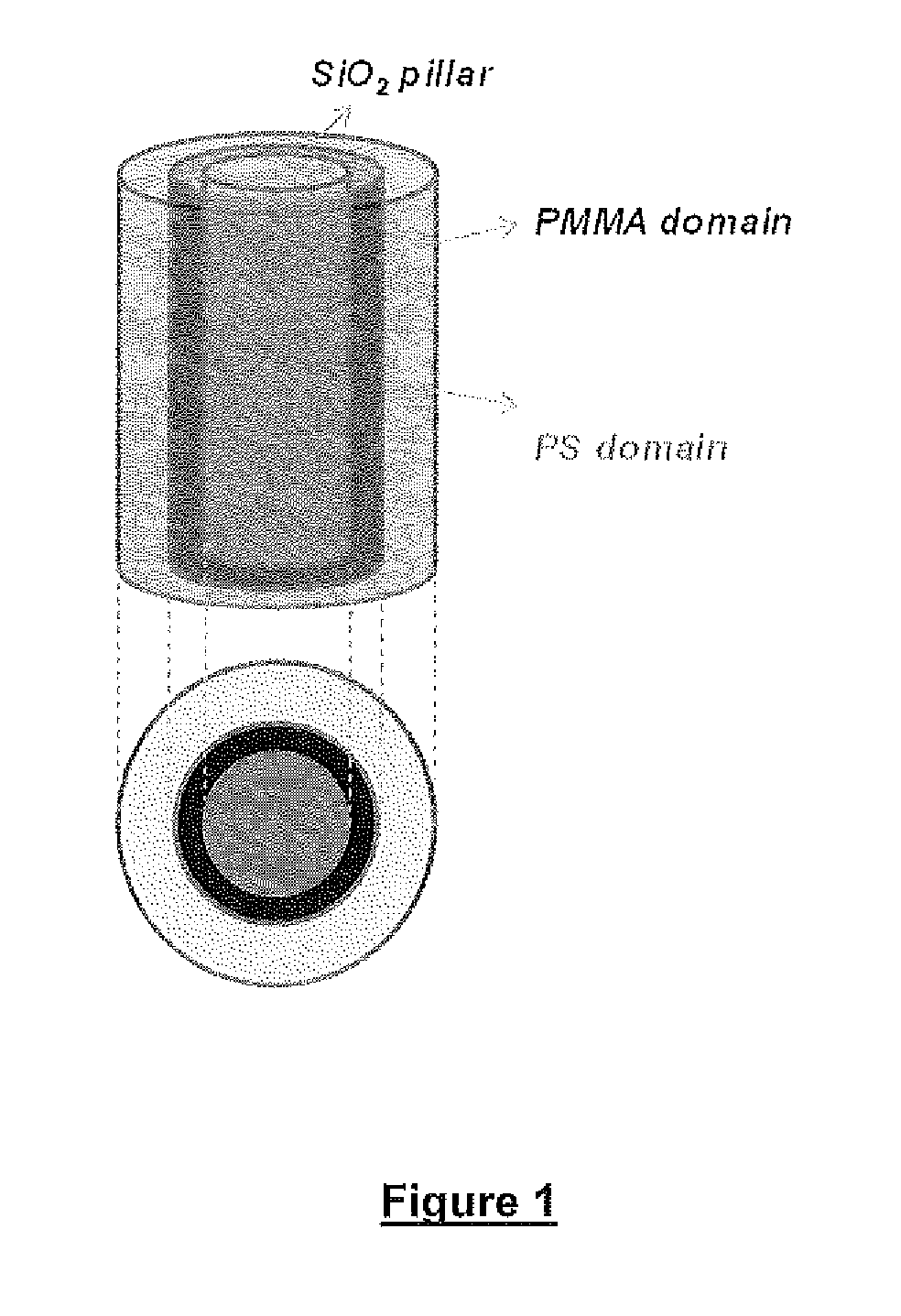

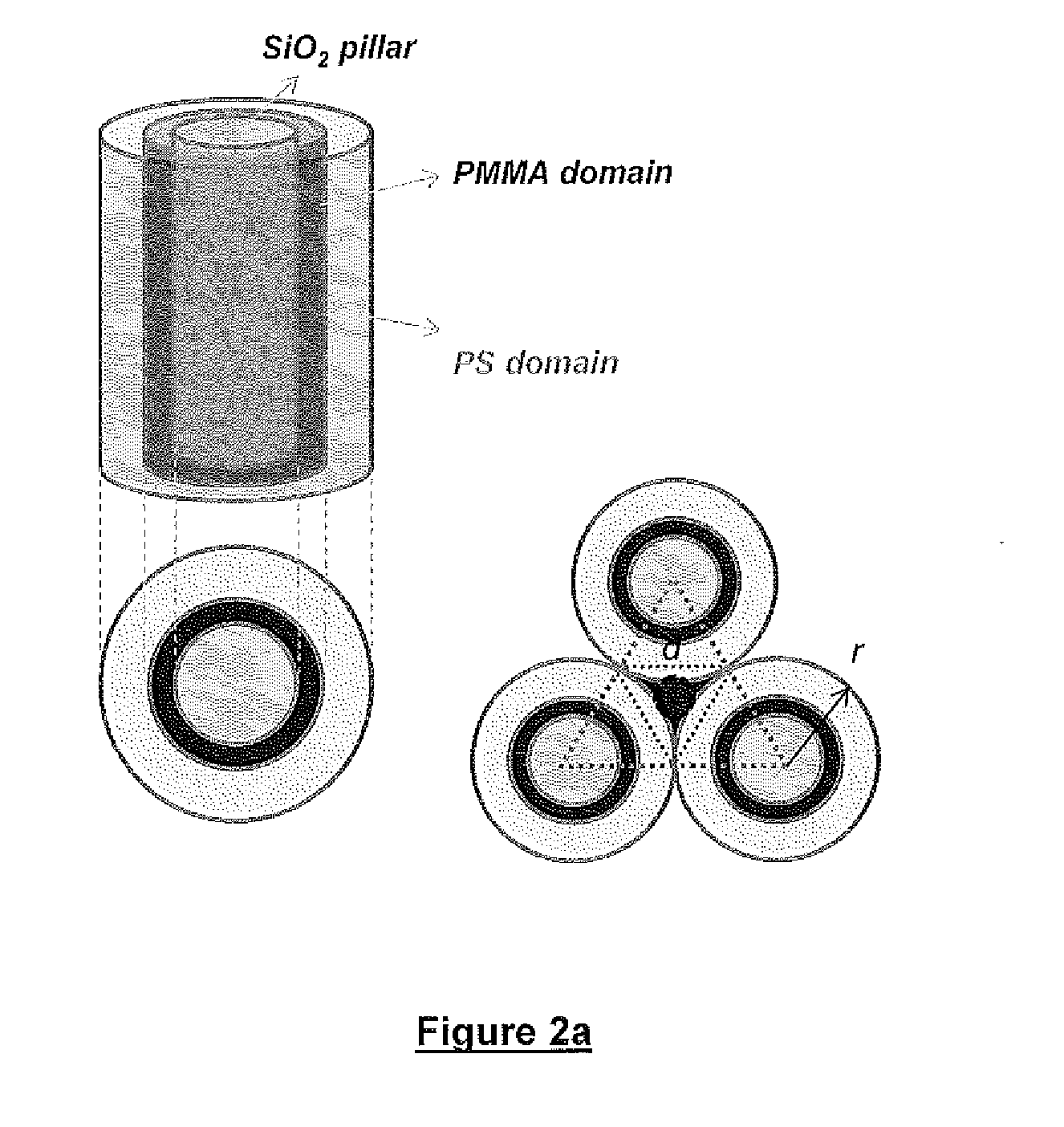

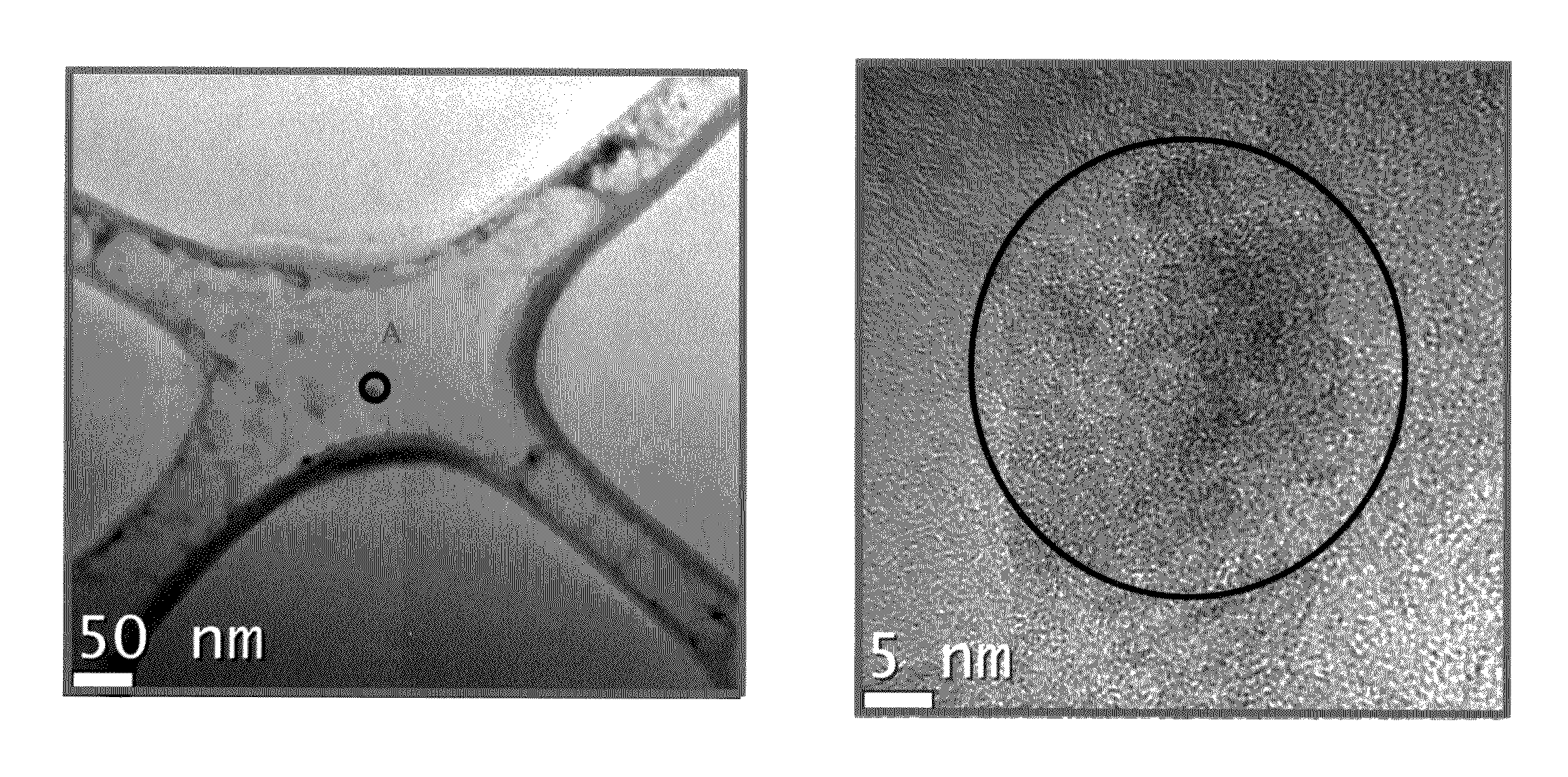

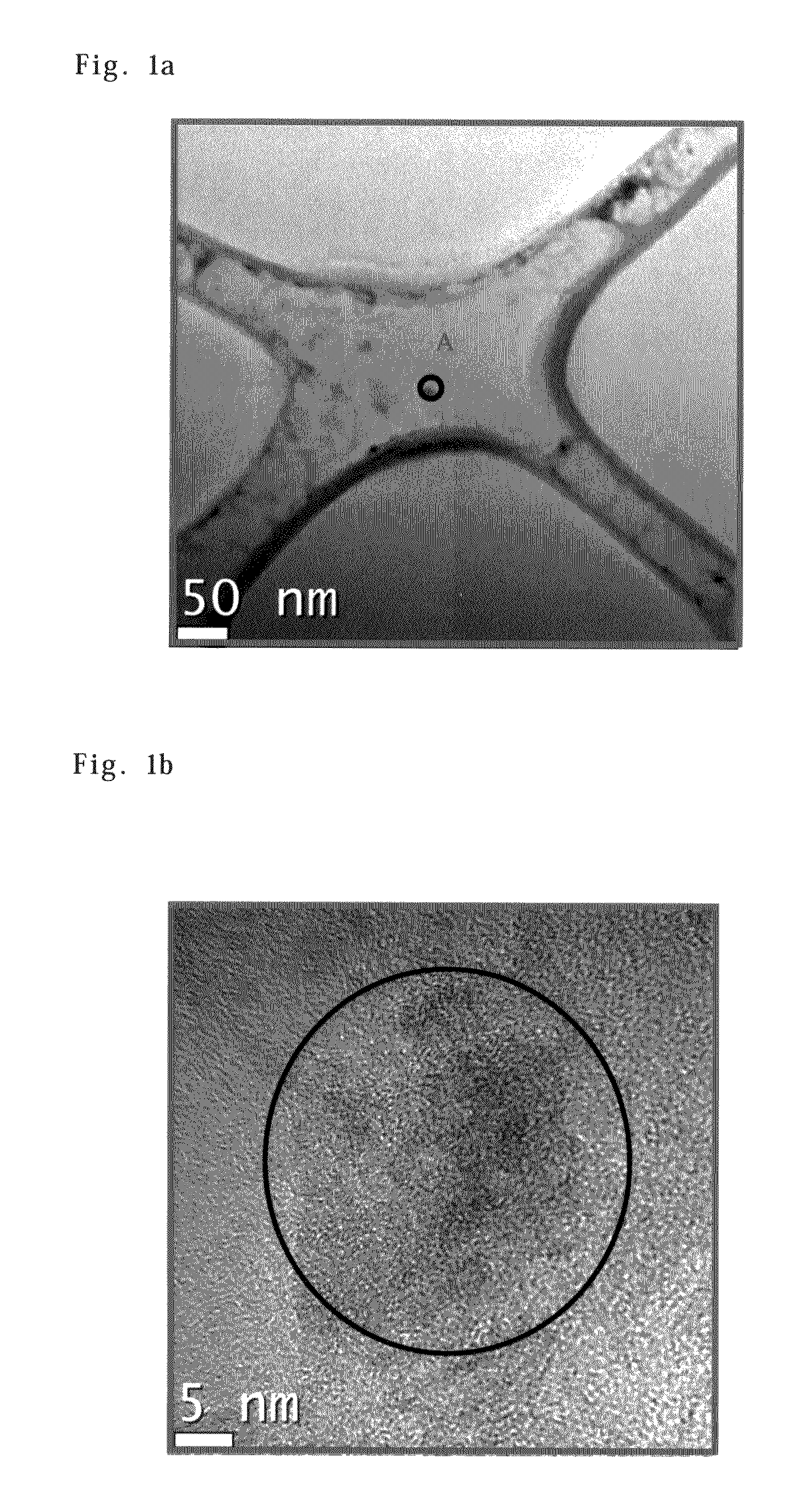

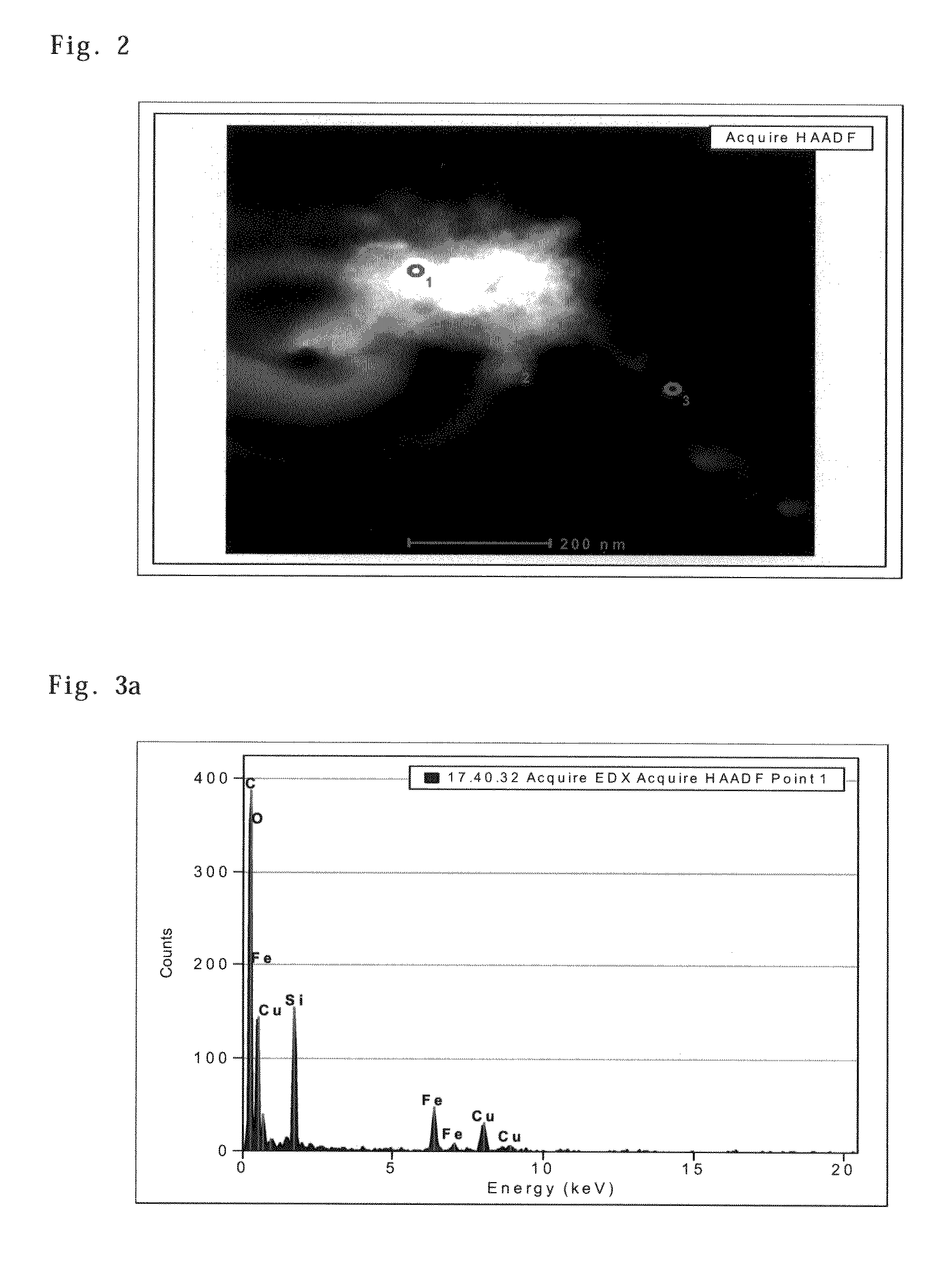

Defect reduction methods and composition for via formation in directed self-assembly patterning

InactiveUS20160122580A1Inhibition formationBetter grafting of the hydroxyl terminated polyhydroxystyreneElectric discharge tubesFilm/foil adhesivesArylHydrophobic polymer

The present invention relates to a two novel processes, “Dual Coating Process and Single Coating Process,” for forming an array of via's by employing a graphoepitaxy approach, where an array of pillars the surface of the pillars has been modified by the formation of a hydrophobic poly(vinyl aryl) brush at the surface of the pillars. The present invention also relates to a composition comprising a poly(vinyl aryl) hydrophopic polymer brush precursor terminated at one chain end with a reactive functional group, a diblock copolymer comprising an etch resistant hydrophobic block and a highly etchable hydrophilic block, a thermal acid generator and a solvent.

Owner:AZ ELECTRONICS MATERIALS LUXEMBOURG R L

Method for preparing chemical mechanical polishing slurry composition

ActiveUS8241375B1Reduce defect formationPigmenting treatmentOther chemical processesCompound (substance)Slurry

A method for preparing a chemical mechanical polishing slurry composition comprises the steps of preparing an aqueous iron salt solution by admixing an iron salt and cooled water of 5° C. or less; preparing an oxide containing silicon and iron as an additive by admixing and stirring a silicon salt and the aqueous iron salt solution for carrying out a reaction of the silicon salt and the aqueous iron salt solution to form an additive solution; and mixing the additive solution with at least one abrasive, at least one oxidizing agent and optionally at least one additional component to form the chemical mechanical polishing slurry composition.

Owner:DONGJIN SEMICHEM CO LTD

Modified phenolic resin and process for preparing the same

The present invention discloses one kind of modified phenolic resin and its preparation process. Nano copper powder and nano alumina fiber are used to modify phenolic resin in conjunction. The modified phenolic resin contains nano copper powder in 2-5 wt% and nano alumina fiber in 1-3 wt%, so that it has improved heat resistance, toughness and strength. The modified phenolic resin of the present invention is suitable for making high performance friction material products, especially wet friction material products used in the conditions of high-energy completely absorbing and / or low coolingoil circulation. In addition, the present invention provides one new method of synthesizing phenolic resin, that is nano copper catalyzed method, with low power consumption and low cost.

Owner:XI AN JIAOTONG UNIV

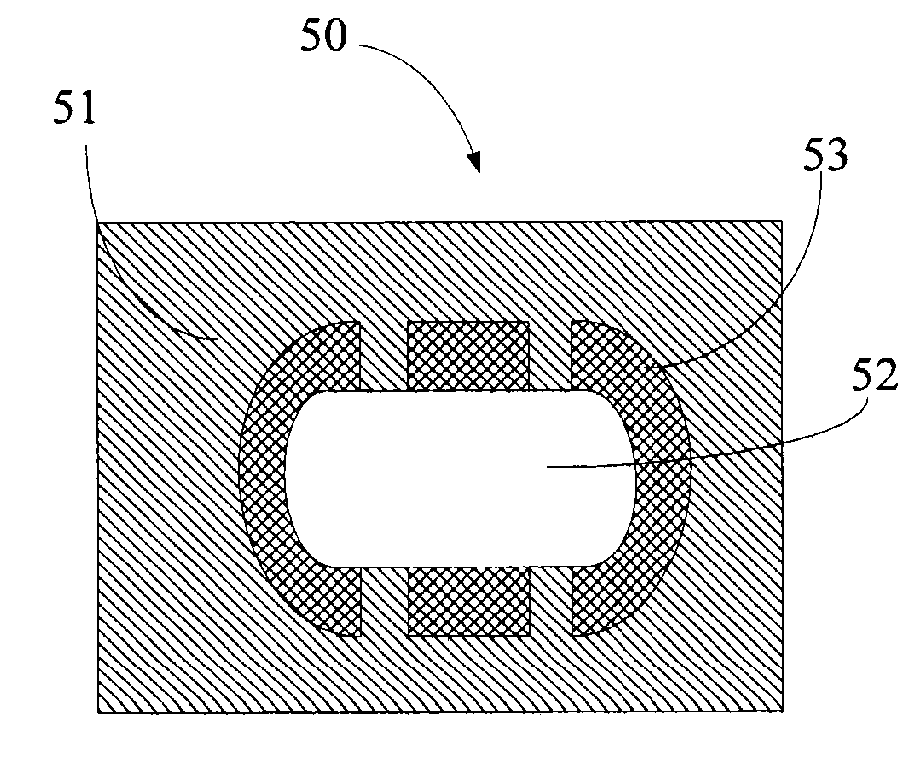

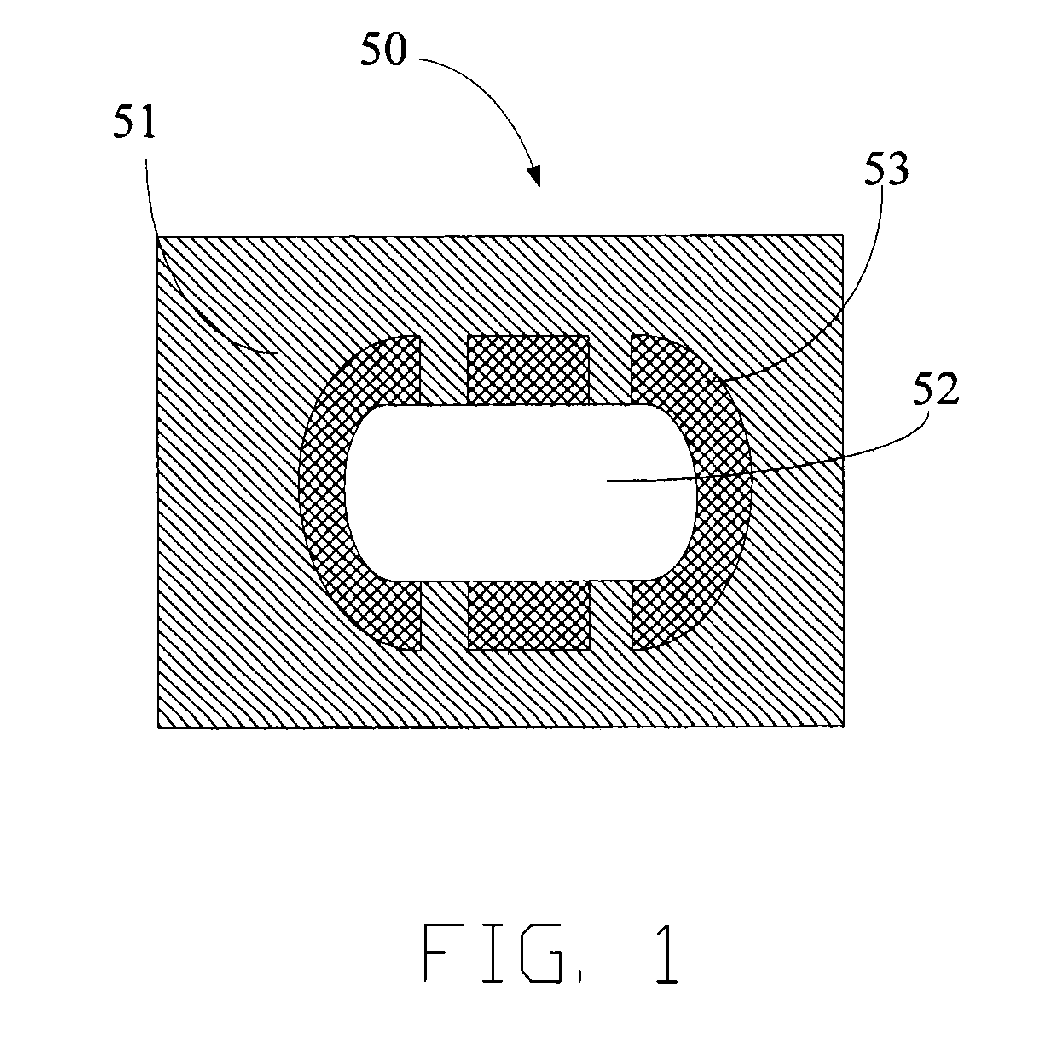

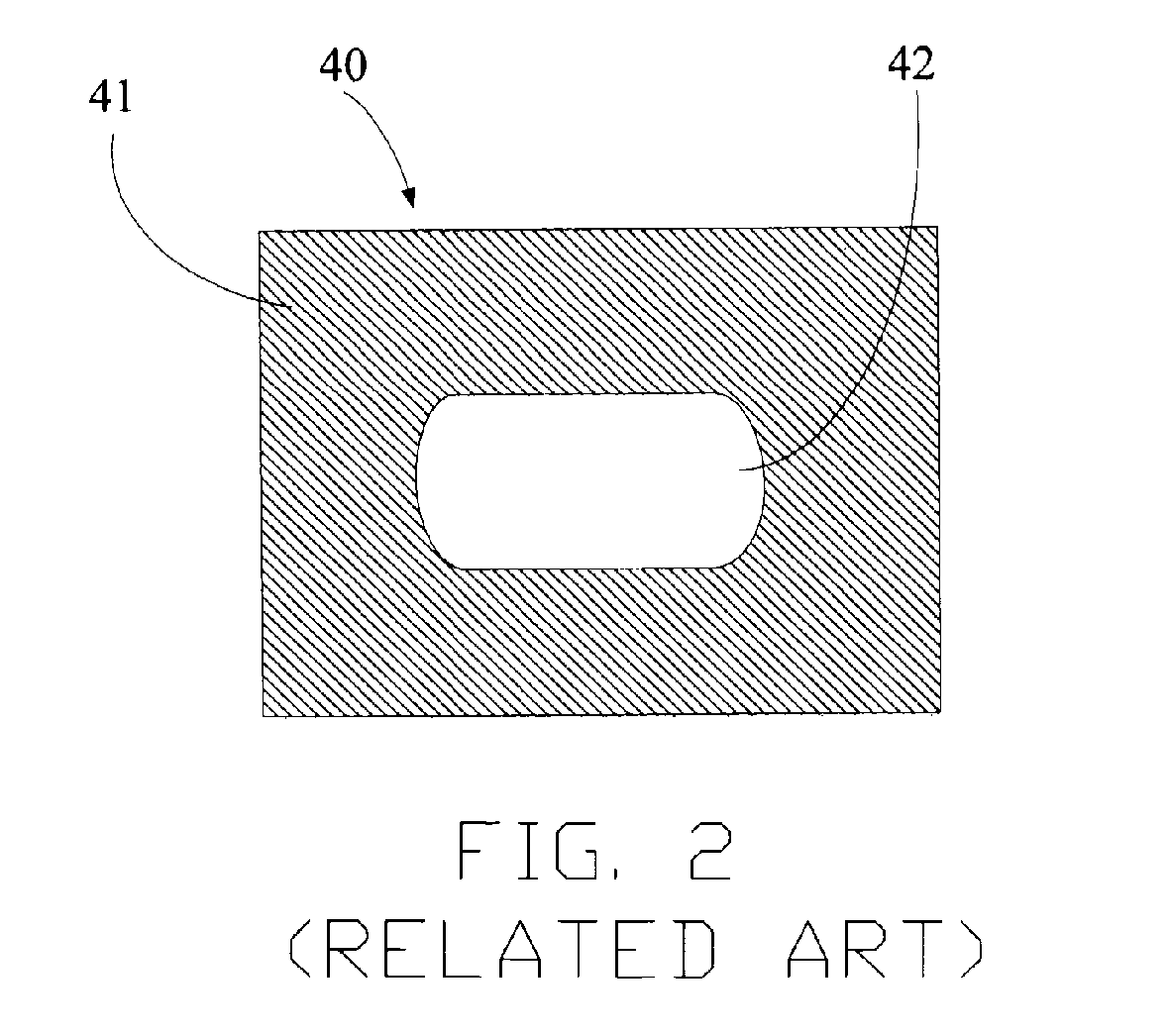

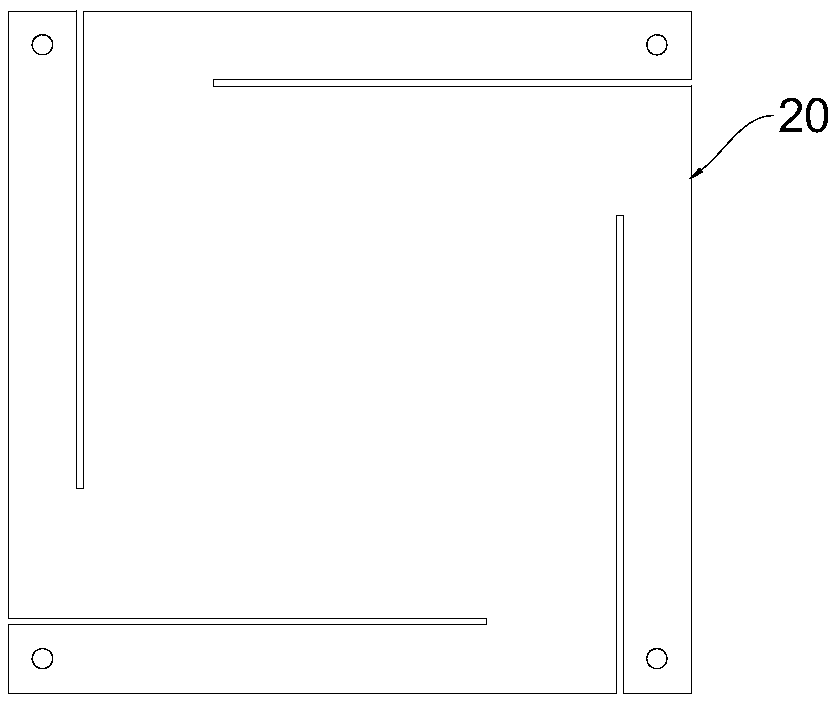

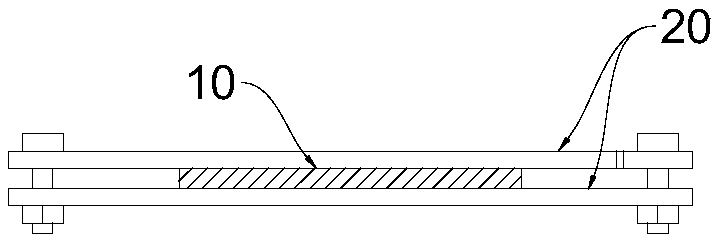

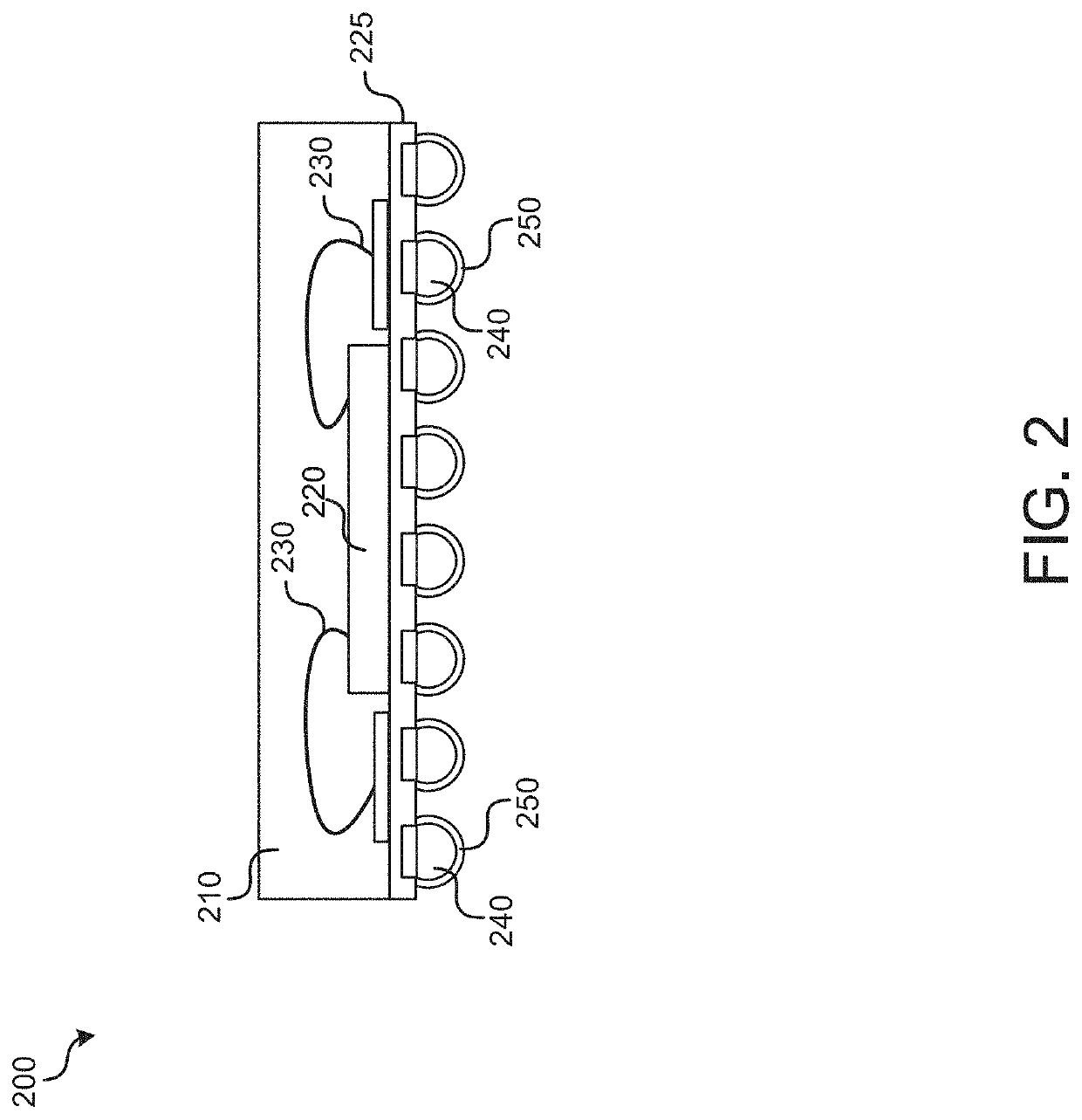

Printed circuit board

InactiveUS20070089903A1Slow down heat distributionReduce defect formationPrinted circuit aspectsPrinted circuit manufactureCopperPrinted circuit board

A printed circuit board includes a reference layer, a through hole defined in the reference layer, and a plurality of insulating areas are defined in the reference layer around the through hole. The copper around the through hole is separated by the insulating areas and forms a plurality of copper strips. The metal surface area around the through hole available for heat dissipation is reduced to slow down heat distribution. Defect formation is thus reduced when the PCB is in a reflow process.

Owner:HON HAI PRECISION IND CO LTD

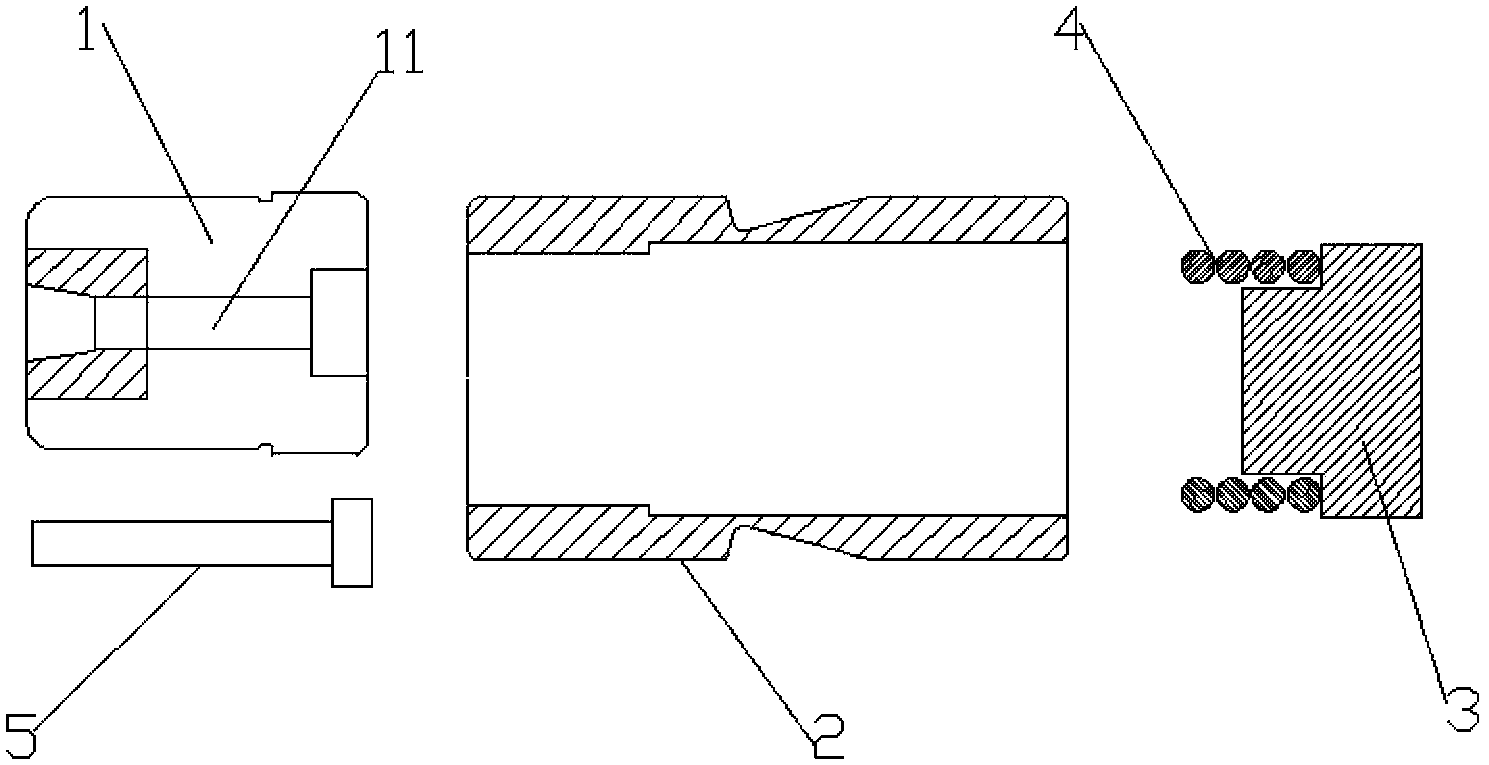

Cold heading die for engine bearing cover fastener

InactiveCN104043766AAvoid damageExtend your lifeForging/hammering/pressing machinesEngineeringFastener

The invention discloses a cold heading die for an engine bearing cover fastener. The cold heading die comprises a columnar floating stamping die and a hollow columnar sleeve shell, wherein the axial middle part of the floating stamping die is provided with a through hole; a cavity for the cold heading shaping of a bolt head part is formed in one end of the through hole; a limiting groove is formed in the other end of the through hole; the floating stamping die is divided into a stamping die shaping part and a stamping die hanging connection part in sequence along the axial outer side; the stamping die hanging connection part is located on one end back to the cavity; the axial inner side of the sleeve shell is divided into a sleeve shell hanging connection part and a sleeve shell limiting part in sequence; the sleeve shell hanging connection part is sheathed on the exterior of the stamping die shaping part; the sleeve shell limiting part is sheathed on the exterior of a stamping die sheathing part; the floating stamping die can axially and reciprocally slide for a certain distance relative to the sleeve shell; moreover, the stamping die hanging connection part can be stopped on the sleeve shell hanging connection part. By applying the cold heading die, the material content of a fastener head part can be effectively increased; the defects of the fastener head part are reduced; the product quality is improved; subsequent improvement procedures can be further reduced; moreover, the service life of the cold heading die can be prolonged, so that the production cost is further reduced.

Owner:DAJINHE FASTENER KUNSHAN

Reflective-type mask blank for EUV lithography

ActiveUS7678511B2Reduce defect formationRadiation/particle handlingNanoinformaticsLithographic artistElectrical connection

There are provided a substrate with a reflective layer and an EUV mask blank, which can prevent particles from adhering to a surface of the reflective layer or an absorbing layer, or into a reflective layer or an absorbing layer during formation thereof by eliminating electrical connection between a film formed on a front surface of the substrate and a film formed on a rear surface of the substrate.A substrate with a reflective layer, which is usable to fabricate a reflective mask blank for EUV lithography, comprising a chucking layer formed on a rear surface opposite a surface with the reflective layer formed thereon, the chucking layer serving to chuck and support the substrate by an electrostatic chuck, wherein the reflective layer has no electrical connection to the chucking layer.

Owner:ASAHI GLASS CO LTD

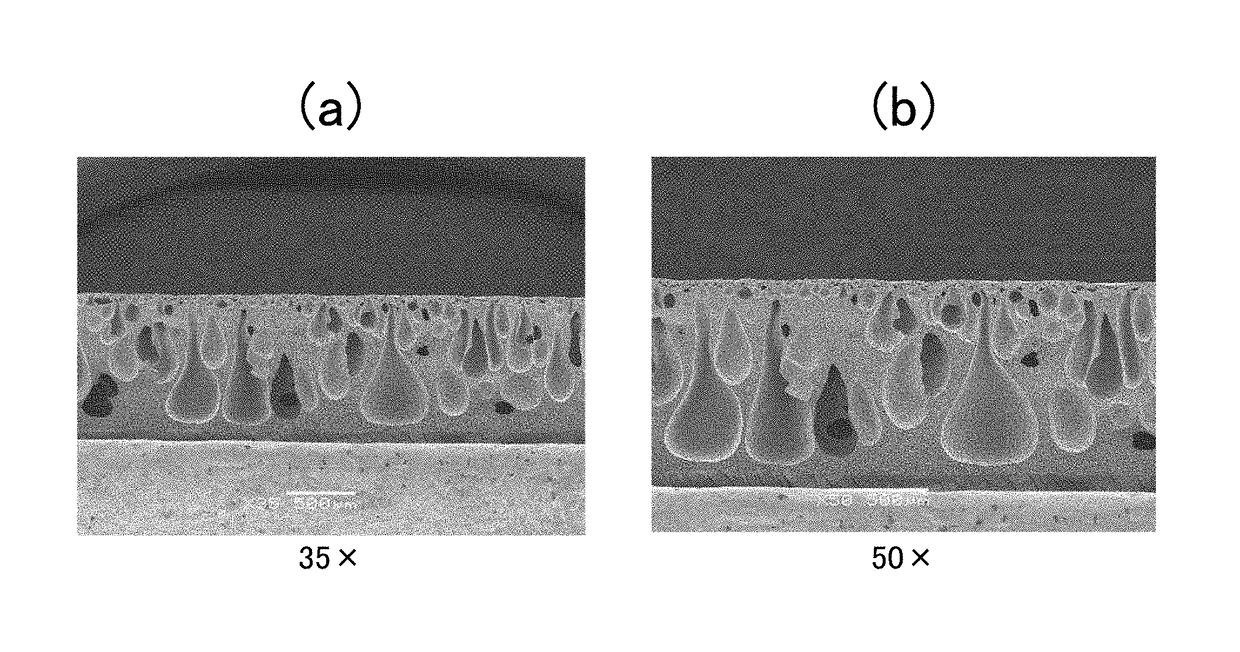

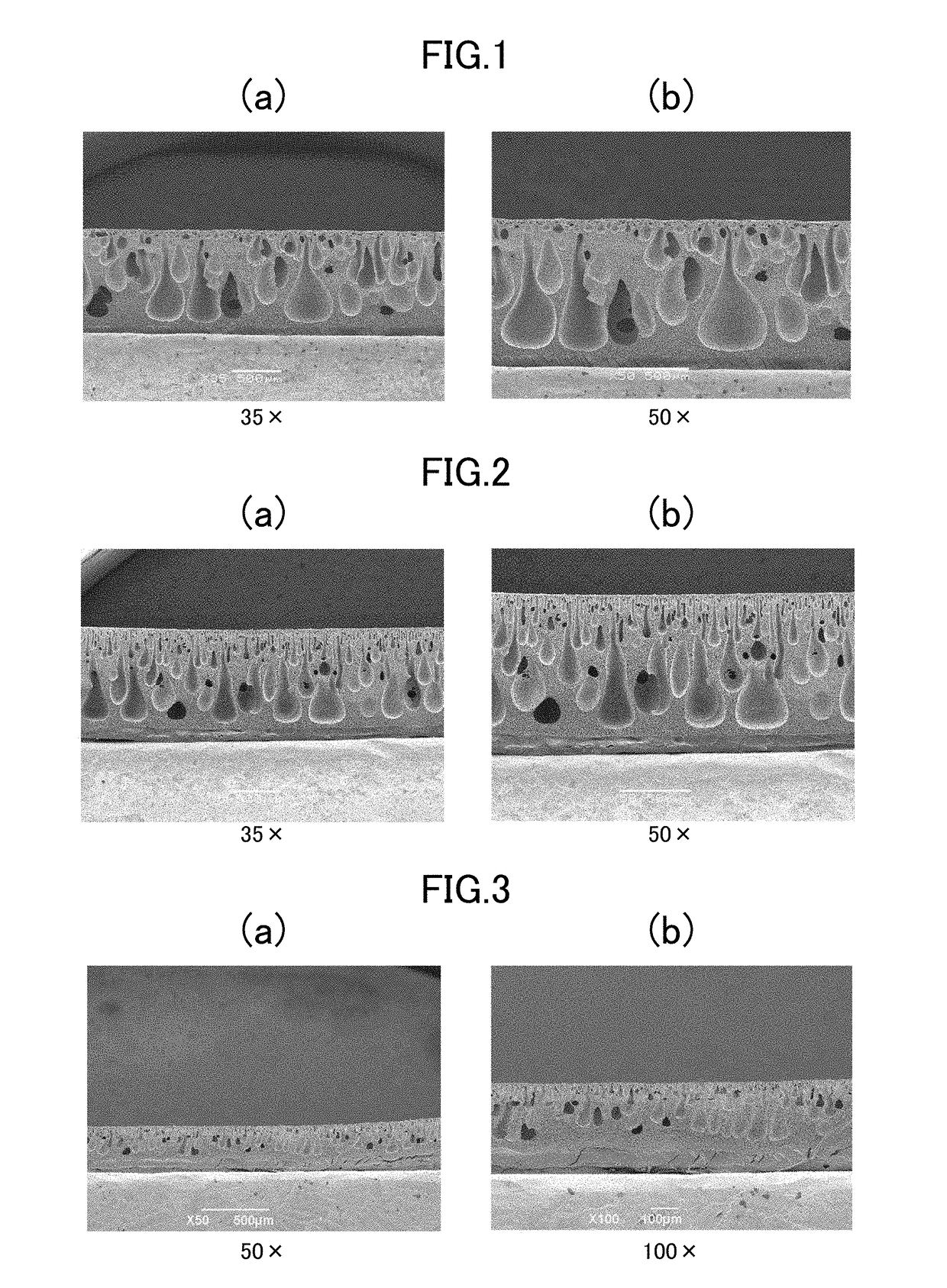

Polishing pad and method for producing polishing pad

ActiveUS10071460B2Reduce formationStable film formationAbrasion apparatusLapping toolsSolventPolymer chemistry

Owner:FUJIBO HLDG

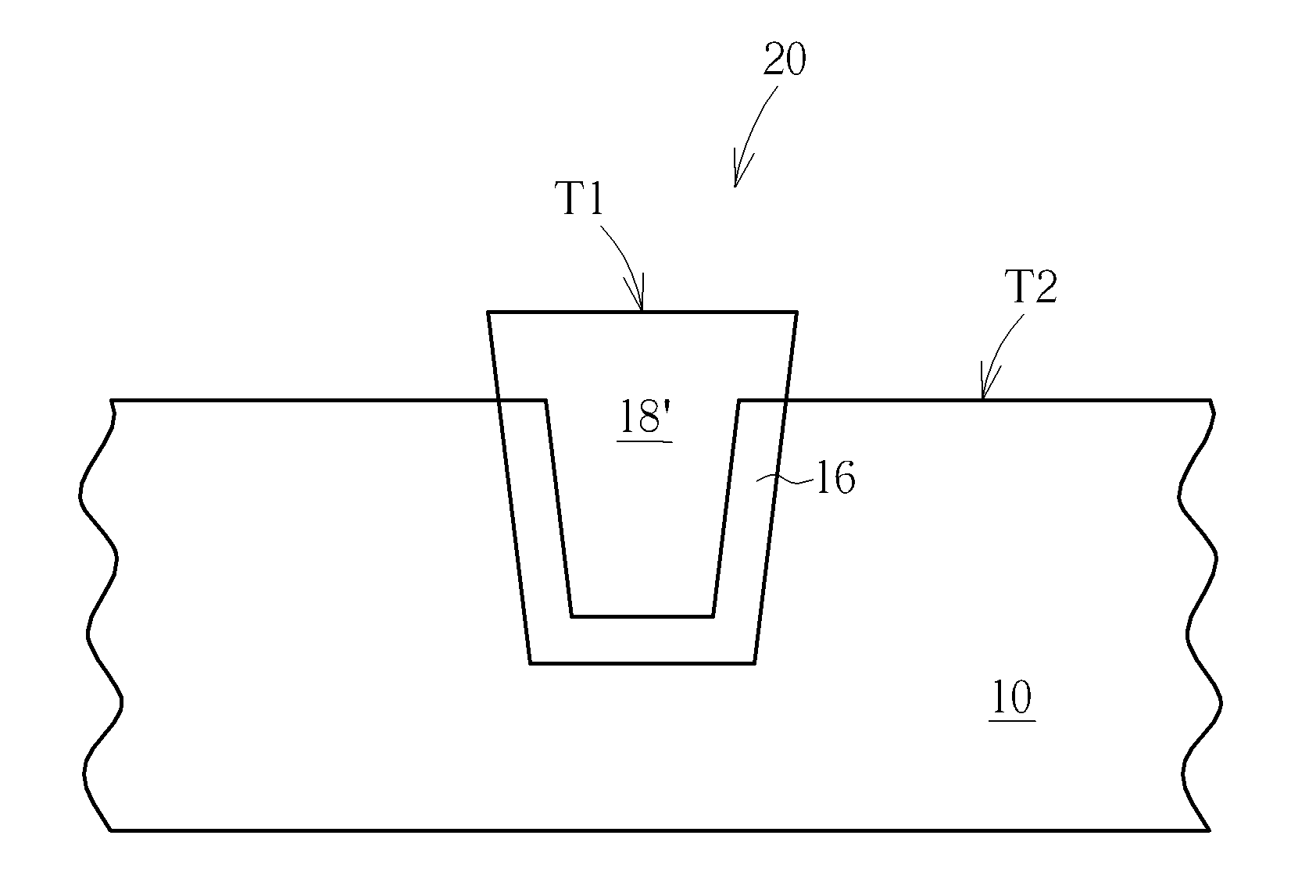

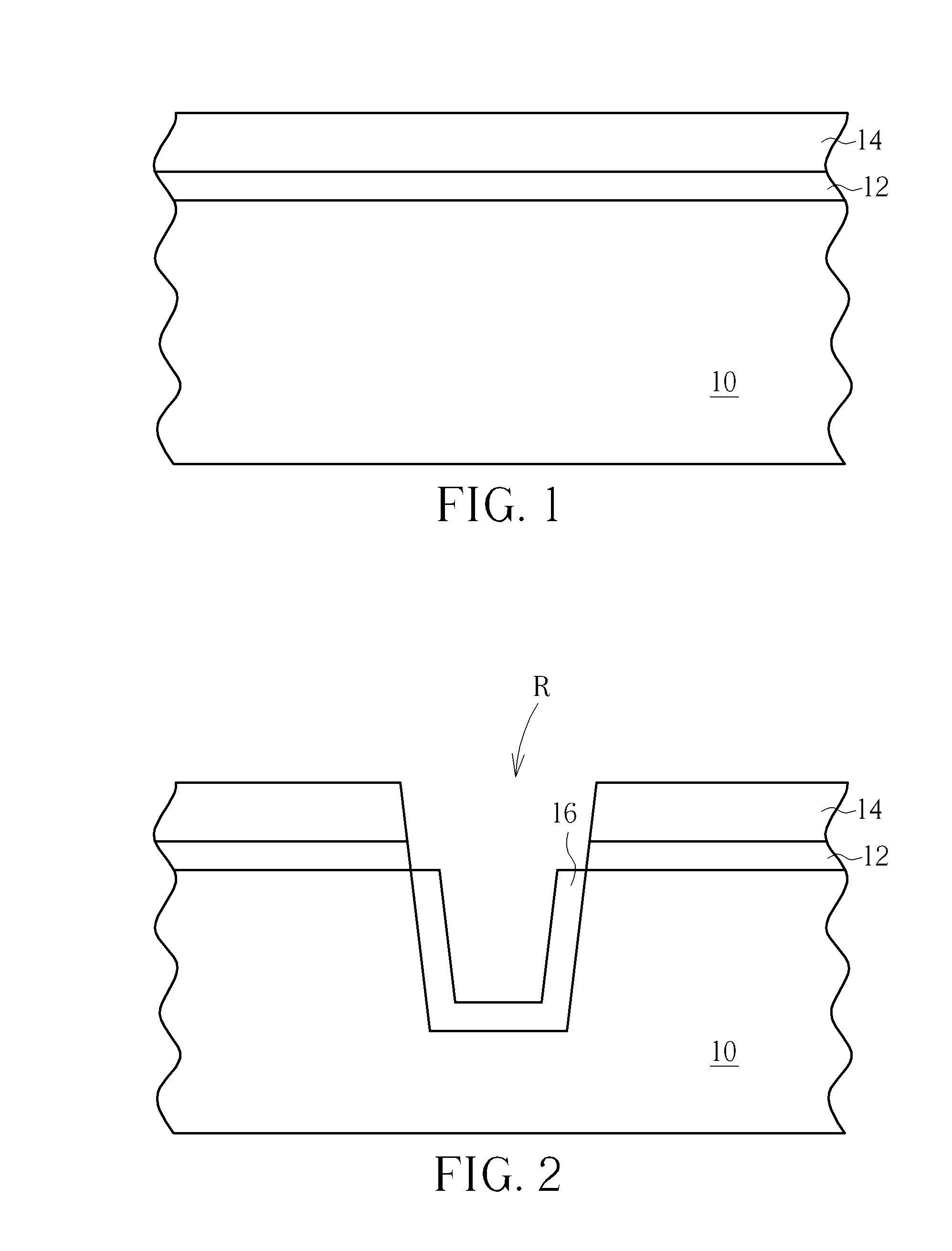

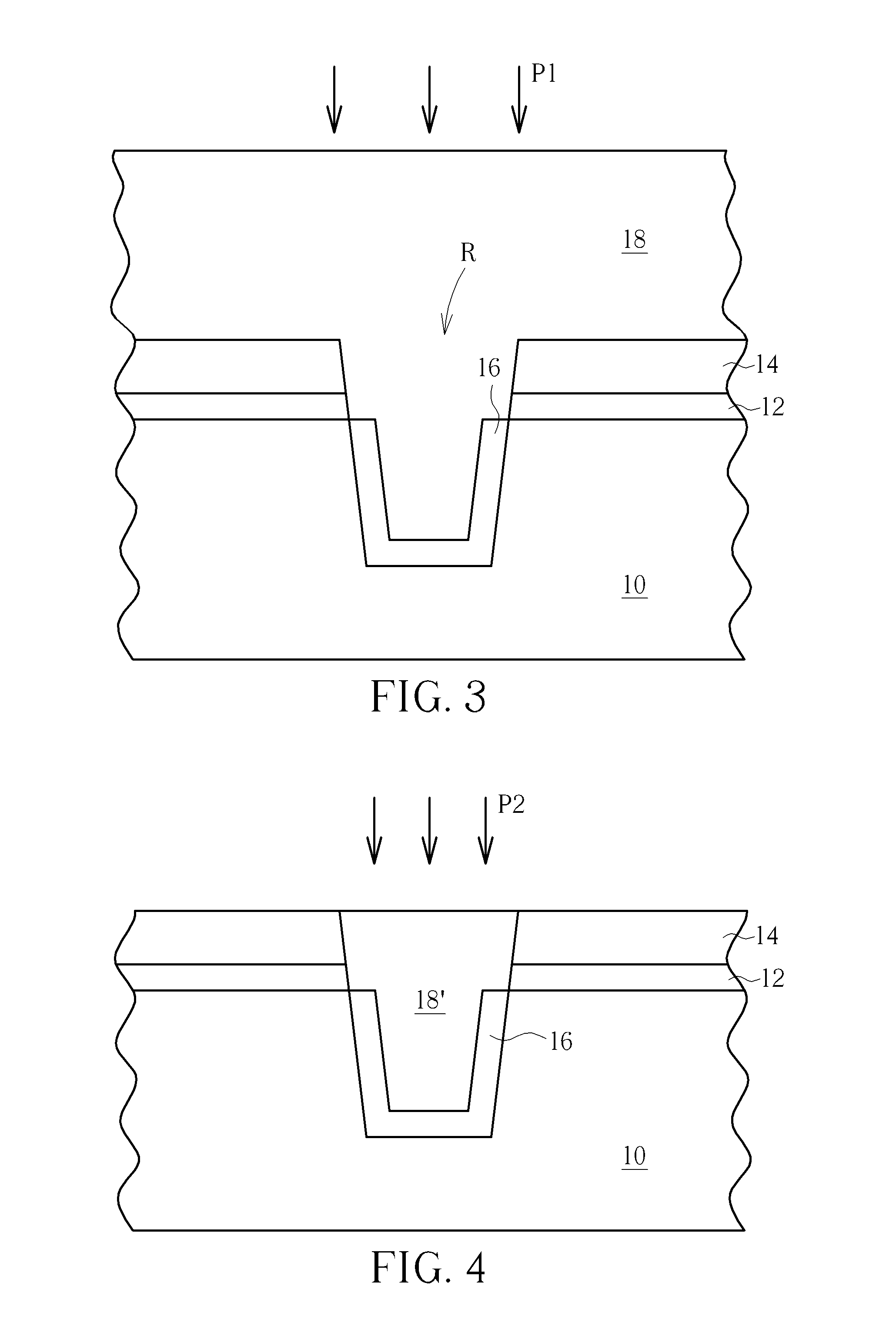

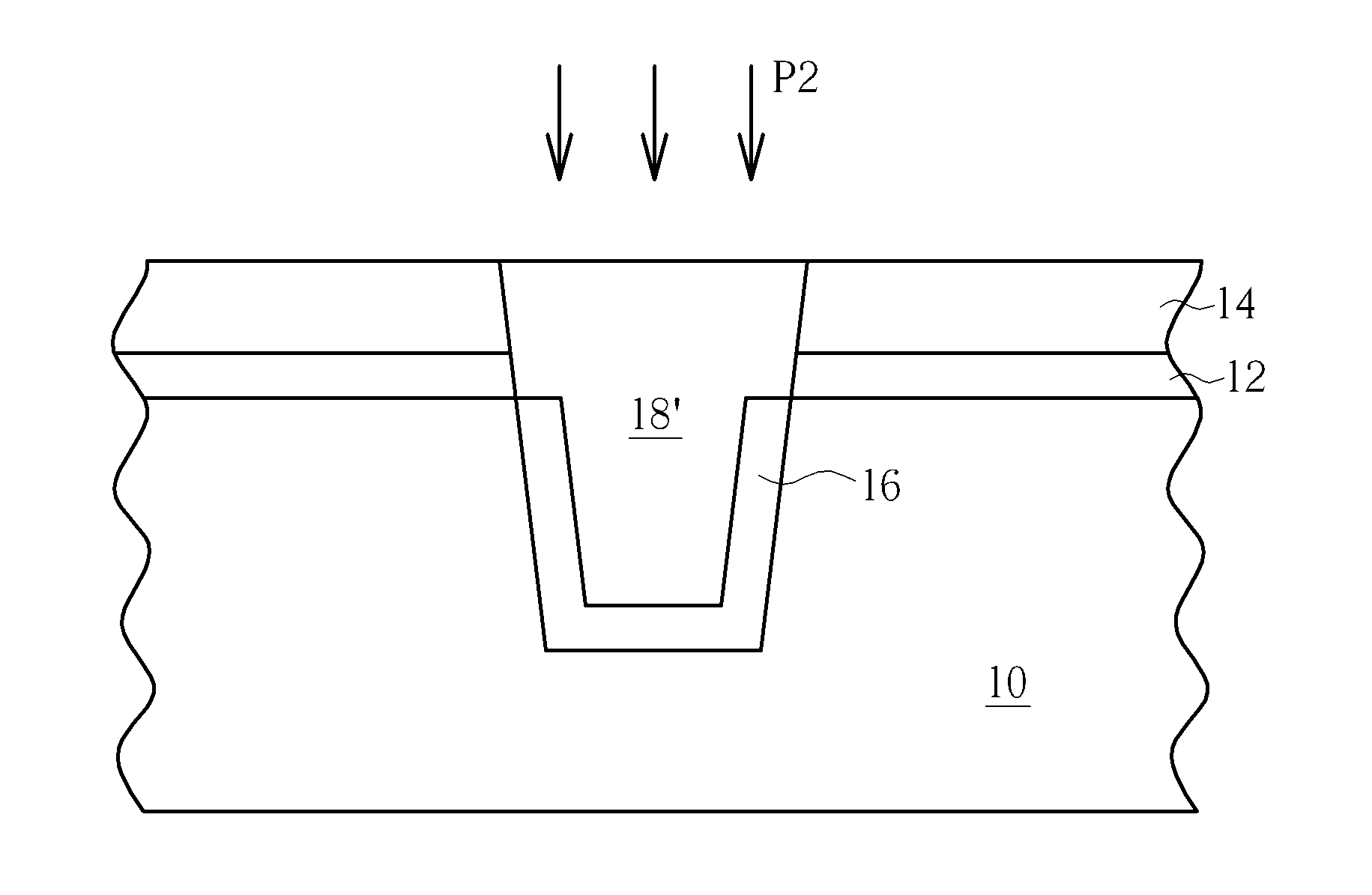

Method of fabricating dielectric layer and shallow trench isolation

ActiveUS8927388B2Reduce defect formationExcellent gap fillingSemiconductor/solid-state device manufacturingOxygen plasmaCompound (substance)

A method of fabricating a dielectric layer includes the following steps. At first, a dielectric layer is formed on a substrate, and a chemical mechanical polishing (CMP) process is performed on the dielectric layer. Subsequently, a surface treatment process is performed on the dielectric layer after the chemical mechanical polishing process, and the surface treatment process includes introducing an oxygen plasma.

Owner:UNITED MICROELECTRONICS CORP

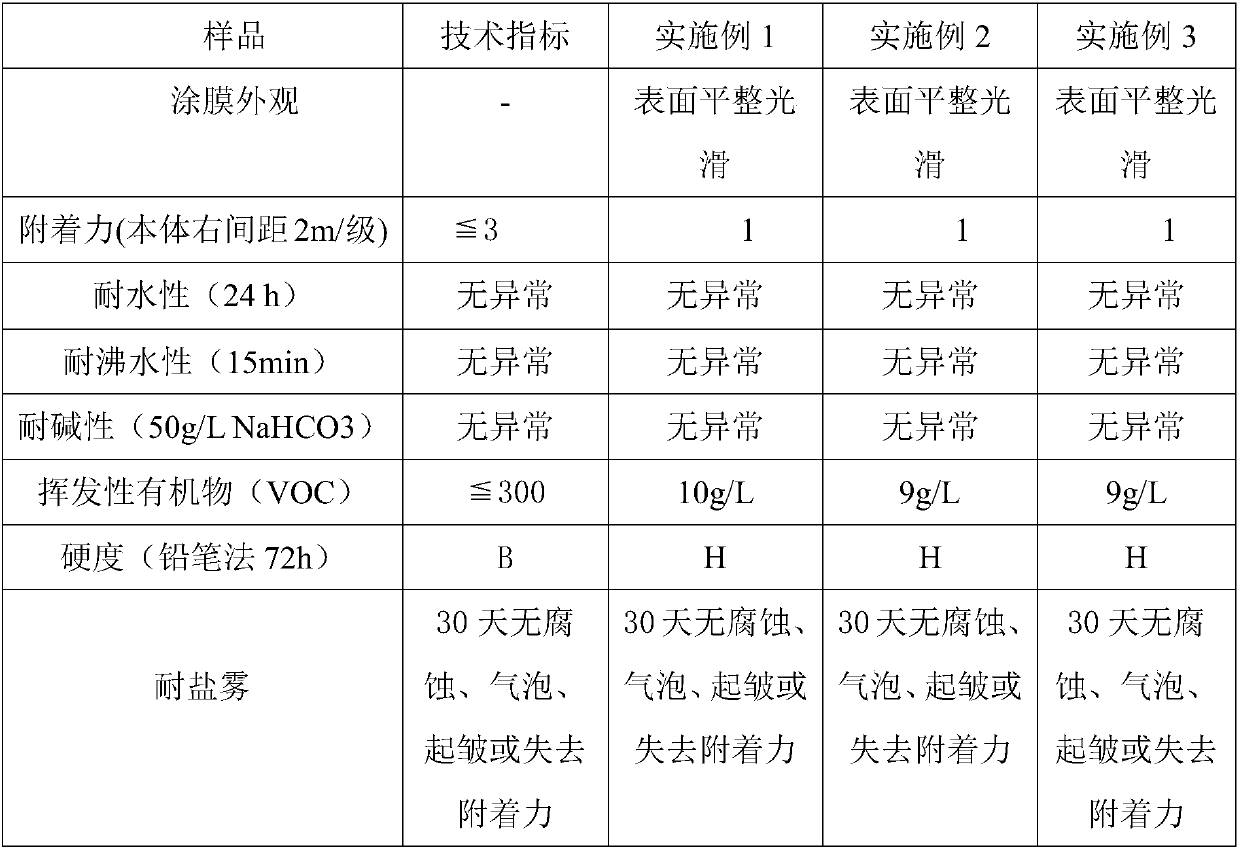

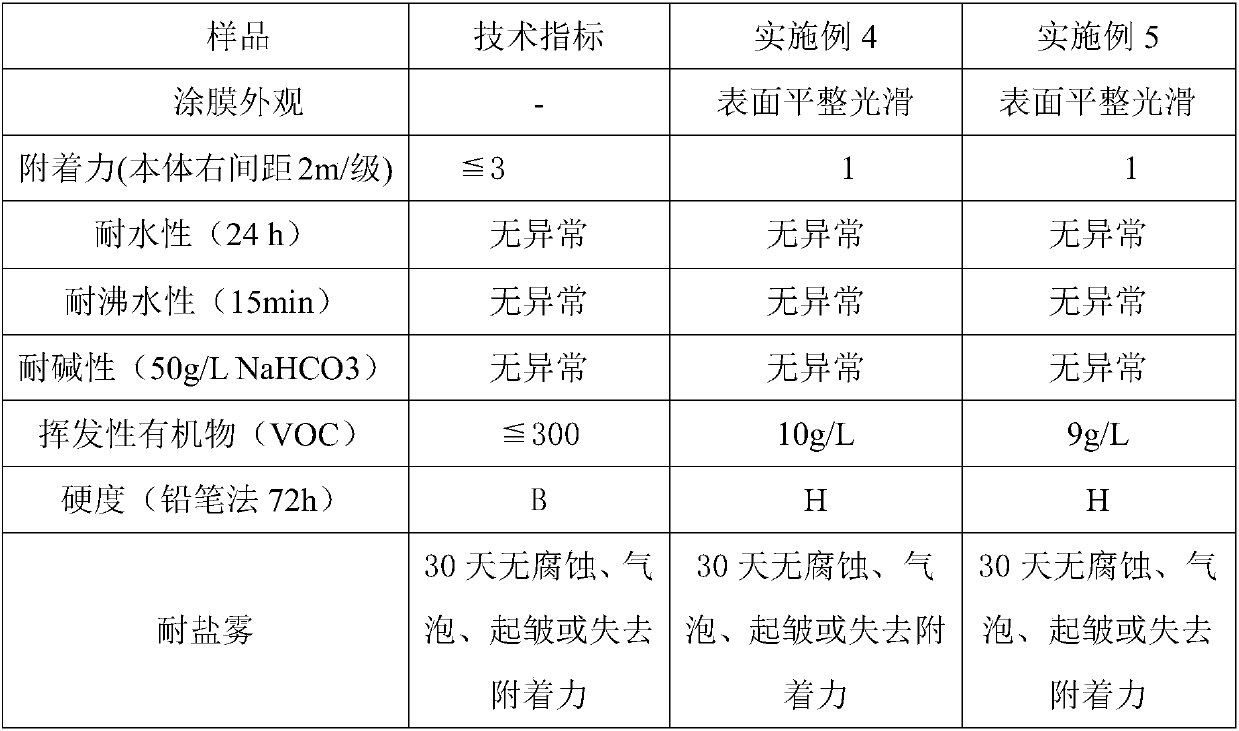

Waterborne acrylic resin coating with chloride ion corrosion resistance and preparation method of waterborne acrylic resin coating

The invention provides a waterborne acrylic resin coating with chloride ion corrosion resistance and a preparation method of the waterborne acrylic resin coating, and relates to the technical field ofcoatings. The waterborne acrylic resin coating with the chloride ion corrosion resistance is prepared from the following raw materials: waterborne acrylic resin, nano calcium carbonate, nano-siliconnitride powder, nano-alumina powder, sodium dodecyl benzene sulfonate, nicotine, an anti-settling agent, tributyl citrate, filler, aids and deionized water. The waterborne acrylic resin coating with the chloride ion corrosion resistance, disclosed by the invention, has the advantages of excellent adhesion, waterproof property, acid and alkali resistance, chlorine ion corrosion resistance, better comprehensive performance, wide application prospect and capability of prolonging the service life of a product.

Owner:GUANGDONG VALSPAR CHEM IND

Ocean heavy anti-corrosion epoxy aluminum-nickel-rich nano-coating and preparation method thereof

ActiveCN103254725AImprove corrosion resistanceHigh content of nano aluminum powderAnti-corrosive paintsEpoxy resin coatingsLacquerFirming agent

The invention discloses an ocean heavy anti-corrosion epoxy aluminum-nickel-rich nano-coating, which is composed of components A and B with a mass ratio of 18:1 and comprises the following components in parts by mass: 14-18 parts of epoxy resin, 3-6 parts of hydroxyl acrylic resin, 125-145 parts of nano-aluminum powder, 25-30 parts of nano-nickel powder, 3-6 parts of talcum powder, 2-4 parts of barium sulfate, 3-5 parts of an anti-settling auxiliary agent, 1-2 parts of a dispersing auxiliary agent, and 10-13 parts of a solvent, wherein the component B comprises the following components with contents in parts by mass: 50-60 parts of a curing agent and 40-50 parts of a solvent. The invention also discloses a preparation method of the coating. By adopting the scheme of the invention, the nano-aluminum powder content in a lacquer film is high, the cost is low, the process is simple, and no special equipment is needed. According to the invention, the prepared coating has strong binding force with a matrix, also has relatively good binding force with various other additional coatings, is excellent in corrosion-resistant performance in an ocean atmospheric environment, and long in service life, and is a heavy anti-corrosion coating applicable to iron and steel constructions such as a drilling platform and a bridge in an ocean atmospheric environment.

Owner:SHANDONG LONGQUAN PIPELINE ENG

Ocean heavy anti-corrosion epoxy aluminum-rich nano-coating and preparation method thereof

ActiveCN103254735AGood effectEffective dispersionAnti-corrosive paintsEpoxy resin coatingsAcrylic resinLacquer

The invention discloses an ocean heavy anti-corrosion epoxy aluminum-rich nano-coating, which is composed of components A and B with a mass ratio of 18:1 and comprises the following components in parts by mass: 14-18 parts of epoxy resin, 3-6 parts of hydroxyl acrylic resin, 125-145 parts of nano-aluminum powder, 3-6 parts of talcum powder, 2-4 parts of barium sulfate, 3-5 parts of an anti-settling auxiliary agent, 1-2 parts of a dispersing auxiliary agent, and 10-13 parts of a solvent, wherein the component B comprises the following components with contents in parts by mass: 50-60 parts of a curing agent and 40-50 parts of a solvent. The invention also discloses a preparation method of the coating. By adopting the scheme of the invention, the nano-aluminum powder content in a lacquer film is high, the cost is low, the process is simple, and no special equipment is needed. According to the invention, the prepared coating has strong binding force with a matrix, also has relatively good binding force with various other additional coatings, is excellent in corrosion-resistant performance in an ocean atmospheric environment, and long in service life, and is a heavy anti-corrosion coating applicable to iron and steel constructions such as a drilling platform and a bridge in an ocean atmospheric environment.

Owner:SHANDONG LONGQUAN PIPELINE ENG

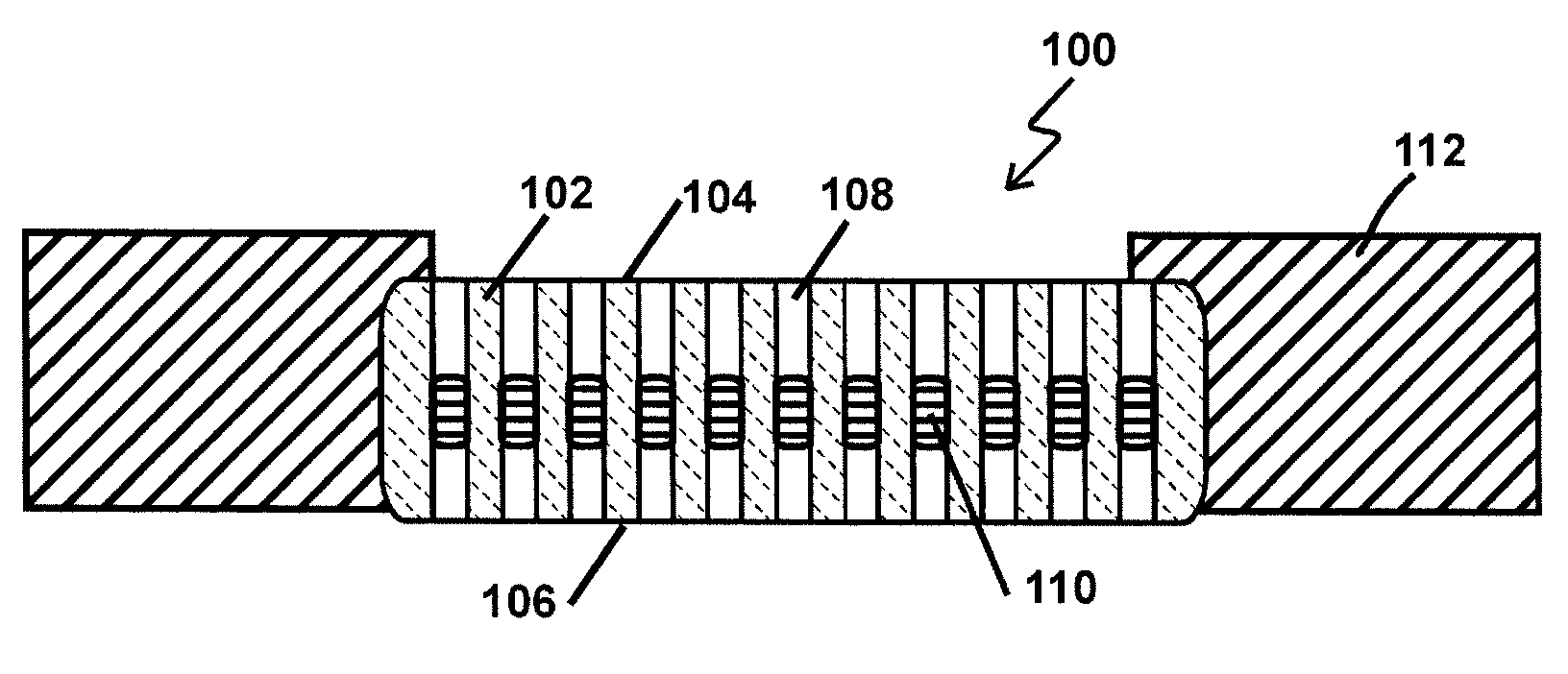

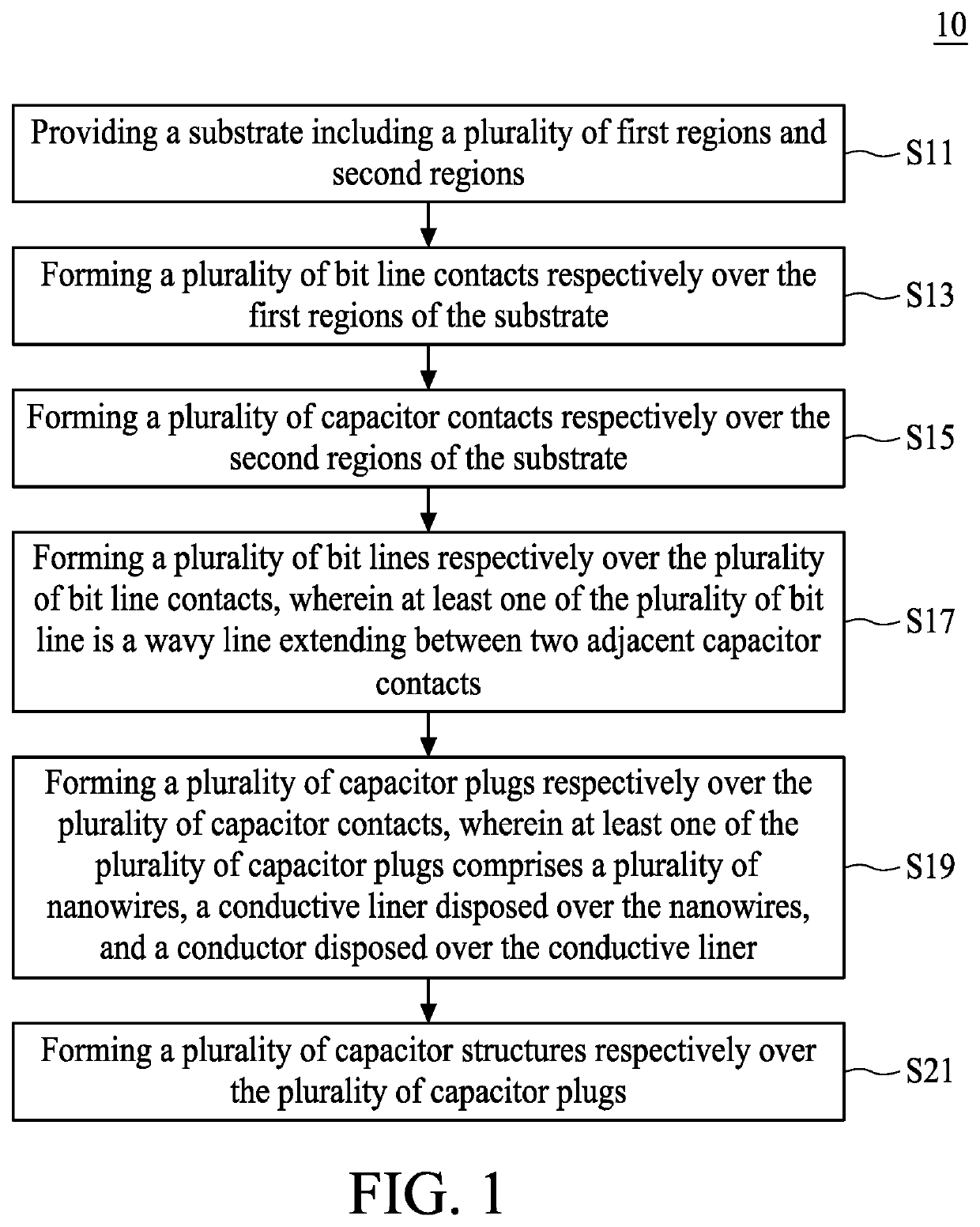

Semiconductor device with nanowire capacitor plugs and method for fabricating the same

ActiveUS20210091088A1Reduce defect formationIncrease productionTransistorSolid-state devicesCapacitanceBit line

The present application discloses a semiconductor device with nanowire plugs and a method for fabricating the semiconductor device. The semiconductor device includes a substrate having first regions and second regions; a plurality of capacitor contacts positioned over the second regions, at least one of the capacitor contacts having a neck portion and a head portion over the neck portion, wherein an upper width of the head portion is larger than an upper width of the neck portion; a plurality of bit line contacts positioned over the first regions and a plurality of bit lines positioned over the bit line contacts; a plurality of capacitor plugs disposed over the capacitor contacts, wherein at least one of the plurality of capacitor plugs includes a plurality of nanowires, a conductive liner disposed over the nanowires, and a conductor disposed over the conductive liner; and a plurality of capacitor structures disposed respectively over the capacitor plugs.

Owner:NAN YA TECH

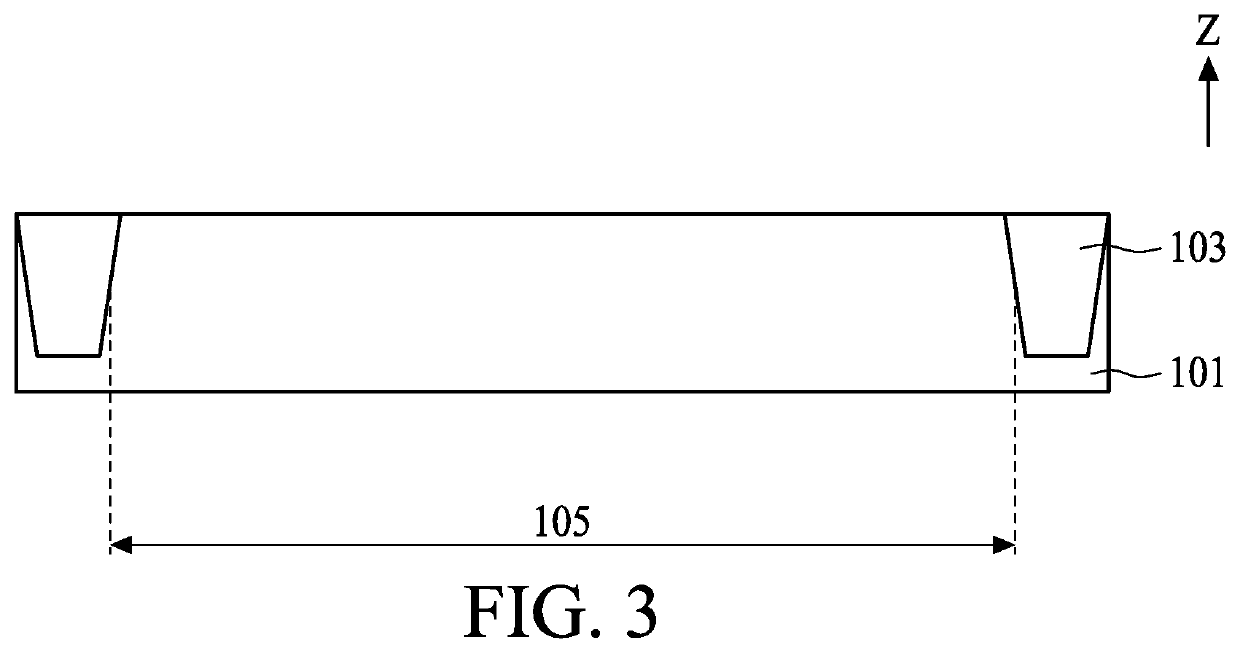

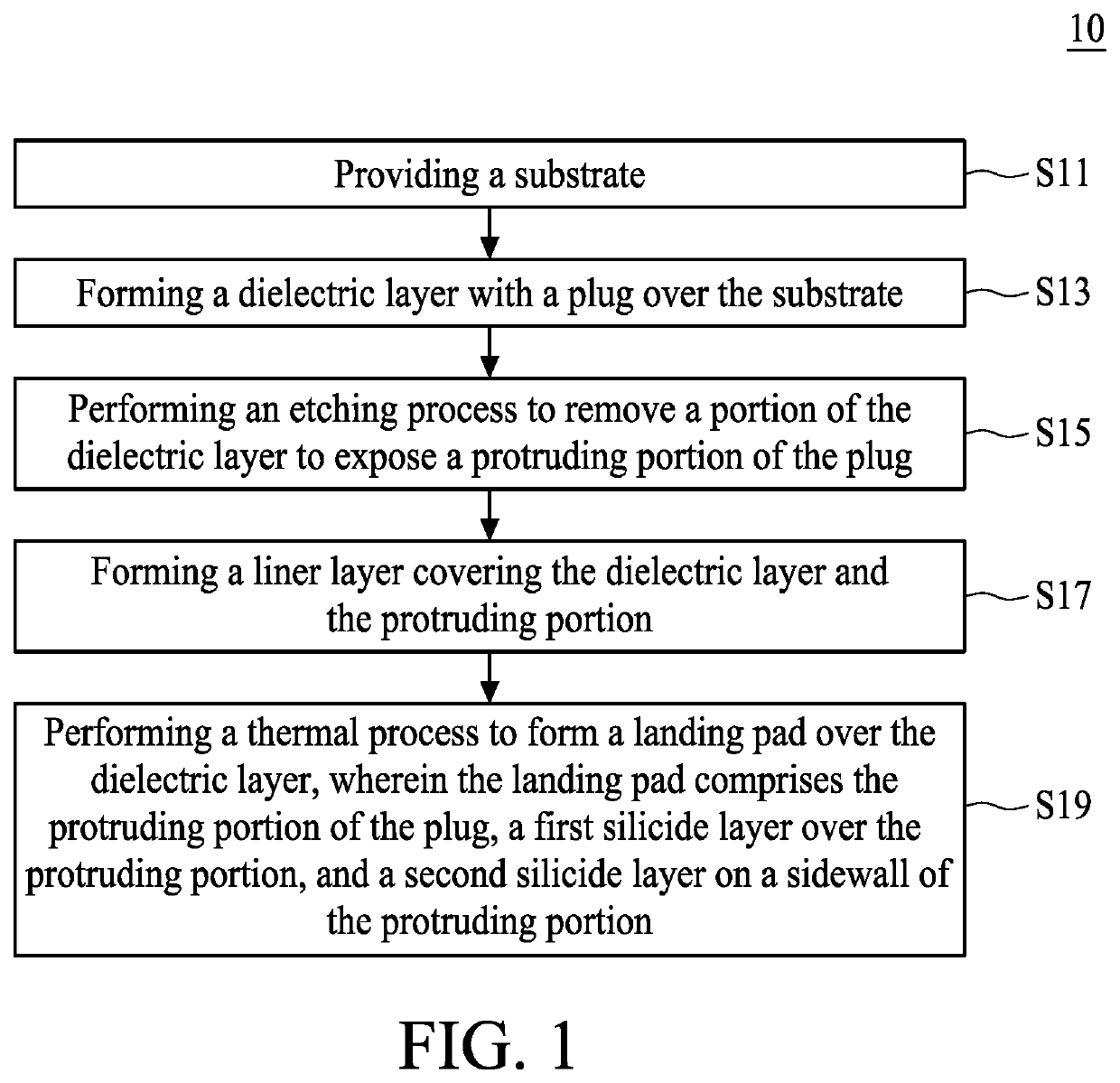

Semiconductor device with self-aligned landing pad and method for fabricating the same

ActiveUS11121137B1Reduce defect formationImprove yieldTransistorSolid-state devicesSelf alignmentMechanical engineering

The present application discloses a semiconductor device with a self-aligned landing pad and a method for fabricating the semiconductor device. The semiconductor device includes a substrate, a dielectric layer disposed over the substrate, a plug disposed in the dielectric layer, and a self-aligned landing pad disposed over the dielectric layer. The method includes: providing a substrate; forming a dielectric layer with a plug over the substrate; performing an etching process to remove a portion of the dielectric layer to expose a protruding portion of the plug; forming a liner layer covering the dielectric layer and the protruding portion; and performing a thermal process to form a landing pad over the dielectric layer in a self-aligned manner. The self-aligned landing pad comprises a protruding portion of the plug, a first silicide layer disposed over the protruding portion, and a second silicide layer disposed on a sidewall of the protruding portion.

Owner:NAN YA TECH

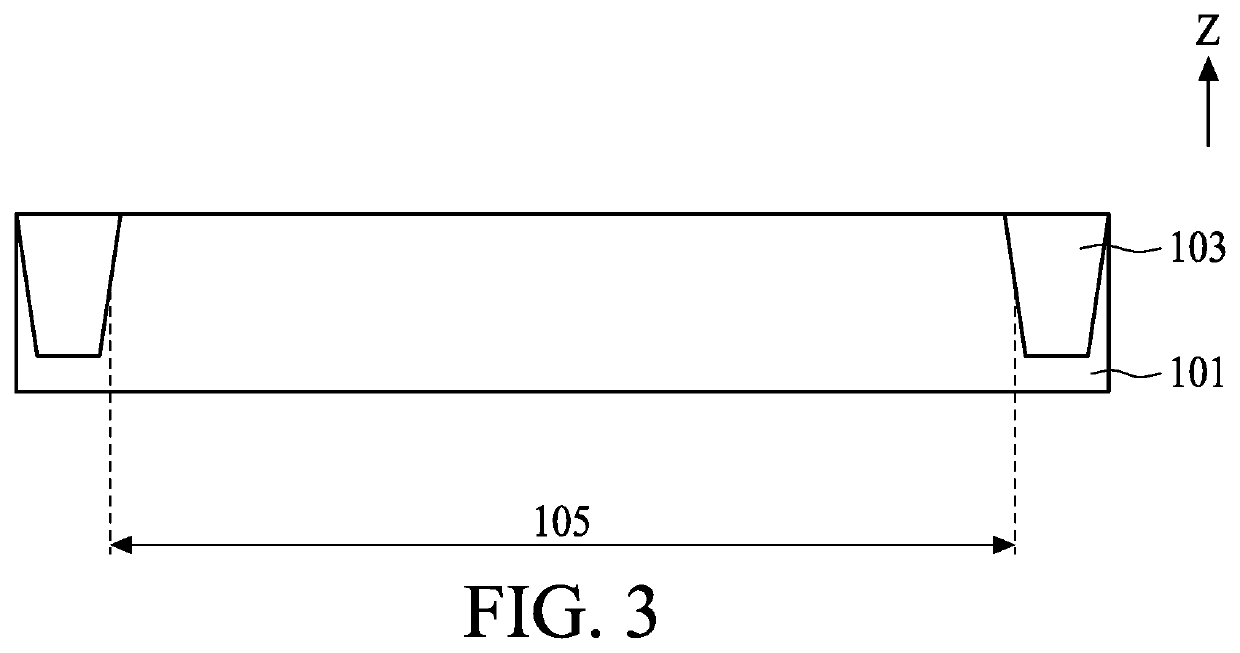

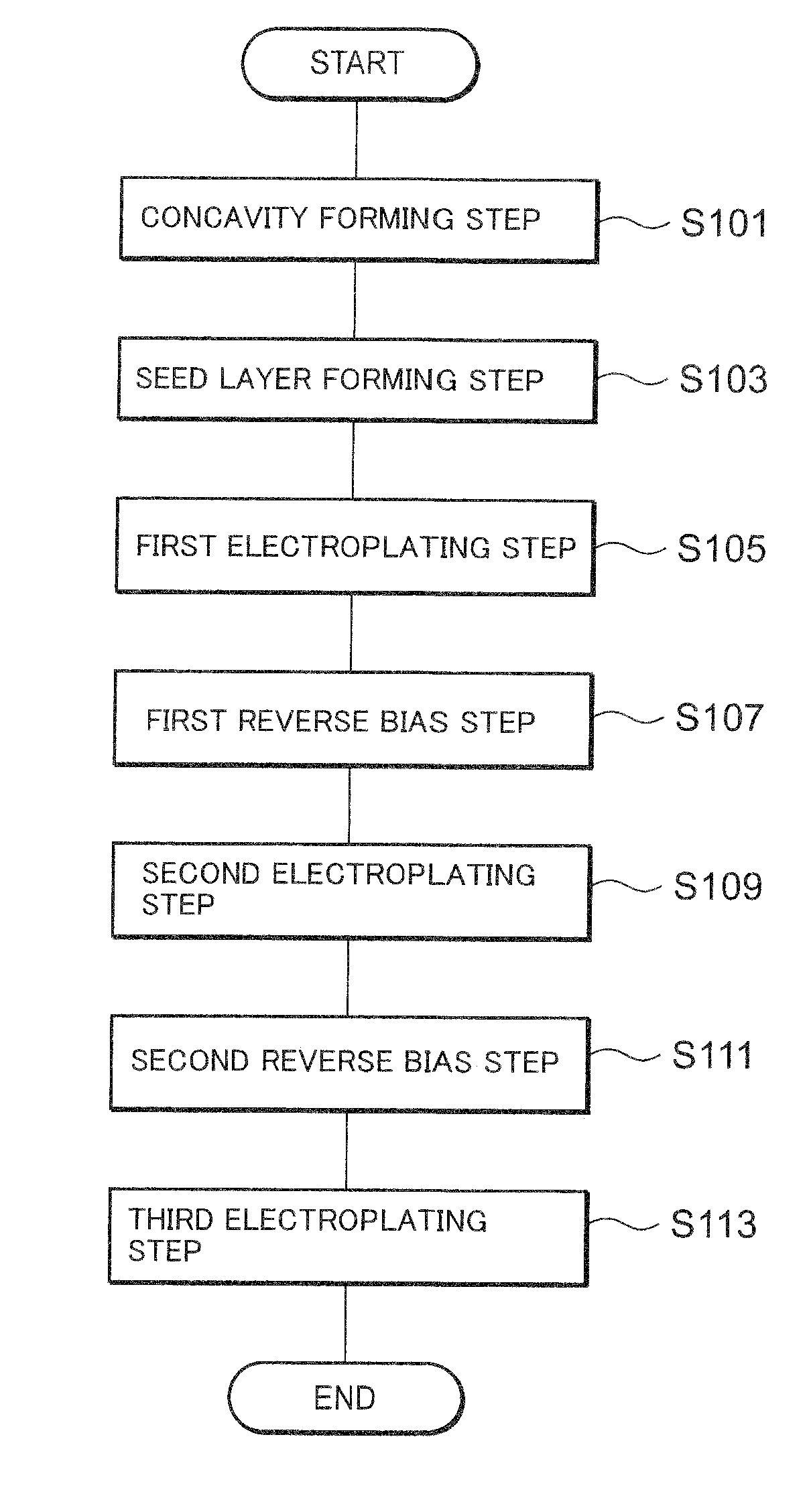

Method of manufacturing semiconductor device to decrease defect number of plating film

InactiveUS20080283404A1Film quality becomes less-preciseIncrease the number ofSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical polarityEngineering

A method for manufacturing a semiconductor device is provided which includes performing an electroplating step to fill concavities formed on a substrate. The electroplating step further includes: performing a first electroplating step; performing a first reverse bias step; performing a second electroplating step; performing a second reverse bias step; and a third electroplating step. The polarity of the first and the second reverse bias steps is different from that of the first electroplating step. A difference between the third current density and the fourth current density is larger than a difference between the first current density and the second current density.

Owner:RENESAS ELECTRONICS CORP

Flexible piezoelectric composite film and preparation method thereof

The invention discloses a flexible piezoelectric composite film and a preparation method thereof, and belongs to the technical field of composite material preparation. In the invention, nano-SiO2 particles are added to PVDF, crystalline phase transformation is promoted by adopting a high-rate uniaxial tensioning method, the content of beta phase in the PVDF material is increased, then two sides ofa film are coated with conductive silver paste electrodes, and the material is polarized at a high voltage and thus the material hs excellent piezoelectric property. The preparation method disclosedby the invention has high operability and is easy to control, and the prepared composite film product has good quality.

Owner:SOUTHWEAT UNIV OF SCI & TECH

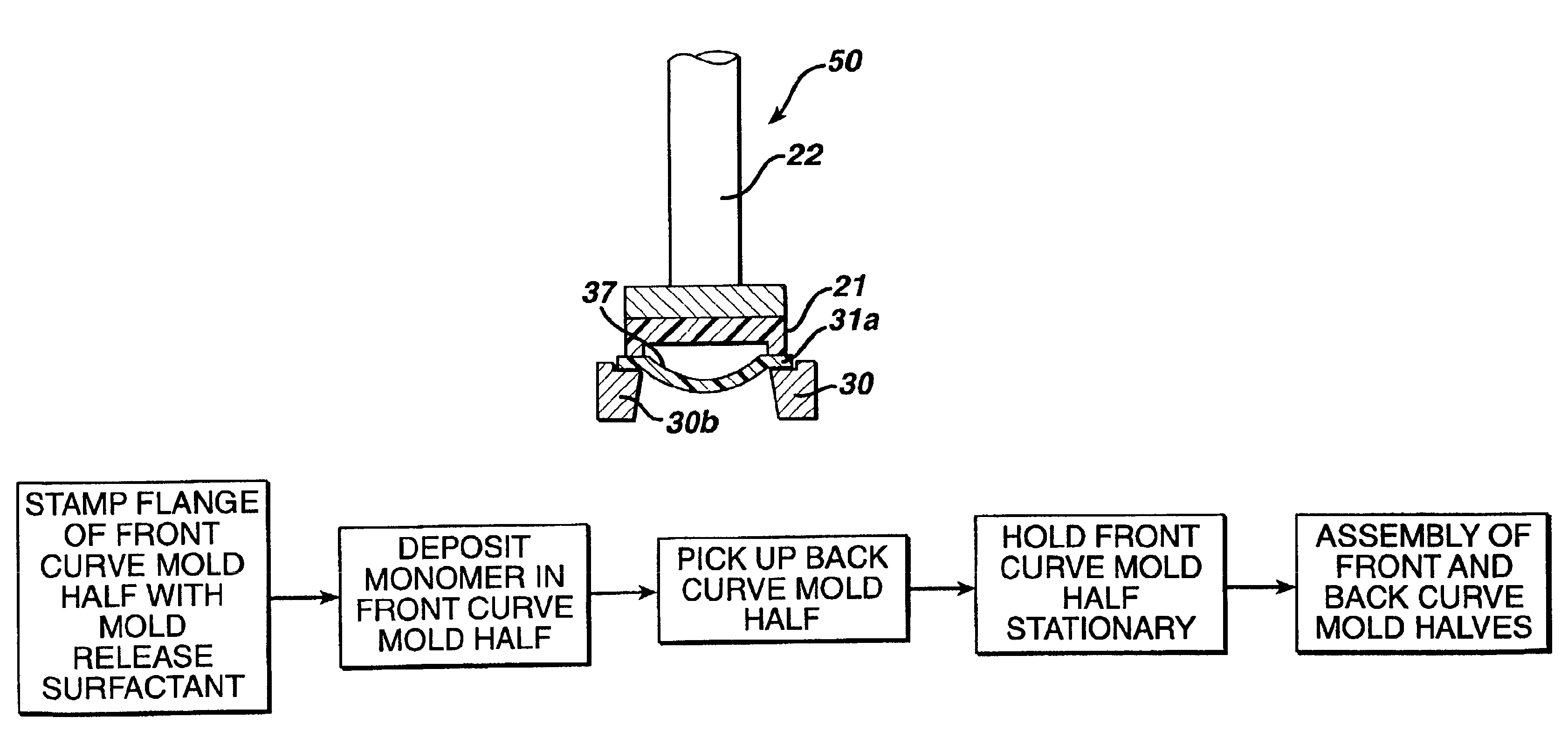

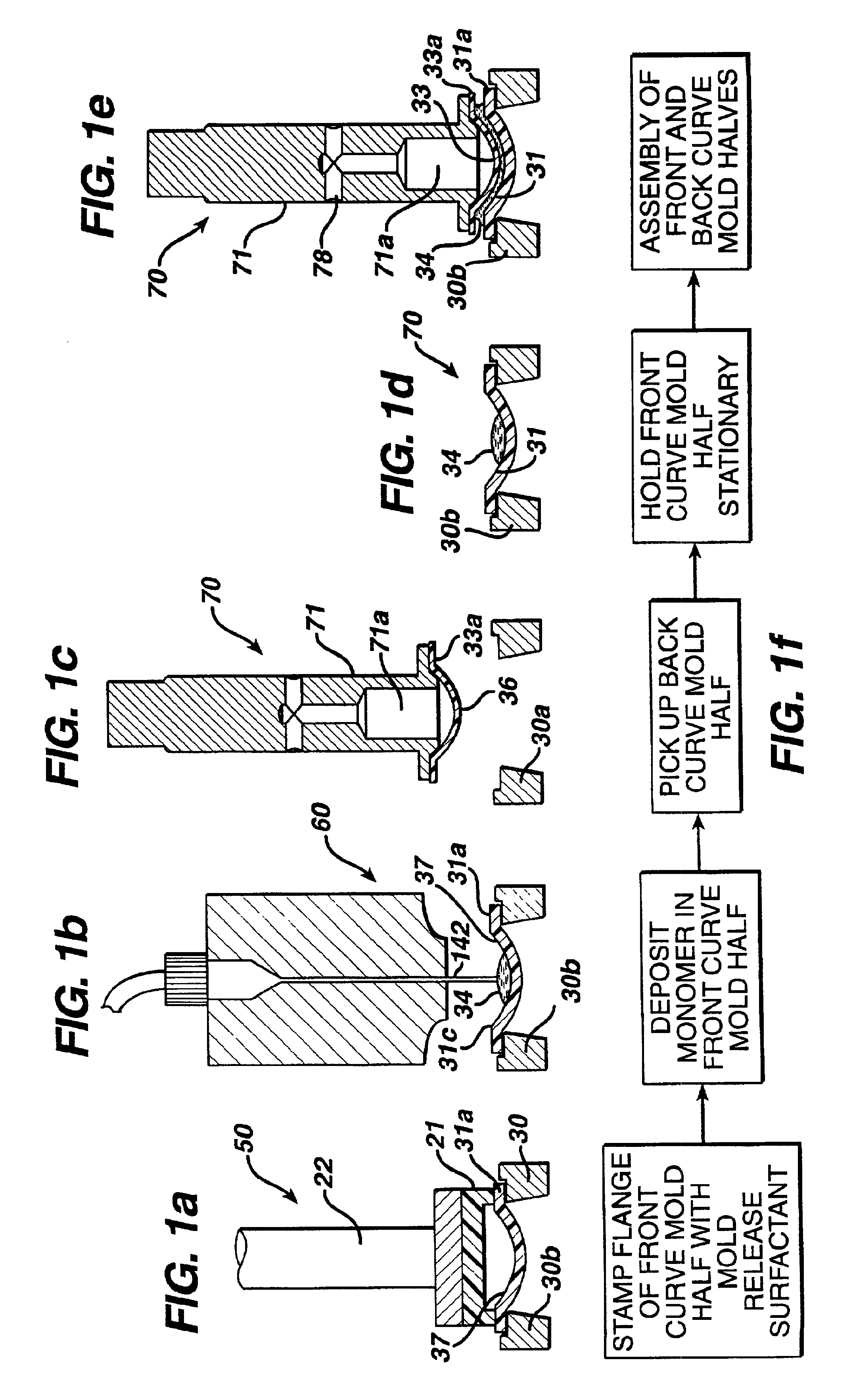

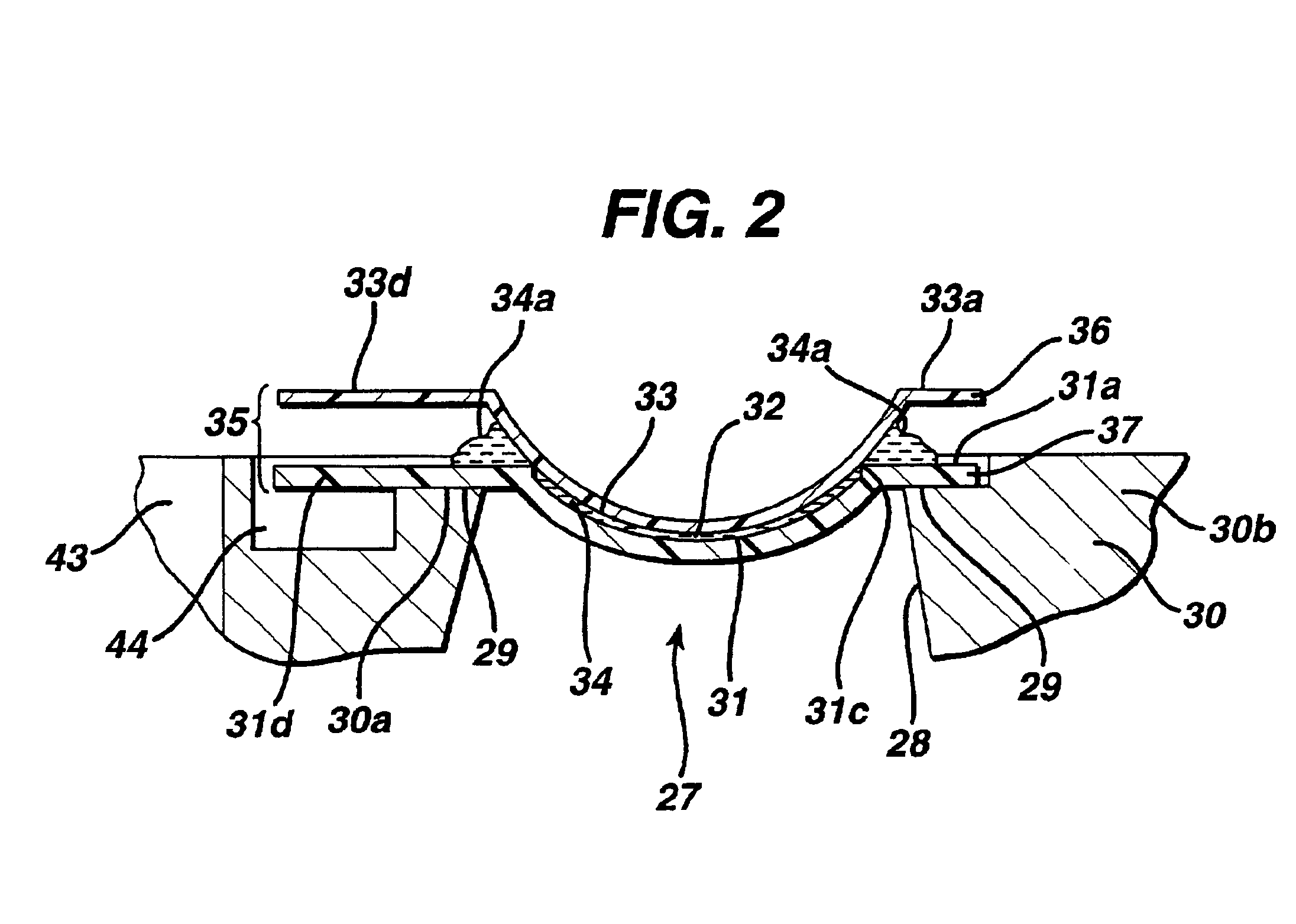

Method and apparatus for contact lens mold assembly

InactiveUS7008570B2Reduce defect formationOther chemical processesConfectioneryBiomedical engineeringContact lens

This invention provides an apparatus and method for assembling first and second mold parts having contact lens forming surfaces, wherein said first mold part has a reaction mixture on said contact lens forming surface, said apparatus comprising movement preventing means which prevents said first mold part from moving while said second mold part is controllably moved from a first position wherein said second mold part is not in contact with said reaction mixture on said first mold part to a position wherein the majority of said contact lens forming surface of said second mold part has been wetted by said reaction mixture on said first mold part.

Owner:JOHNSON & JOHNSON VISION CARE INC

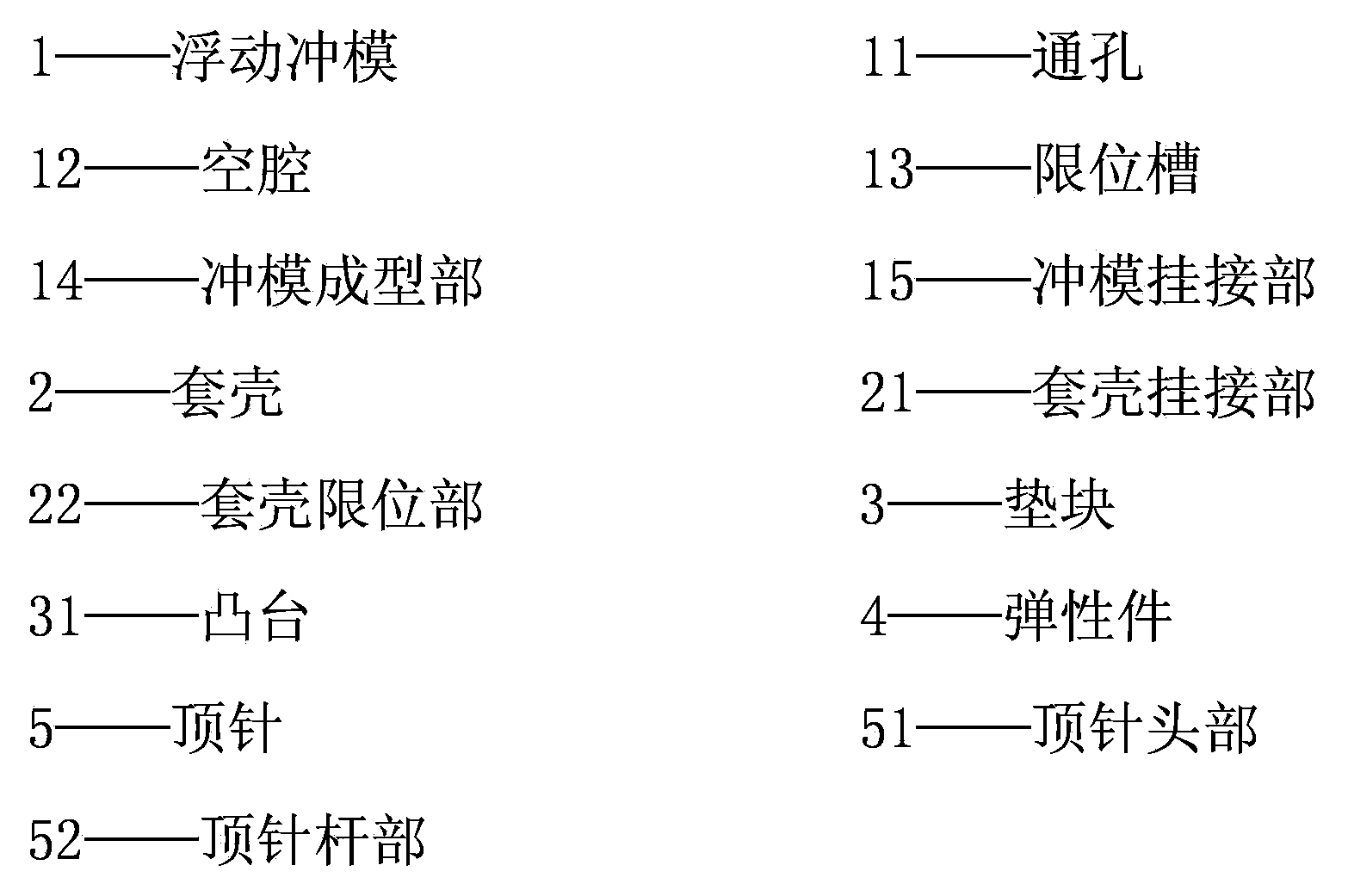

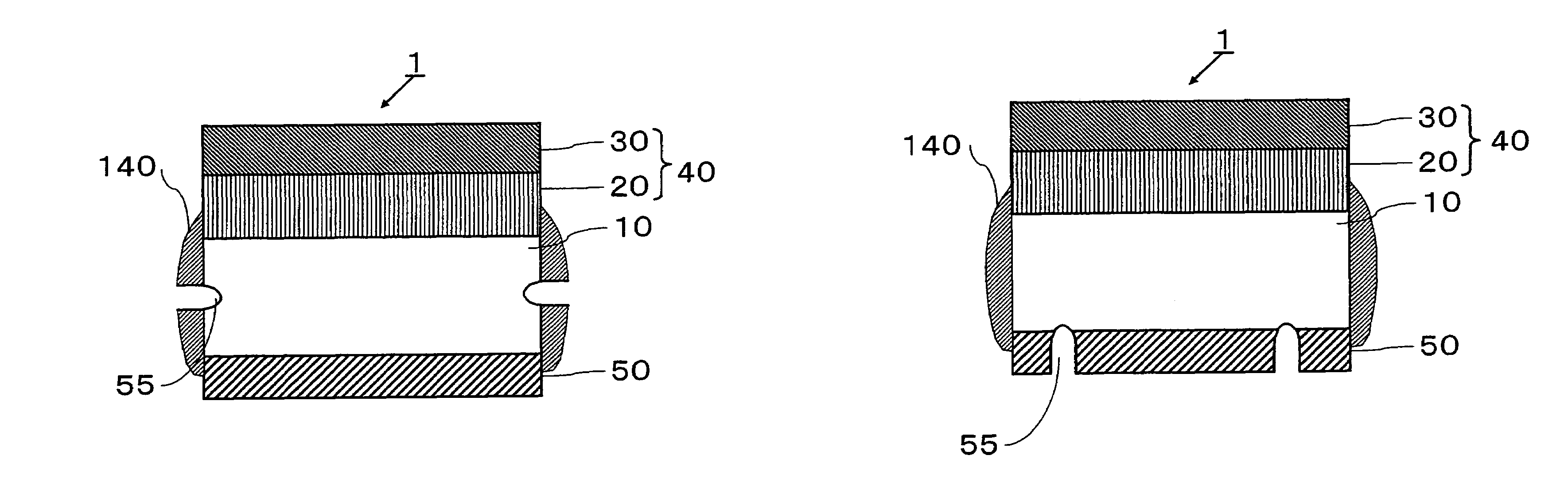

Method for manufacturing semiconductor device

ActiveUS7772098B2Reduce defect formationReduce hardnessLiquid surface applicatorsElectric discharge tubesEngineeringSemiconductor

On one face of a semiconductor wafer 1 having a first face (principal face) 1a and a second face (rear face) 1b, a protection film 2 is formed. When allowing the semiconductor wafer 1 to be attracted onto an attracting face of an electrostatic chuck 6 which is heated to 400° C. or more, the semiconductor wafer 1 is attracted onto the attracting face via the protection film 2. While heating the semiconductor wafer 1 to 400° C. or more, an ion implantation is performed for the face of the semiconductor wafer 1 on which the protection film 2 is not formed. Thereafter, the protection film 2 is removed from the semiconductor wafer 1.

Owner:PANASONIC CORP

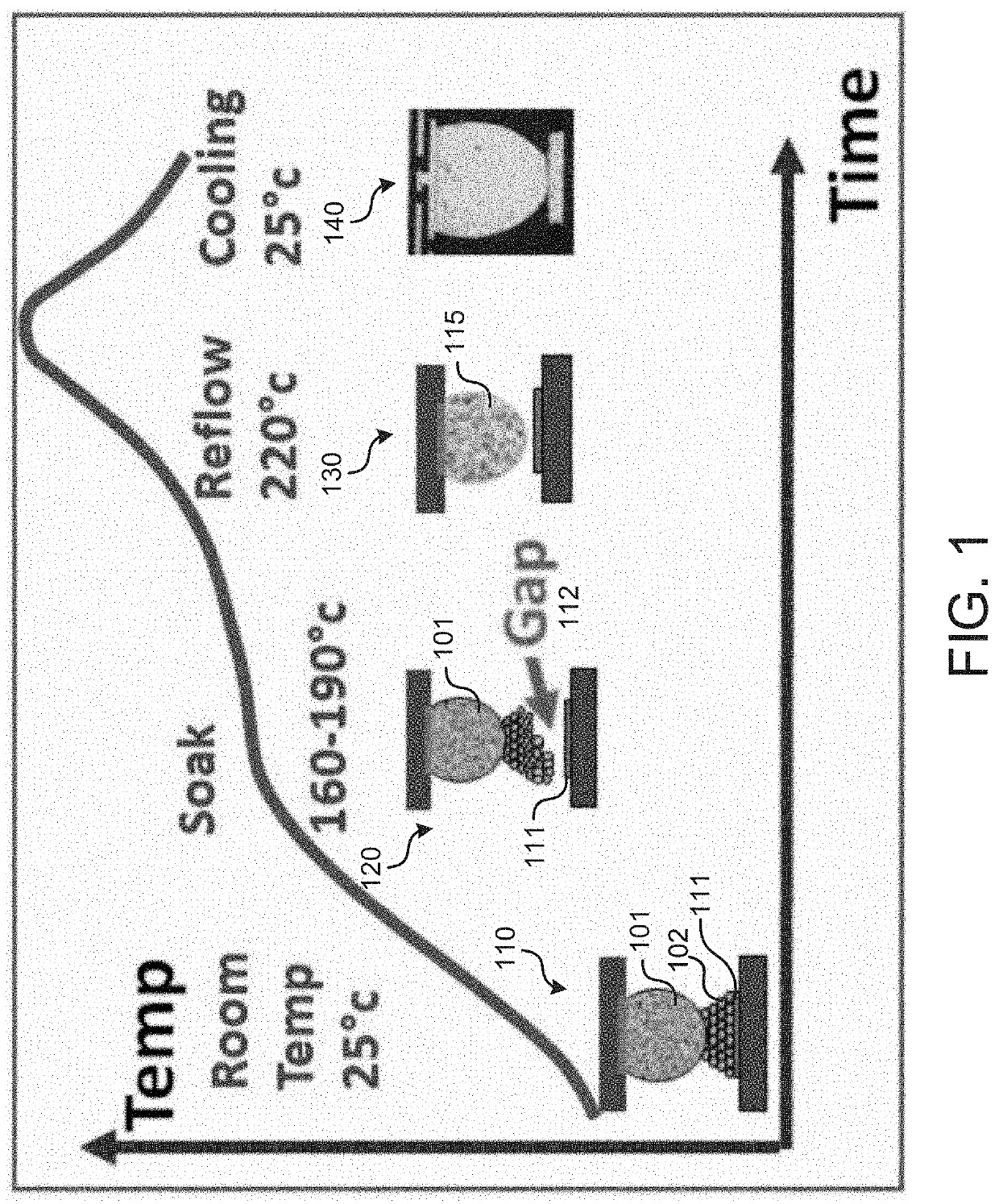

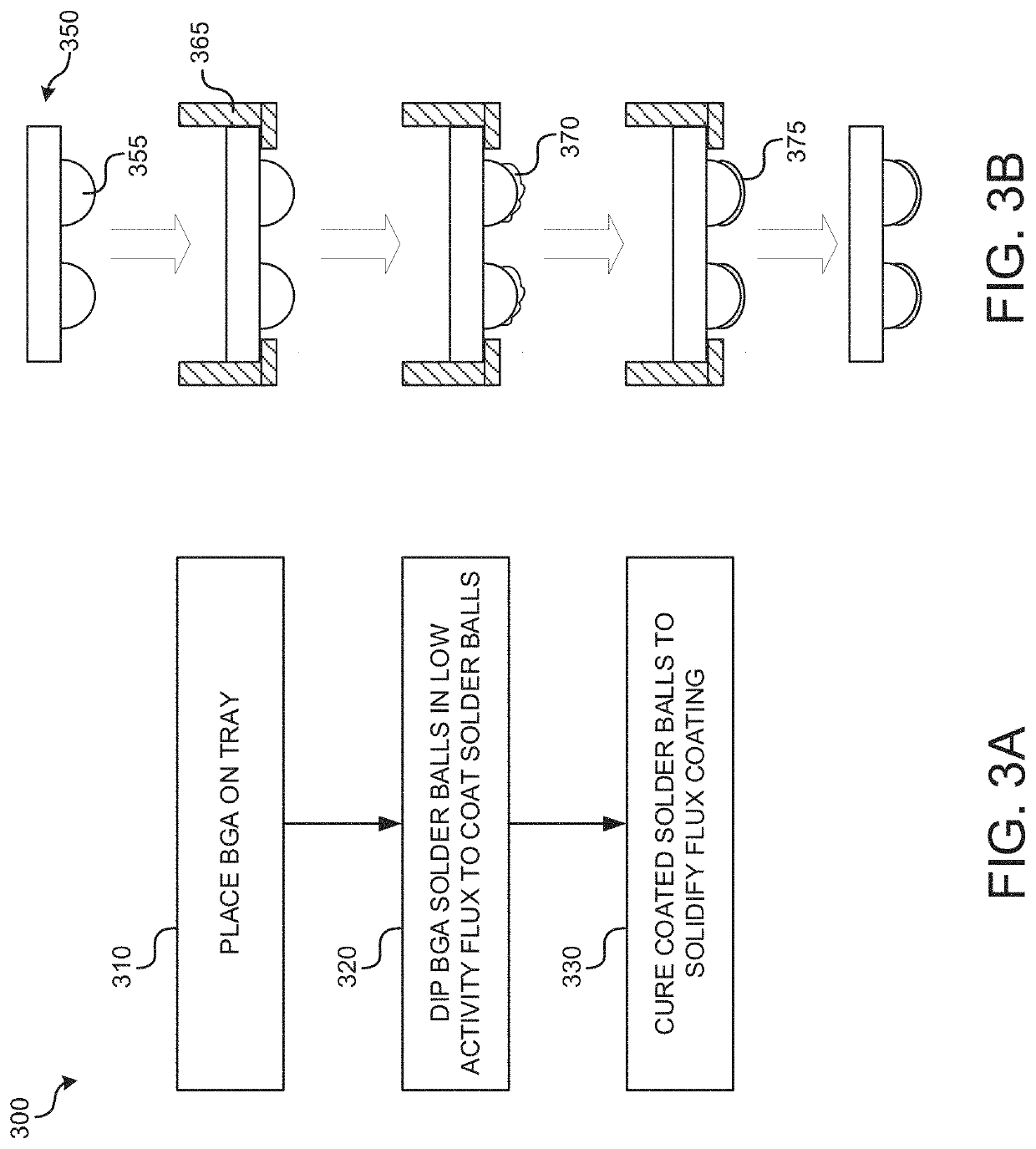

Fluxes effective in suppressing non-wet-open at bga assembly

ActiveUS20190371752A1Eliminating and reducing non-wet open (NWO) defect formationReduce defect formationPrinted circuit assemblingSemiconductor/solid-state device detailsLow activityMetallurgy

The disclosure describes techniques for eliminating or reducing non-wet open (NWO) defect formation by using a low activity flux to prevent a solder paste from sticking to ball grid array (BGA) solder balls during reflow soldering. The low activity flux may be configured such that: i) it creates a barrier that prevents the solder paste from sticking to the solder balls of the BGA; and ii) it does not impede the formation of solder joints during reflow. In implementations, a solid coating of the low activity flux may be formed over balls of the BGA, and the BGA may then be bonded to a PCB during reflow. In implementations, the balls of a BGA may be dipped in a low-activity creamy or liquid flux prior to reflow. In some implementations, the flux may applied on a solder paste printed on pads of the PCB, followed by placement of a BGA.

Owner:INDIUM CORPORATION

Process for preparing anti-wear, anti-corrosion nano composite epoxy zinc-enriched paint

Owner:SHANGHAI UNIVERSITY OF ELECTRIC POWER