Scribe street seals in semiconductor devices and method of fabrication

a technology of semiconductor devices and scribes, applied in semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve problems such as latent failures, and achieve the effects of improving toughness and energy absorption capacity, high density ics, and low end

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

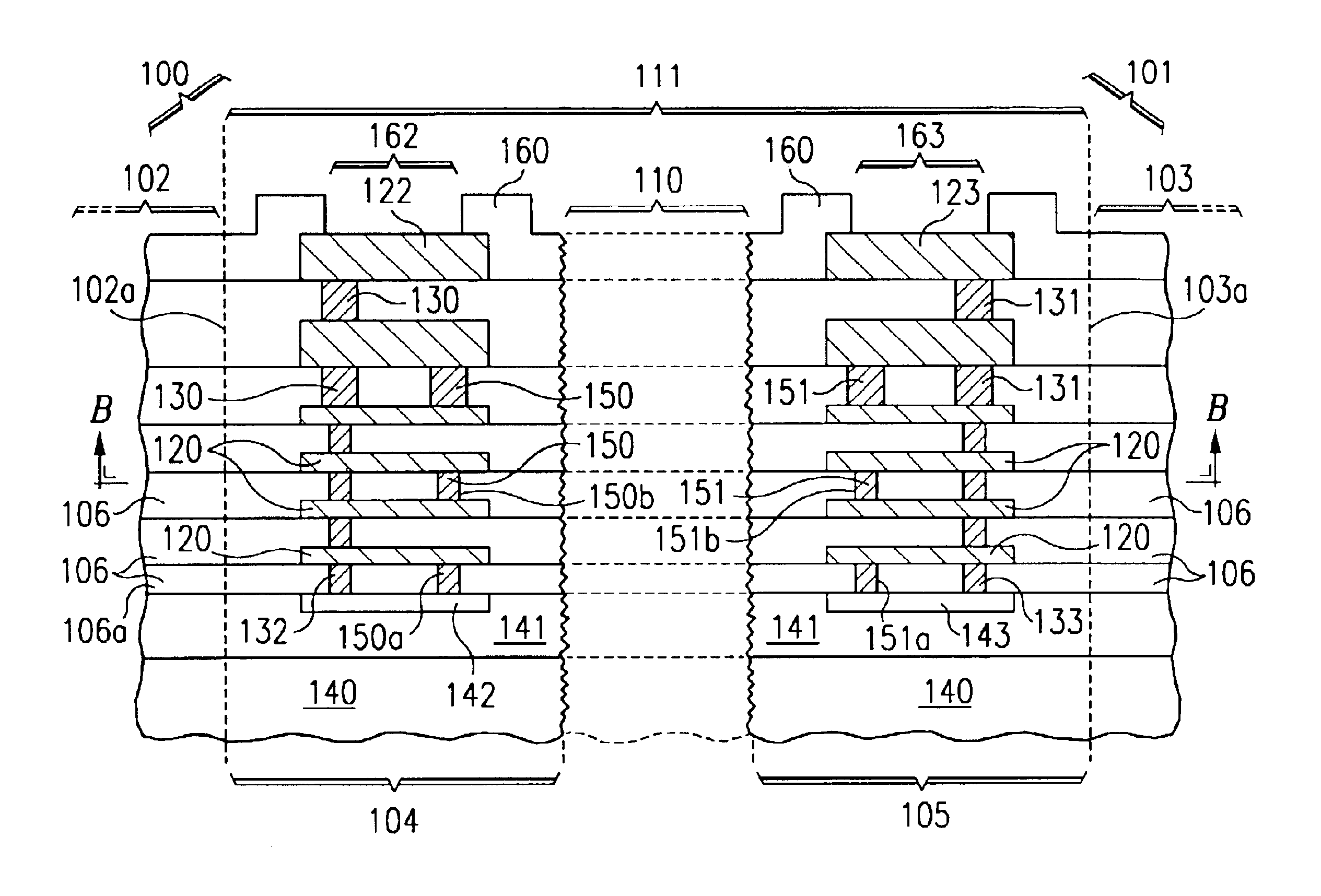

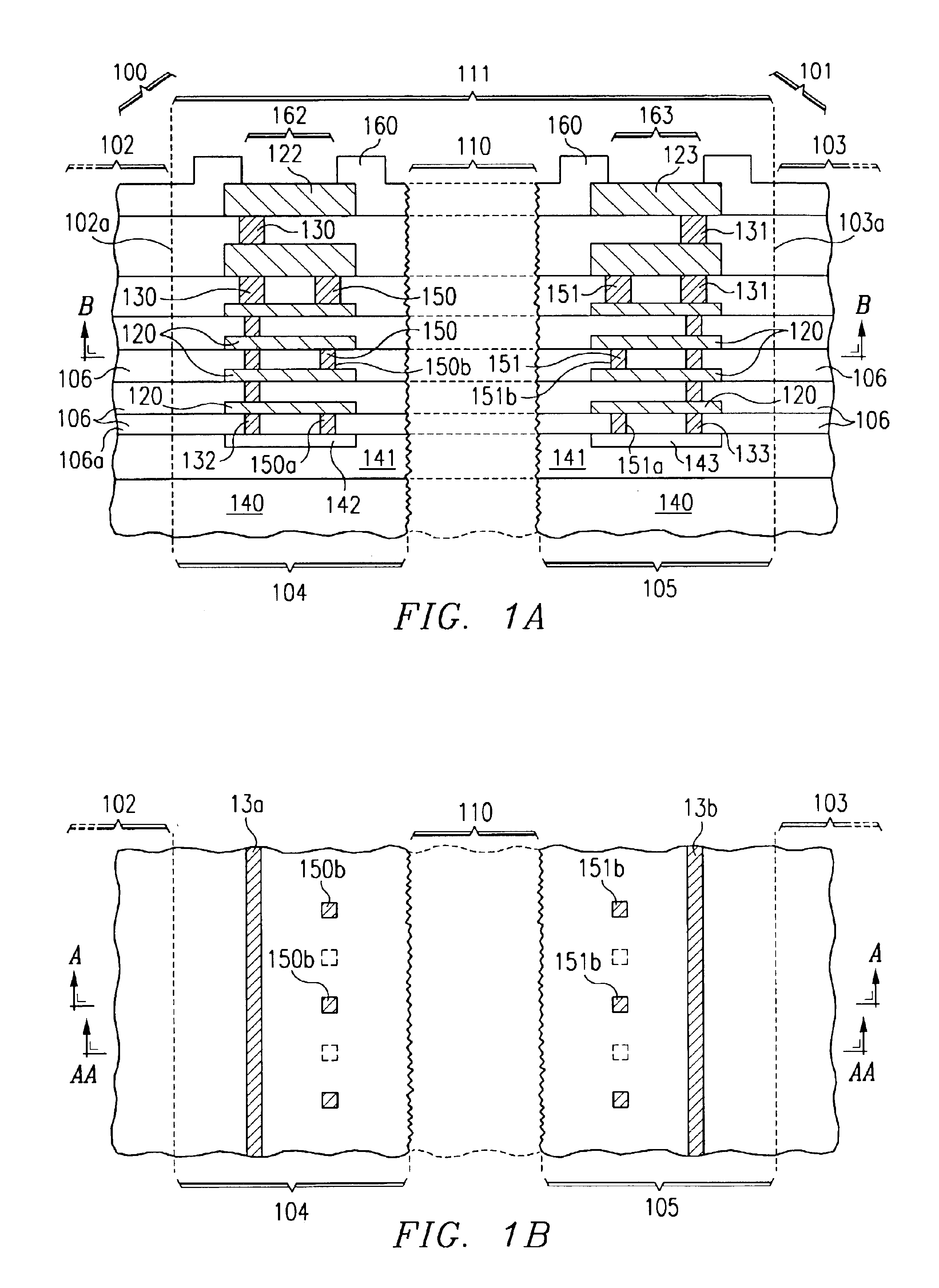

FIG. 1A is a schematic cross section through a small portion of circuit chips 100 and 101 and the dicing line 110 between them. FIG. 1A also shows the cross sections through seal regions 104 and 105, with several embodiments of the invention positioned in each. The first embodiment comprises a seal structure made of a combination of a continuous wall and a discontinuous wall, interconnected by a plurality of patterned, electrically conductive layers 120. These layers are usually made of metal and are formed and patterned simultaneously with the equivalent metal levels of the ICs. As required by the specific IC design, the material of the electrically conductive layer is selected from a group consisting of copper, copper alloy, aluminum, aluminum alloy, tantalum, titanium, tungsten, molybdenum, chromium and compounds thereof.

The part of the seal structure closest to the chip data edge is the continuous barrier wall made by first etching trenches 130 and 131 through the thickness of t...

second embodiment

FIGS. 1A, 2A and 3B also illustrate the present invention, the slot opened in the protective overcoat and reaching from the surface of the overcoat at least to the surface-nearest electrically conductive layer of the sacrificial seal structure. The protective overcoat layer 160 is deposited over the whole wafer in a thickness usually between 0.5 and 1.0 μm. The preferred materialis moisture impermeable silicon nitride, silicon oxy-nitride, or combinations thereof. While the layer is free of pinholes, it is brittle, and cracks originating from dicing line 110 are able to propagate, approximately parallel to the surface, towards the circuit.

Consequently, the invention calls for slots (162 and 163 in FIGS. 1A and 2A, 161 in FIG. 3B) reaching from the surface of overcoat 160 through its whole thickness at least to the surface-nearest electrically conductive layer of the composite structures in the seal regions. In FIGS. 1A and 2A, these conductive layers are designated 122 and 123 in ch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More