Method for making groove power semiconductor device

A device manufacturing method and power semiconductor technology, which are applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of increasing process complexity, device performance degradation, and source region junction depth, etc., to improve switching characteristics, The effect of increasing the breakdown strength and reducing the electric field strength

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

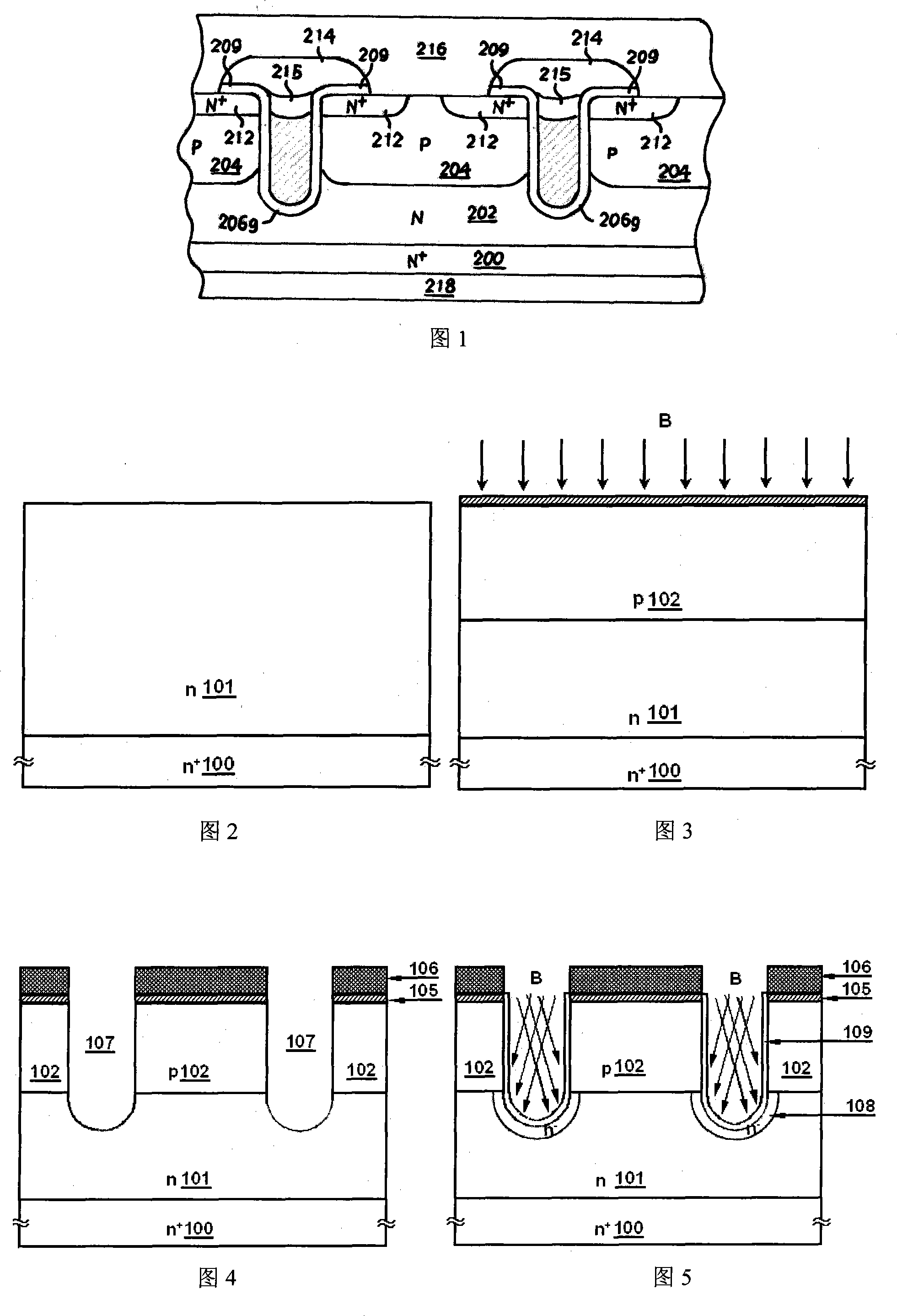

[0051] In conjunction with Figures 2-9, the specific steps of this embodiment are:

[0052] (1) Base preparation, in n + or p + Epitaxial growth on substrate n - Area;

[0053] (2) Utilize the LPCVD method to grow a thin oxide layer on the semiconductor substrate obtained in step (1), and the film thickness is controlled at 500 angstroms;

[0054] (3) Perform ion implantation of B impurities on the surface of the semiconductor substrate obtained in step (2), the ion implantation energy is typically 600KeV, and the implantation dose is controlled at 10 14 cm -2 ;

[0055] (4) utilize LPCVD method to grow Si at the semiconductor substrate surface of step (3) gained 3 N 4 , the thickness is controlled at 800 Angstroms;

[0056] (5) Spin-coat photosensitive adhesive on the surface of the semiconductor substrate obtained in step (4), obtain a groove etching window through a photolithography process, and form a groove structure by combining dry etching and wet etching;

[0...

Embodiment 2

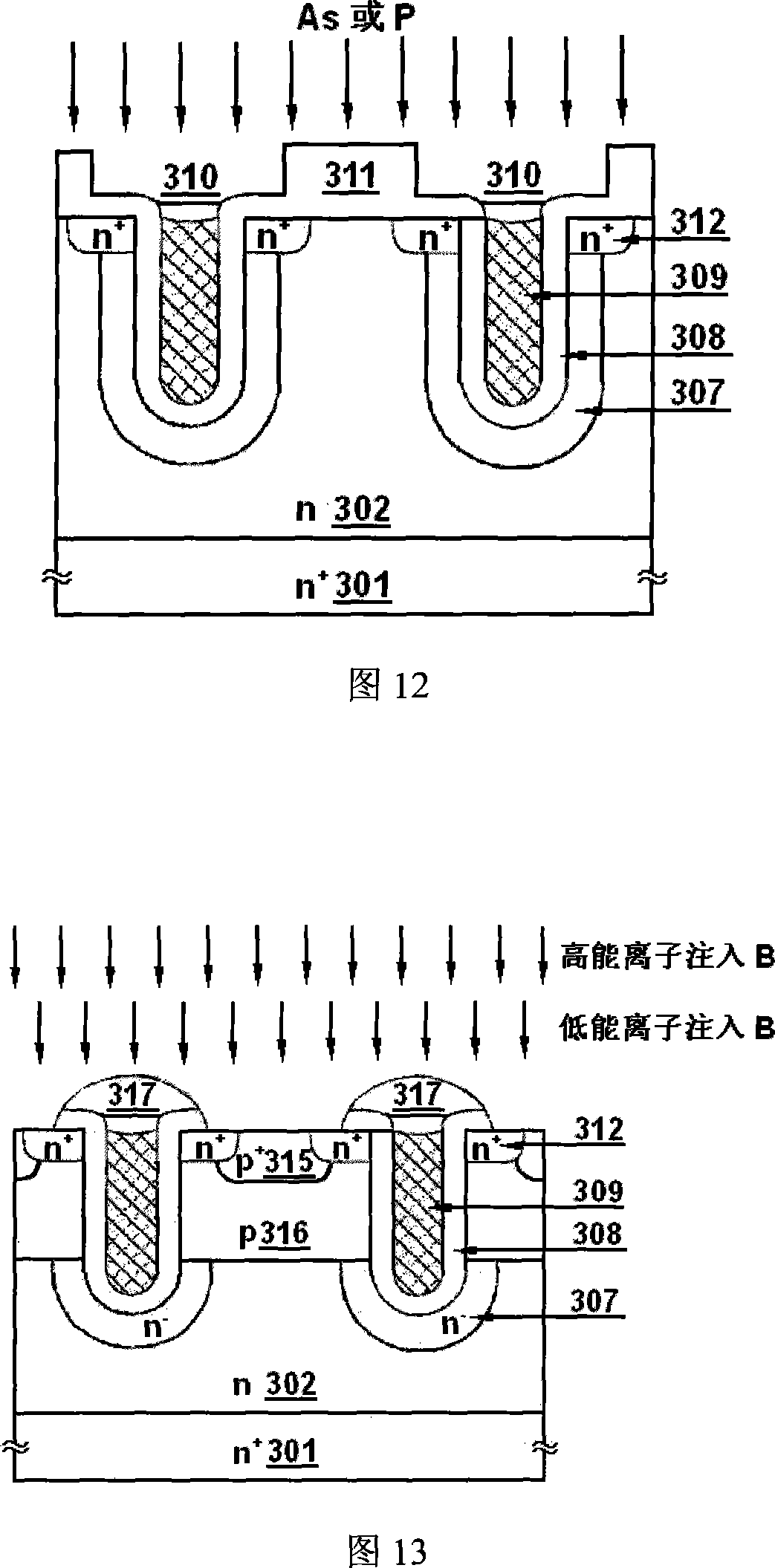

[0071] Referring to FIG. 10 , an epitaxial layer 302 is grown on an n+ substrate 301 with a resistivity of 0.003Ω·cm, and the thickness of the epitaxial layer depends on the requirements of the device for withstand voltage and on-resistance. On the surface of the epitaxial layer 302, LPCVD sequentially grows SiO with a thickness of 1000 Ȧ 2 layer 303 and Si with a thickness of 600 Å 3 N 4 Layer 304. Form the etching window of the trench gate through the photolithography process, adopt anisotropic etching such as RIE to form the trench 305, and supplemented by wet etching (in this embodiment, dilute HNO 3 , HF and H 2 O mixture). SiO with a thickness of 1300 Ȧ was grown by LPCVD on the inner surface of the trench of the above-mentioned substrate 2 The sacrificial layer 306 is grown under the implantation energy of 100KeV, with 5*10 11 cm -2 The dose of B is injected into B, and the n-region 307 is formed by diffusion at a high temperature of 1100° C. for 100 minutes.

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More