Passivation layer of IC chip

A technology of integrated circuits and passivation layers, applied in circuits, electrical components, electrical solid devices, etc., can solve problems such as peeling off, failure of integrated circuit devices, and poor adhesion, and achieve the effect of improving yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

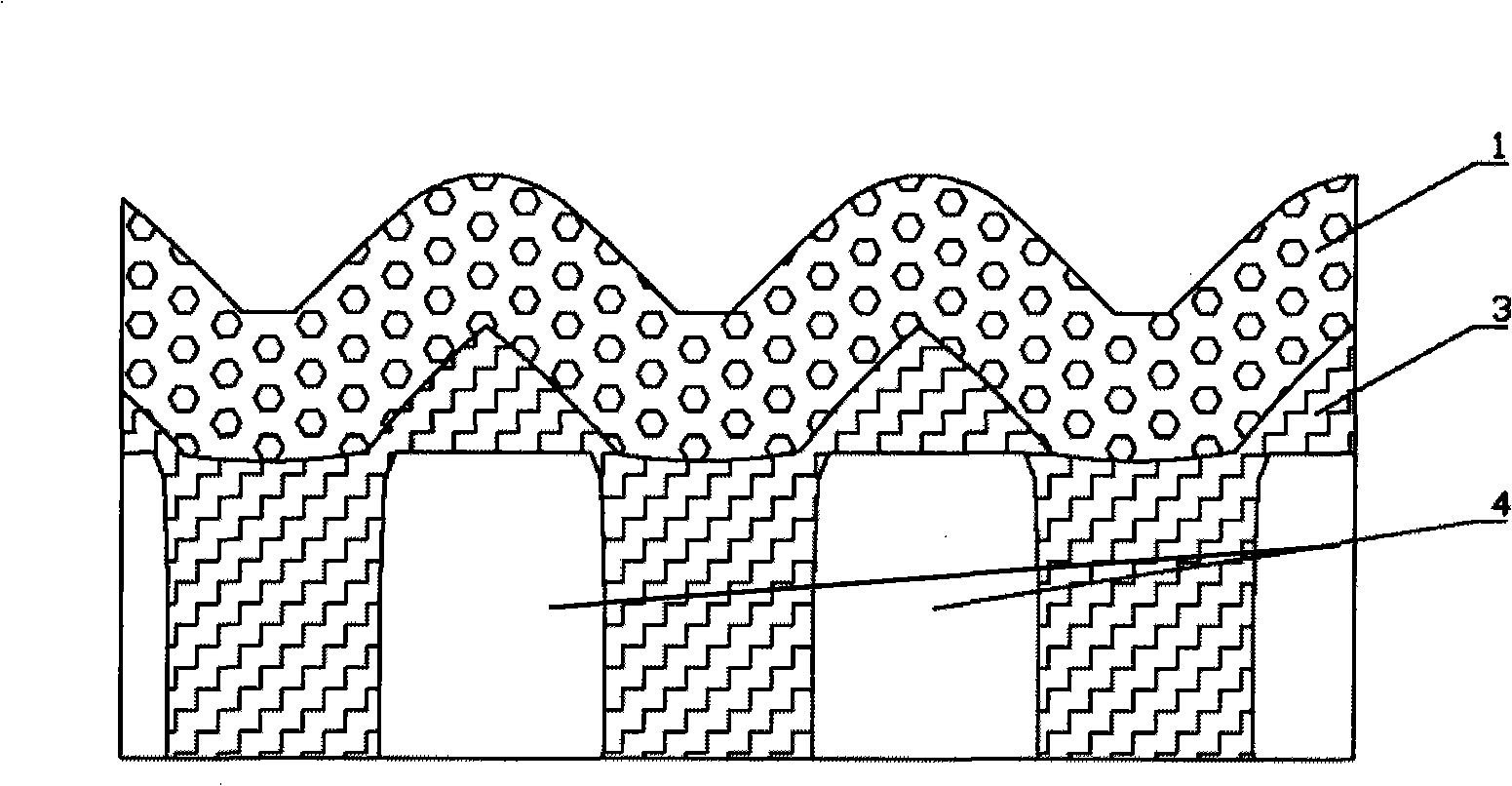

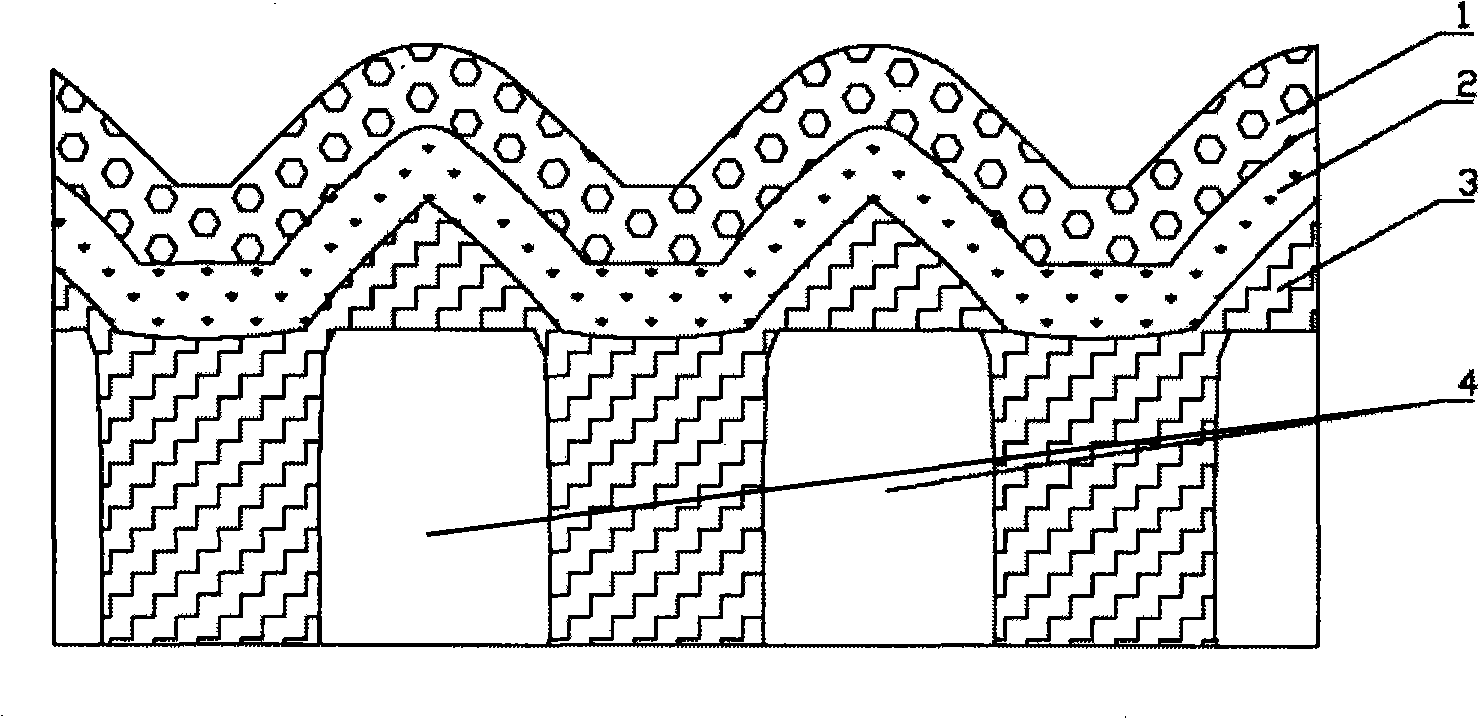

[0022] see figure 2 , the invention discloses a passivation layer of an integrated circuit chip, comprising at least a first SiO 2 Layer 3, second SiO 2 Layer 2 and SiN layer 1. Second SiO 2 Layer 2 is located on the first SiO 2 Between layer 3 and SiN layer 1.

[0023] First SiO 2 Layer 3 is formed by a high-density plasma chemical vapor deposition (HDPCVD) process or a plasma-enhanced chemical vapor deposition (PECVD) process, and the first SiO 2 Both layer 3 and SiN layer 1 exert shrinkage stress on the metal layer. In the present invention, the thickness of both and SiO in the prior art 2 layer is the same thickness as the SiN layer.

[0024] Second SiO 2 Layer 2 is produced by a sub-atmospheric chemical vapor deposition (SACVD) process, usually with ozone (O 3 ) and tetraethyl orthosilicate (TEOS) chemical reaction, depositio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More