Packaging structure and packaging method of semiconductor device

A device packaging and semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problems of significant thermo-mechanical stress, increase the cost of process methods, exceed, etc., and achieve thermo-mechanical stress reduction Small, avoid thermal mismatch, improve the effect of electrical performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

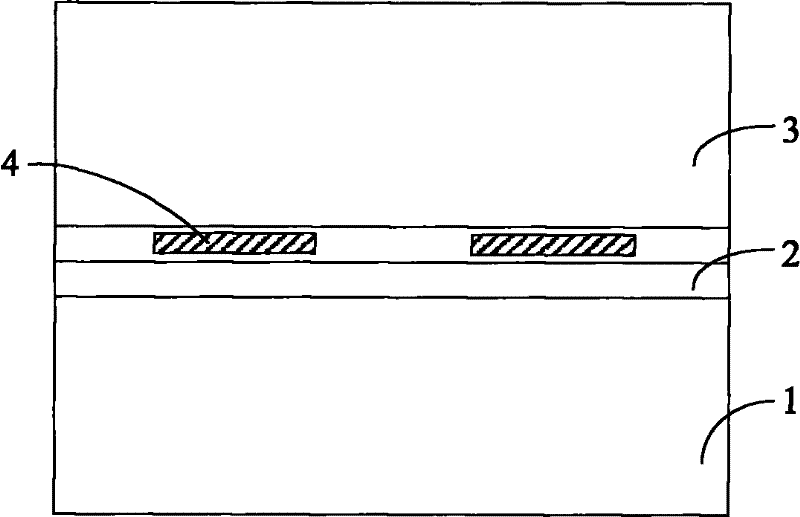

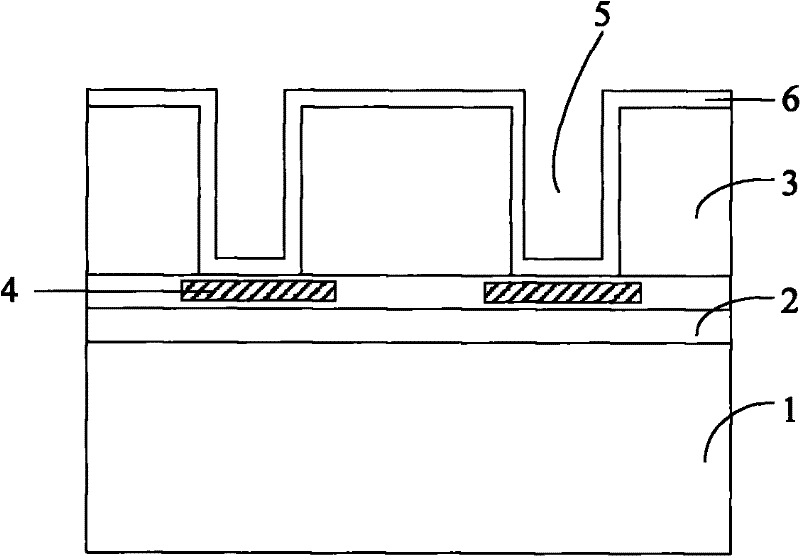

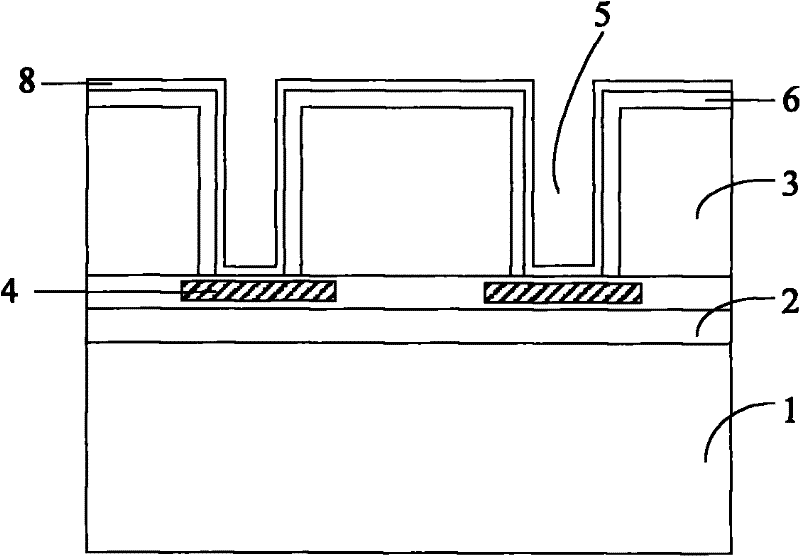

[0029] The current process methods for processing the through-silicon via interconnect structure are: (1) using reactive ion etching-inductively coupled plasma (RIE-ICP) method to etch through holes on the chip; (2) using chemical vapor deposition (CVD) (1) Oxide or nitride passivation method to form a dielectric layer (usually silicon dioxide) on the inner wall of the through hole; (3) metallize the through hole; (4) back-grind the wafer.

[0030] This process has the following problems: (1) There is only a very thin dielectric layer (usually silicon dioxide) between the chip and the conductor layer, which leads to the formation of high capacitance between TSV interconnects. Sometimes it even exceeds the capacitance value of the standard wire bonding interconnection method; (2) A conductor layer with a predetermined thickness is filled in the through hole. Due to the large thermal mismatch between the silicon and the conductor layer, it will be in the thermal cycle process. (3) ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More