Realization method and device of multiphase filter structure

A technology of polyphase filter and filter, applied in the direction of impedance network, digital technology network, electrical components, etc., can solve the problems of efficiency bottleneck, low efficiency, poor flexibility, etc., and achieve the effect of ensuring real-time generation and saving hardware resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment 1

[0078] The specific structure of the device is as Figure 16 As shown, it includes the following parts:

[0079] (1) The clock source provides a clock clk_f synchronized with the highest sampling clock of the input digital signal;

[0080] (2) Data cache memory array, referred to as data cache array, it contains M+1 capacity of D MAX The readable and writable memory of: RAM(0), RAM(1), ..., RAM(M).

[0081](3) Multiplexer, the unit is connected to the data input port, the control unit, the data buffer array, and the weighted sum unit. Specifically, there are the following ports: data input port In; multiplexing state control port S connected to the control unit, data buffer array control signal input port WR, AddrD_WR, RD, AddrD_RD; control signal output port Addr_m, WRm connected to the data buffer array , RDm, data input port RAM(m)_Din, data output port RAM(m)_Dout,; data vector output port x connected to the weighted summation unit 1 , x 2 ,...,x M . The gating mode...

specific Embodiment 2

[0102] The structure of the device is as Figure 23 As shown, it contains the following parts:

[0103] (1) The clock source, which provides the clock clk_f with the same frequency as the highest input data rate;

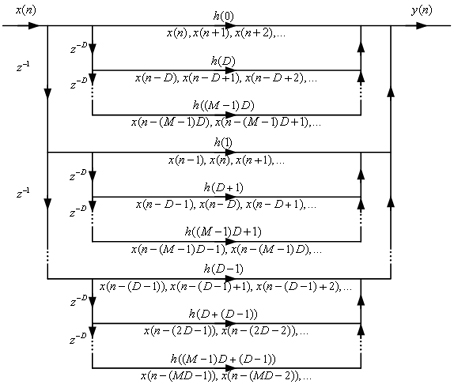

[0104] (2) A multi-tap high-order delay line, which is implemented by a shift register or a first-in-first-out (FIFO) memory, corresponding to K possible values of D, there are K groups of tap sequences on the high-order delay line, and the tap positions are 0, D, 2D, ..., (M-1)D, where D ∈ {D 1 ,D 2 ,...,D K}, the total order of the multi-tap high-order delay line is (M-1)D MAX .

[0105] (3) Multiplexer, its gating mode setting port SEL is connected to the control unit, all taps of the multi-tap high-order delay line at the input port are connected, and the output port is connected to the data vector input port x of the weighted summation unit 1 , x 2 ,...,x M connected. When the value on SEL is k (or D K ), the multiplexer takes the tap sequence 0 of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More