Silicon-on-insulator N-type transverse insulated gate bipolar transistor and preparation method thereof

A bipolar transistor and silicon-on-insulator technology, which is applied in the manufacture of semiconductor/solid-state devices, semiconductor devices, electrical components, etc., can solve the problems of reducing the current capability of the device, affecting the impurity concentration of the P-type doped body region, etc., to improve triggering. Effects of Threshold Conditions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

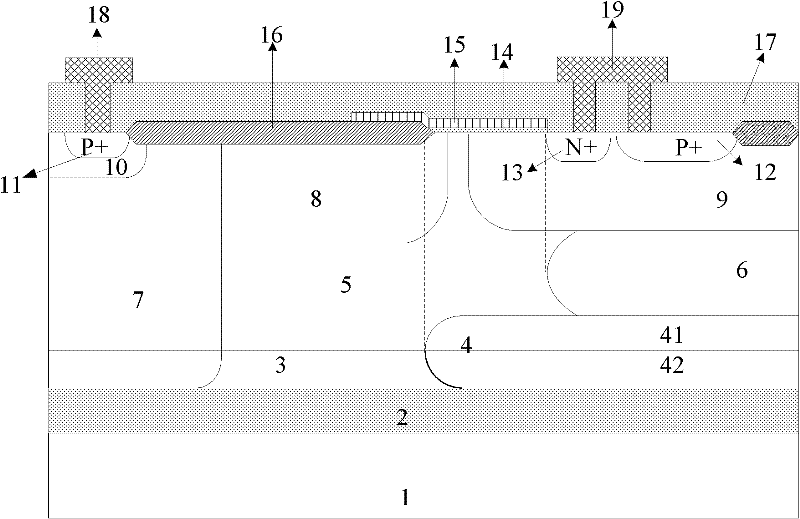

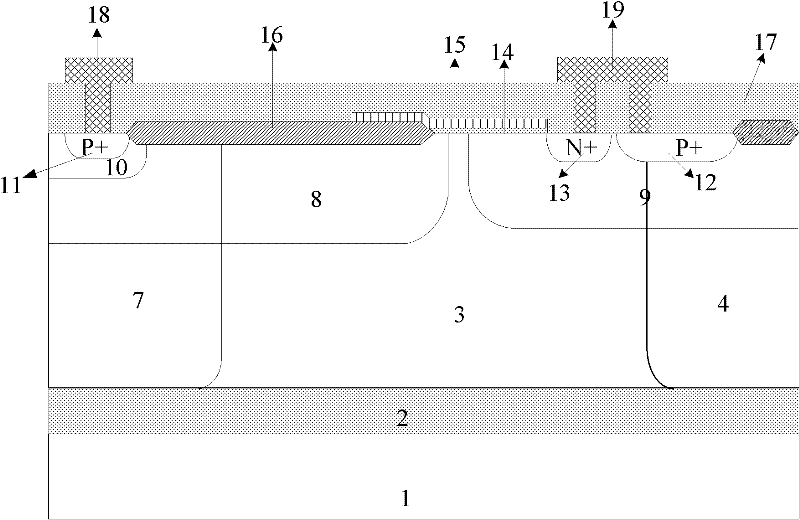

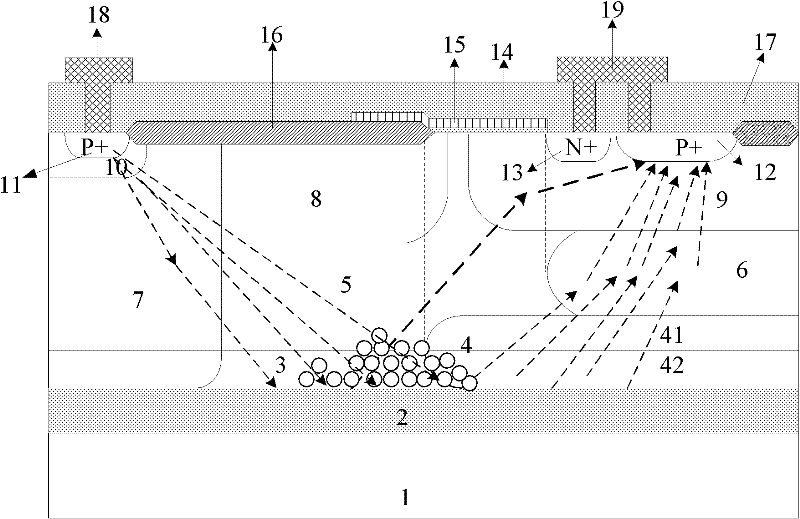

[0025] refer to figure 1, a silicon-on-insulator N-type lateral insulated gate bipolar transistor, comprising: a P-type substrate 1, a buried oxide layer 2 is arranged on the P-type substrate 1, and a first P-type oxide layer is arranged on the buried oxide layer 2 The epitaxial layer 3 is provided with a second P-type epitaxial layer 5 above the first P-type epitaxial layer 3, and an N-type doped deep well 7 is provided on the left side of the second P-type epitaxial layer 5. An N-type doped drift region 8 is arranged in the well 7 and part of the second P-type epitaxial layer 5, and an N-type buffer layer 10 is arranged in the N-type doped drift region 8, and a P-type buffer layer 10 is arranged in the N-type buffer layer 10. The doped anode contact region 11 is provided with a P-type doped channel region 9 on the right side of the second P-type epitaxial layer 5, and an N-type doped cathode contact region 13 and The P-type doped body contact region 12 is provided with a f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More