Linear voltage stabilizing circuit with low voltage difference

A low-dropout linear and voltage-stabilizing circuit technology, which is applied in the direction of adjusting electrical variables, control/regulation systems, instruments, etc., can solve the problems of low dominant pole, poor interference ability of medium and high frequency power supply, low power supply rejection ratio of LDO circuit, etc., to achieve Improved power supply rejection ratio and reduced resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

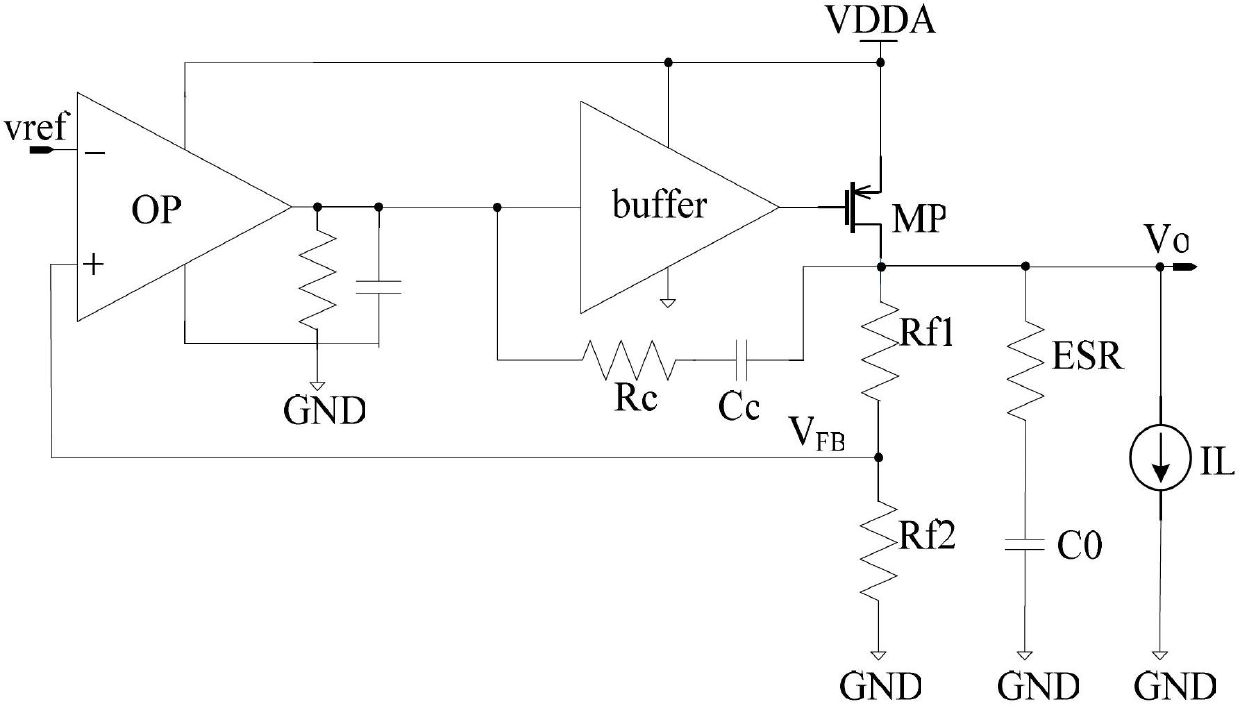

[0055] As mentioned in the background art, the LDO circuit in the prior art has poor ability to resist power supply interference and low power supply rejection ratio, and cannot provide clean and reliable DC power for many current high-speed and high-performance SOCs.

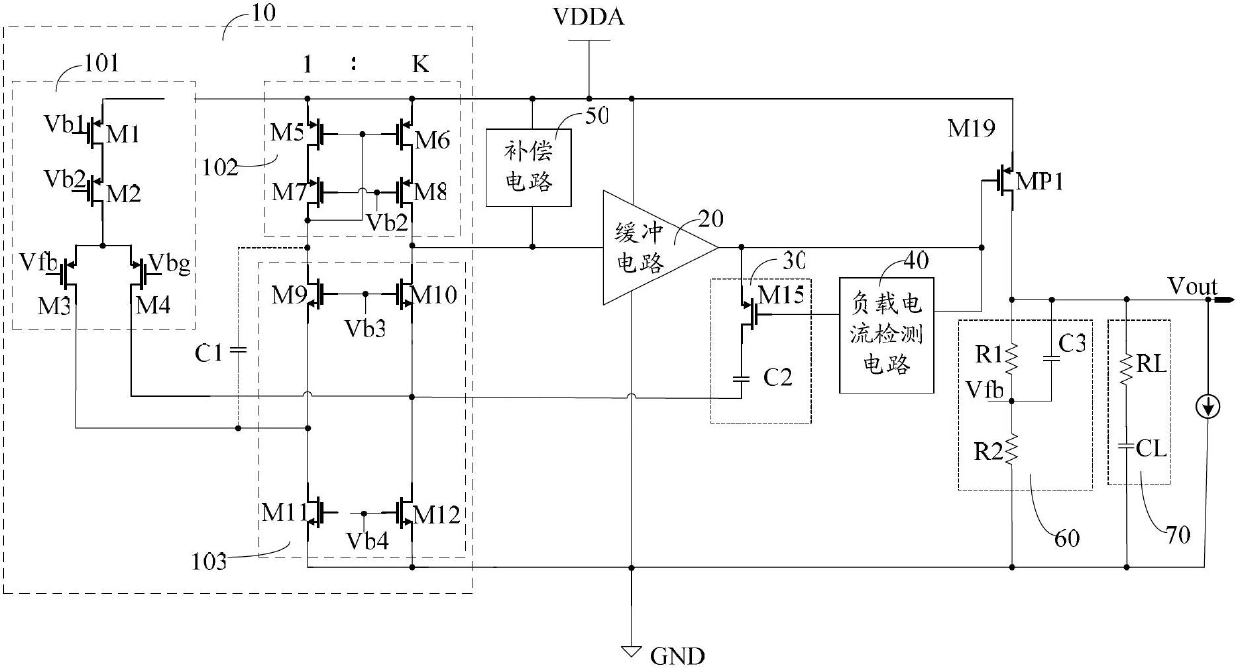

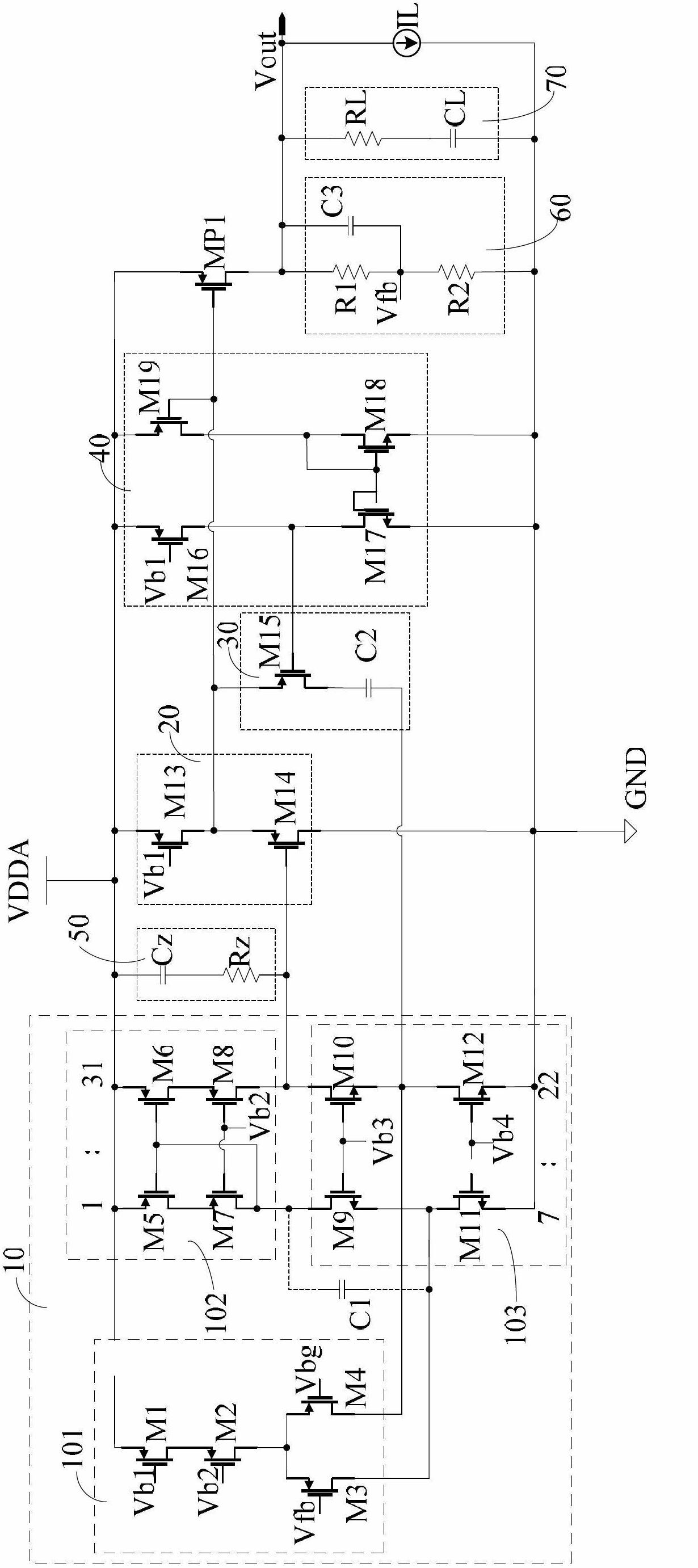

[0056] In the technical solution of the present invention, the ratio of the width-to-length ratio of the fifth PMOS transistor to the width-to-length ratio of the sixth PMOS transistor of the error amplifier, and the ratio of the width-to-length ratio of the seventh PMOS transistor to the width-to-length ratio of the eighth PMOS transistor And the ratios of the width-to-length ratios of the ninth NMOS transistor and the tenth NMOS transistor are both 1:K, and K is an integer greater than 1. The power supply rejection ratio of the low-dropout linear regulator circuit in the technical solution is effectively improved by changing the ratio between the width and length ratios of the above-mentioned MOS transistors. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More