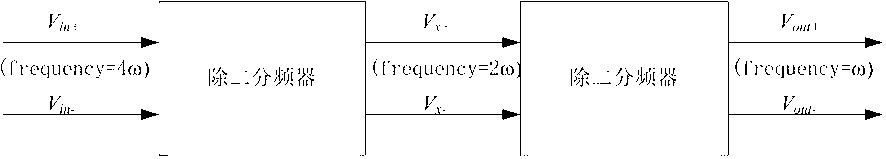

Divide-by-four injection locked frequency divider circuit with low power consumption and wide lock range

A technology of injecting locking and locking range, which is applied in the direction of automatic power control and electrical components, and can solve problems such as small locking range, increased power consumption and area of frequency divider links, and small output swing of the front stage.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

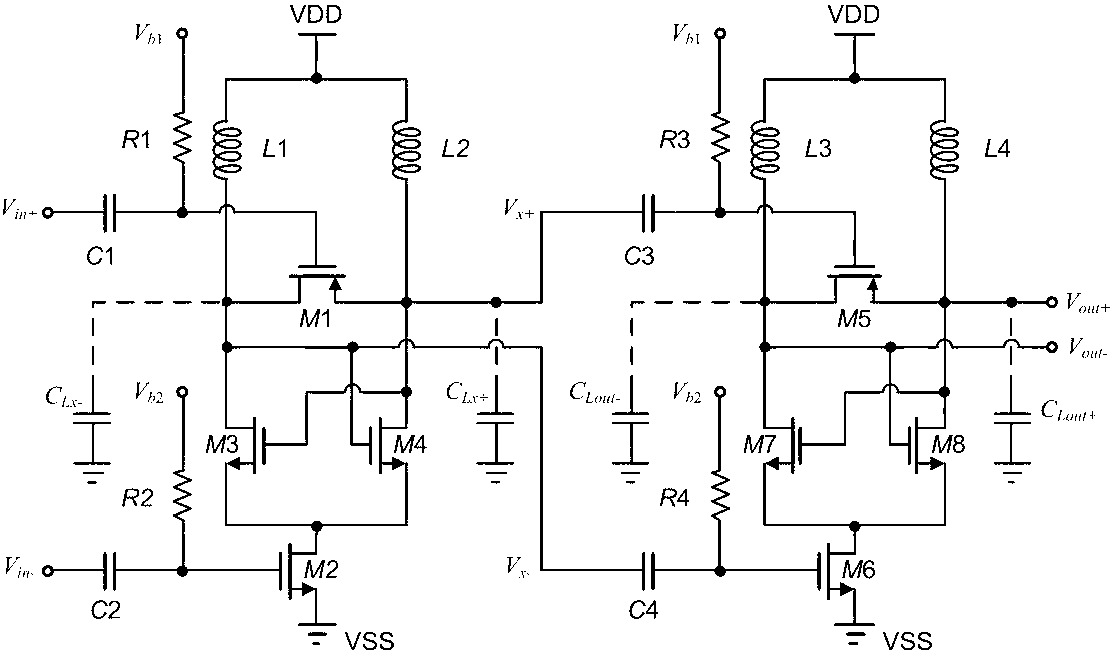

[0037] Take the design of a low-power, wide-locked-range divider-by-four injection-locked divider with an input frequency between 26.25GHz and 30.25GHz as an example.

[0038] design circuit figure 2 As shown, add a fully differential amplifier as a load circuit. The TSMC 0.13μm RF CMOS 1P8M process is adopted, the simulation tool is Cadence SpectreRF, and the power supply voltage is 800mV. where V b1 = V b3 = 1.2V, V b2 and V b4 Change to current mirror bias to reduce process deviation, the actual value is around 600mV.

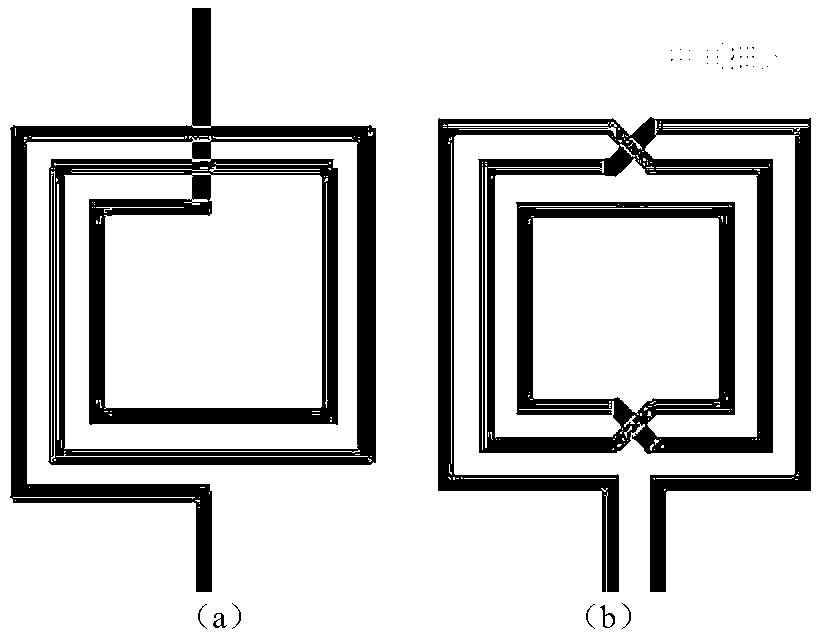

[0039] The MOS tubes are all radio frequency NMOS tubes, the resistors are high-resistance polysilicon resistors, the capacitors are MIM capacitors, the inductors are on-chip spiral inductors with center taps, and the eighth layer of metal wiring. L1 and L2 are implemented with a 1.67nH inductor, and L3 and L4 are implemented with a 4.15nH inductor.

[0040] When the input signal size is 0dBm (single-ended peak-to-peak value is 632mV) differential...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More