SiGe based strain BiCMOS (Bipolar Complementary Metal-Oxide-Semiconductor Transistor) integrated device and preparation method thereof

A technology for MOS devices and integrated devices, which is applied in semiconductor/solid-state device manufacturing, electrical solid-state devices, semiconductor devices, etc., and can solve problems such as the inability to meet low power consumption, the inability to meet the requirements of lithography technology, and the impact of device performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

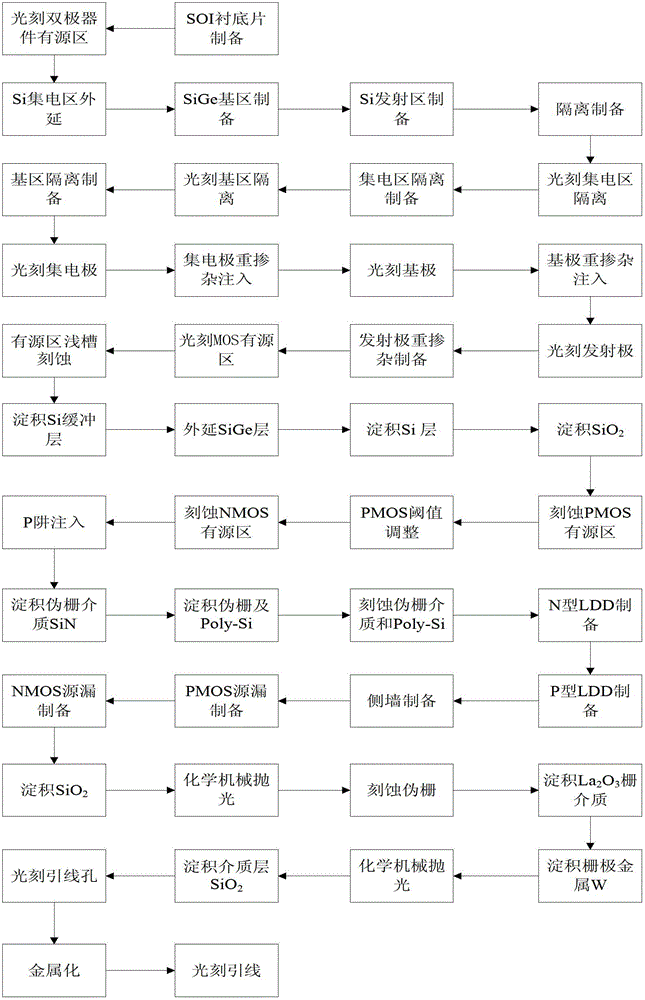

[0116] Embodiment 1: To prepare a SiGe-based strained BiCMOS integrated device and circuit with a channel length of 22nm, the specific steps are as follows:

[0117] Step 1, SOI substrate material preparation.

[0118] (1a) Select the N-type doping concentration as 1×10 15 cm -3 The Si sheet is oxidized on its surface, and the thickness of the oxide layer is 1 μm, which is used as the base material of the upper layer, and hydrogen is injected into the base material;

[0119] (1b) Select the N-type doping concentration as 1×10 15 cm -3 The Si sheet is oxidized on its surface, and the thickness of the oxide layer is 1 μm, which is used as the base material of the lower layer;

[0120] (1c) Using a chemical mechanical polishing (CMP) process to polish the surface of the lower layer and the upper layer of substrate material after hydrogen injection;

[0121] (1d) Put the oxide layer on the surface of the polished lower layer and the upper layer of the base material relatively...

Embodiment 2

[0183] Embodiment 2: To prepare a SiGe-based strained BiCMOS integrated device and circuit with a channel length of 130nm, the specific steps are as follows:

[0184] Step 1, SOI substrate material preparation.

[0185] (1a) Select the N-type doping concentration as 3×10 15 cm -3 The Si sheet is oxidized on its surface, and the thickness of the oxide layer is 0.7 μm, which is used as the base material of the upper layer, and hydrogen is injected into the base material;

[0186] (1b) Select the N-type doping concentration as 3×10 15 cm -3 The Si sheet is oxidized on its surface, and the thickness of the oxide layer is 0.7 μm, which is used as the base material of the lower layer;

[0187] (1c) Using a chemical mechanical polishing (CMP) process to polish the surface of the lower layer and the upper layer of substrate material after hydrogen injection;

[0188] (1d) Put the oxide layer on the surface of the polished lower layer and the upper layer of the base material relat...

Embodiment 3

[0250] Embodiment 3: The preparation of SiGe-based strained BiCMOS integrated devices and circuits with a channel length of 350nm, the specific steps are as follows:

[0251] Step 1, SOI substrate material preparation.

[0252] (1a) Select the N-type doping concentration as 5×10 15 cm -3 The Si sheet is oxidized on its surface, and the thickness of the oxide layer is 0.5 μm, which is used as the base material of the upper layer, and hydrogen is injected into the base material;

[0253] (1b) Select the N-type doping concentration as 5×10 15 cm -3 The Si sheet is oxidized on its surface, and the thickness of the oxide layer is 0.5 μm, which is used as the base material of the lower layer;

[0254] (1c) Using a chemical mechanical polishing (CMP) process to polish the surface of the substrate material of the lower layer and the upper layer of the active layer after injecting hydrogen, respectively;

[0255] (1d) Put the oxide layer on the surface of the polished lower layer ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More