Compensation method for increase of amplification times of direct current caused by thinning of germanium-silicon edge

A technology of DC current and compensation method, applied in the manufacturing of circuits, electrical components, semiconductor/solid-state devices, etc., can solve problems such as yield drop, achieve yield improvement, compensate for the rise of collector current, and tighten the distribution of magnification. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

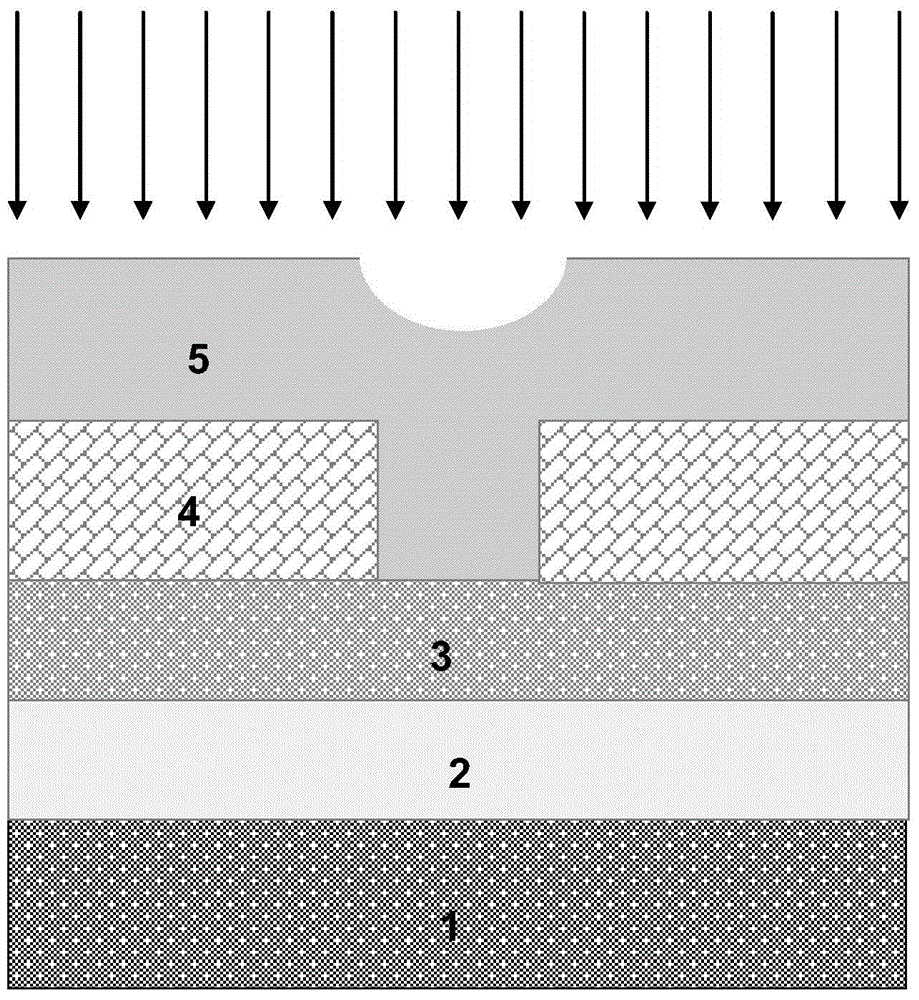

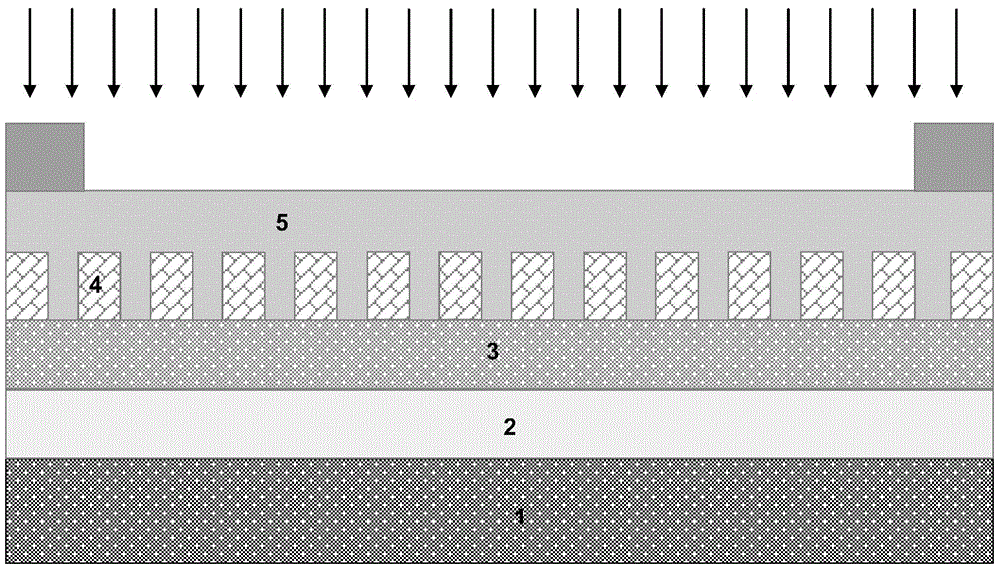

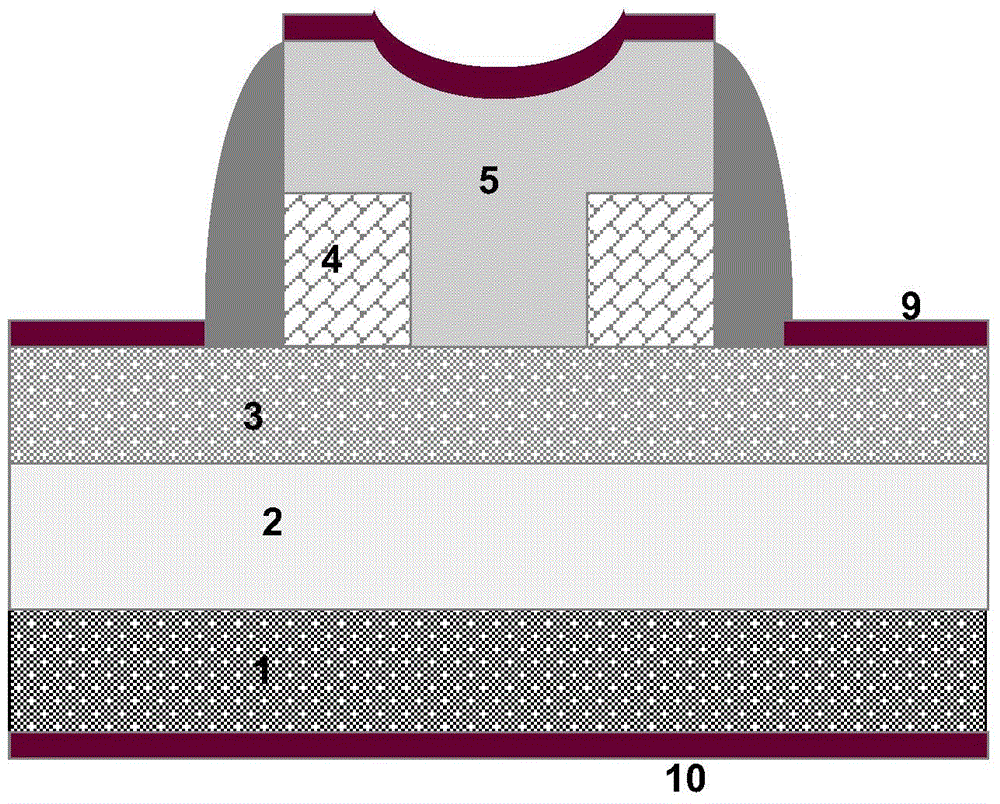

[0024] The compensation method for increasing the direct current amplification factor caused by the thinning of the silicon germanium edge of the present invention is mainly used in the manufacturing process of the emitter area, and the manufacturing process of the collector area and the base area is the same as the commonly used manufacturing process, such as Figure 4 shown. The collector region is manufactured by growing a low N-doped epitaxial layer 2 on a heavily doped N-type silicon substrate 1, with a thickness between 1.0 and 5.0 microns and a doping concentration of 10 15 ~10 17 cm -3 . The manufacture of the base area is to grow a silicon-germanium epitaxial layer 3 on the N-type epitaxial layer 2. The silicon-germanium epitaxial layer 3 is divided into three layers: a silicon buffer layer, a silicon-germanium layer, and a silicon cap layer. Among them, the silicon-germanium layer has a highly doped doped boron and the silicon cap layer has low doped boron. The t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More