Folding gate-controlled L-shaped channel tunneling transistor low in leakage current

A technology of tunneling transistors and low leakage, applied in thyristors, circuits, electrical components, etc., can solve the problems of large static power consumption, weakened gate electrode control ability, and cannot be reduced, achieve fast current rise rate, and overcome sub-threshold characteristics The effect of enhancing the control effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

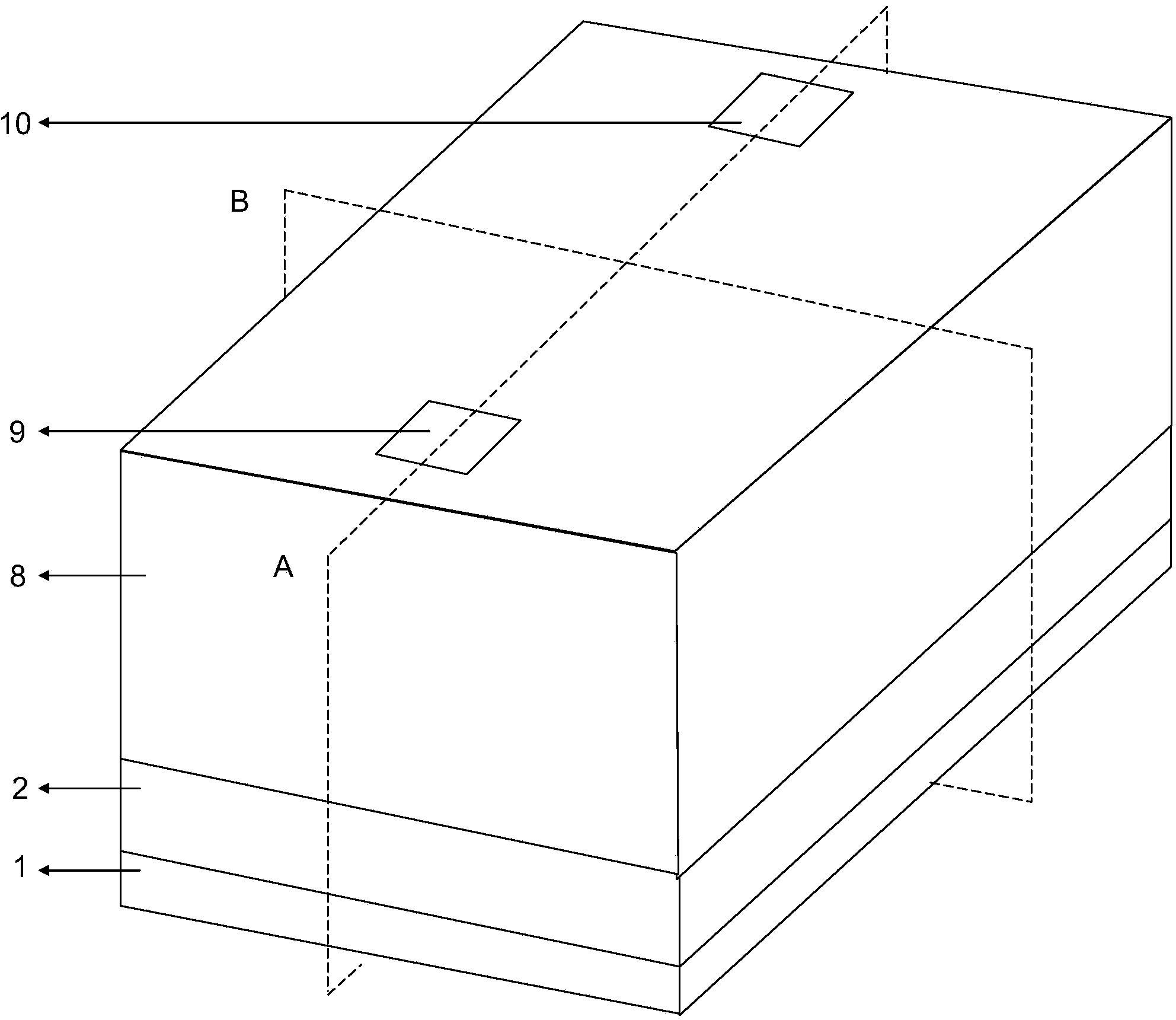

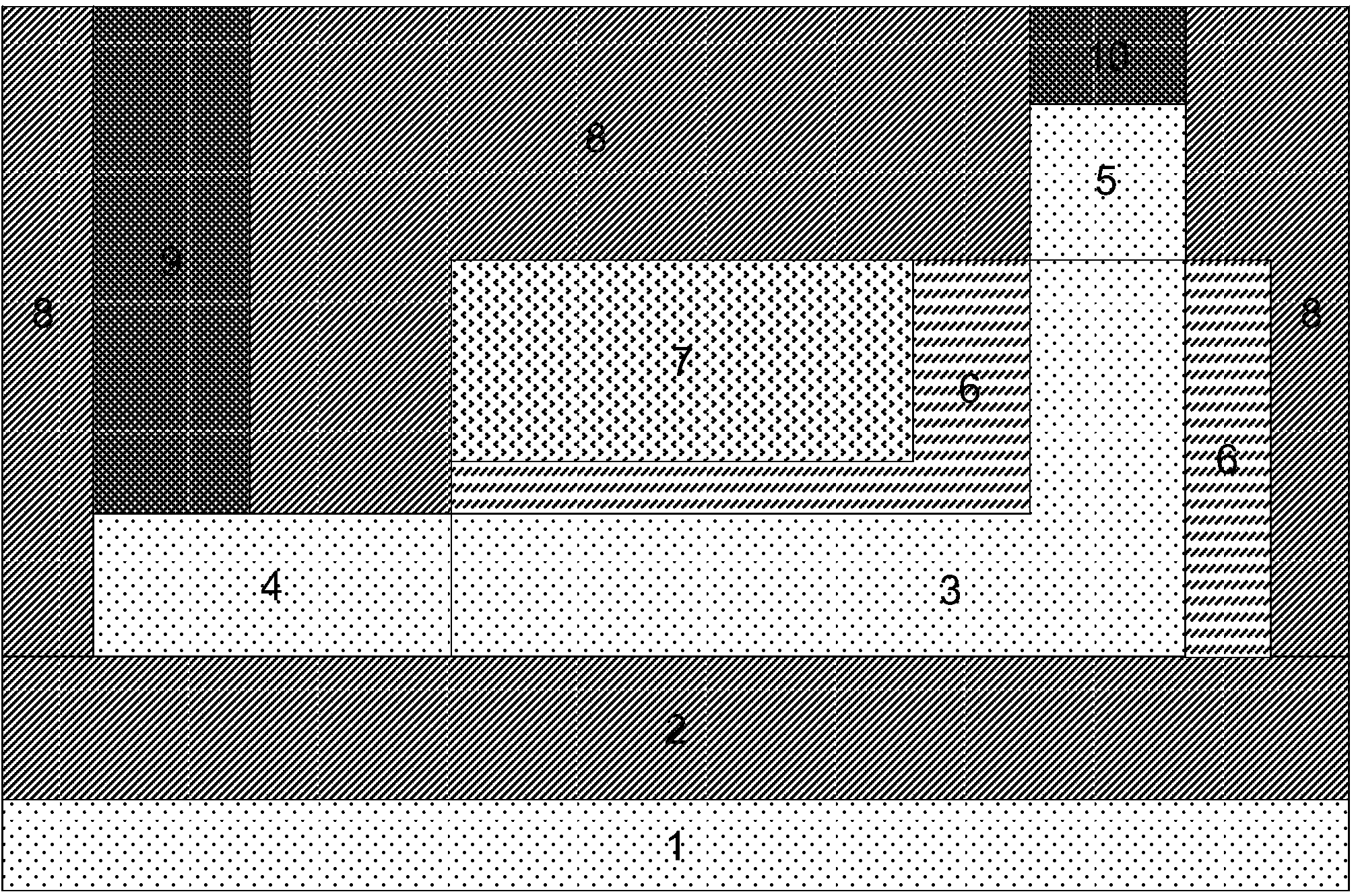

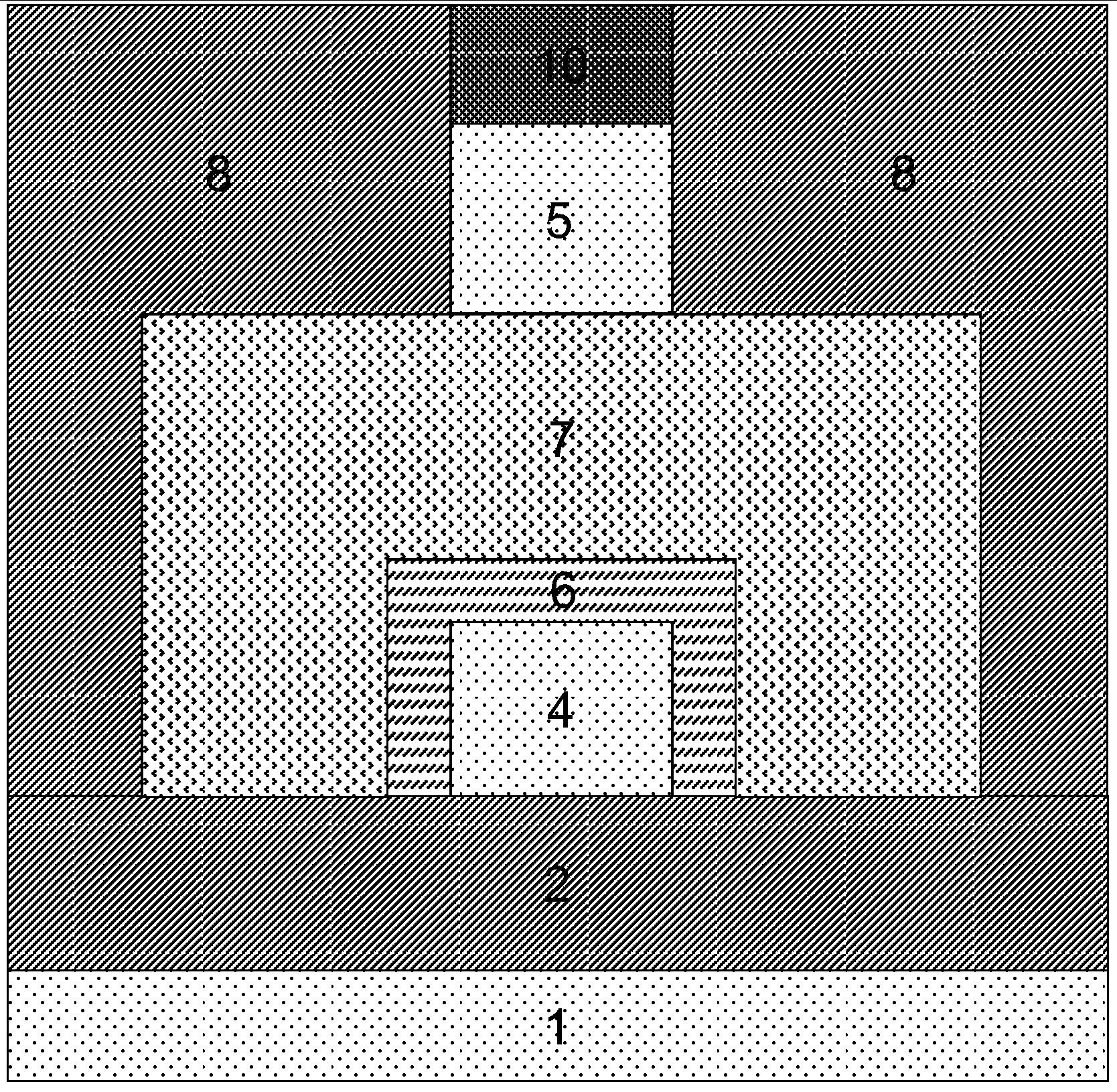

[0030] The folded gate electrode 7 is located above and on both sides of the horizontal part of the L-shaped intrinsic silicon 3, is isolated from the L-shaped intrinsic silicon 3 by the gate insulating layer 6, and has a control effect.

[0031] The thickness of the gate insulating layer 6 between the folded gate electrode 7 and the horizontal part of the L-shaped intrinsic silicon 3 is between 0.4 nanometers and 2 nanometers; between the folded gate electrode 7 and the vertical part of the L-shaped intrinsic silicon 3 The thickness of the intervening gate insulating layer 6 is between 2 nanometers and 4 nanometers.

[0032] The gate insulating layer 6 is an insulating medium with a high dielectric constant, and the insulating medium may be hafnium dioxide, silicon nitride, aluminum oxide and the like.

[0033] The dielectric constant of the insulating dielectric layer 8 is lower than that of the gate insulating layer 6 and may be silicon nitride, silicon dioxide or the like...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com