Growing method of light-emitting diode epitaxial wafer and light emitting diode epitaxial wafer

A technology for light emitting diodes and a growth method, which is applied in the field of light emitting diode epitaxial wafers, can solve the problems of little room for improving the luminous efficiency of the chip, cannot effectively improve the luminous efficiency of the chip, and increase the damage of the InGaN active layer, so as to avoid the working voltage. Raise, improve antistatic ability and reverse breakdown ability, improve the effect of light extraction efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

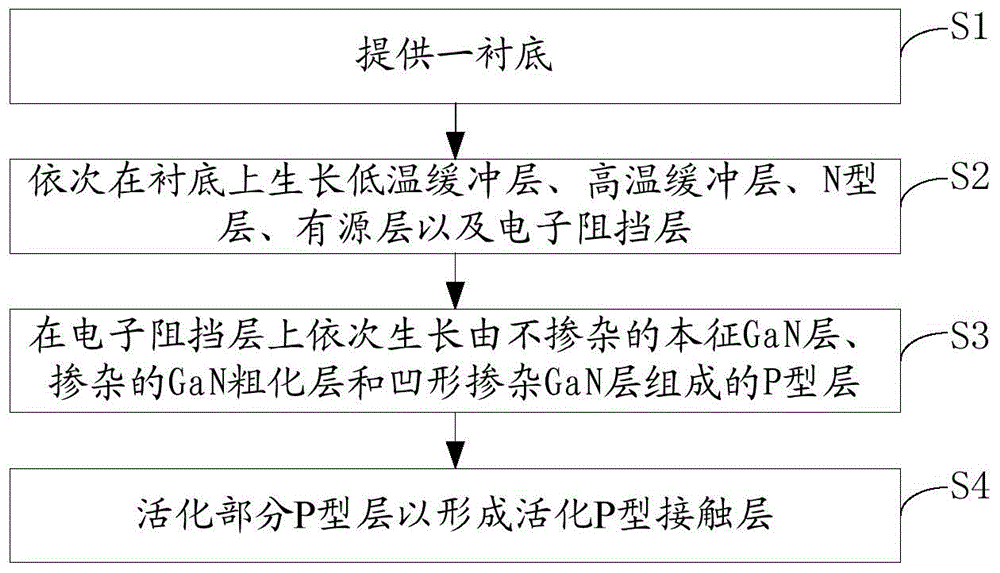

[0032] see figure 1 , an embodiment of the present invention provides a method for growing a light-emitting diode epitaxial wafer, the method comprising the following steps:

[0033] S1: providing a substrate;

[0034] Specifically, in this embodiment, the substrate may be sapphire. Before growing the epitaxial wafer, the substrate needs to be pretreated. The pretreatment operation includes: placing the substrate in a reaction chamber, and treating it at a high temperature under a hydrogen atmosphere. Substrate 5-6min. Wherein, the temperature of the reaction chamber is 1000-1100° C., and the pressure of the reaction chamber is controlled at 200-500 torr.

[0035] S2: growing a low-temperature buffer layer, a high-temperature buffer layer, an N-type layer, an active layer, and an electron blocking layer on the substrate in sequence;

[0036] Specifically, in this embodiment, Veeco K465i MOCVD (Metal Organic Chemical Vapor Deposition, Metal Organic Compound Chemical Vapor De...

Embodiment 2

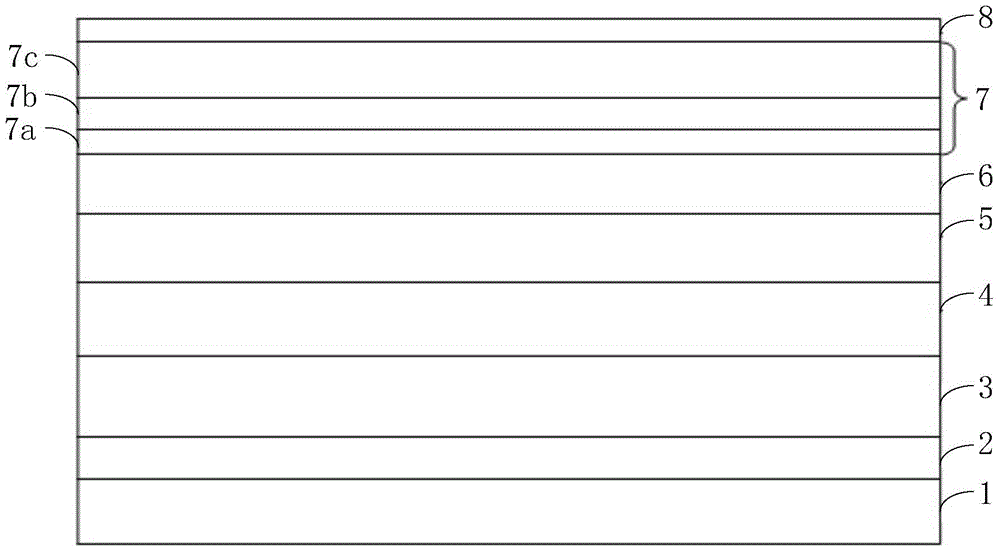

[0058] see figure 2 , the embodiment of the present invention provides a light-emitting diode epitaxial wafer, which is suitable for preparation by the method as in Example 1. The epitaxial wafer includes a substrate 1 and a low-temperature buffer layer 2, a high-temperature buffer layer 3, and N-type layer 4, active layer 5, electron blocking layer 6, P-type layer 7 and activated P-type contact layer 8, P-type layer 7 consists of undoped intrinsic GaN layer 7a, doped GaN rough layer 7b , concave-doped GaN layers 7c are sequentially stacked, the growth temperature of the concave-doped GaN layer 7c is higher than that of the intrinsic GaN layer 7a, and the growth temperature of the intrinsic GaN layer 7a is higher than that of the GaN roughened layer 7b,

[0059] The GaN rough layer 7b is doped with Mg of the first concentration, the concave doped GaN layer 7c is firstly doped with the second concentration of Mg, then with the third concentration of Mg, and finally with the fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More