A kind of low on-state loss igbt and its manufacturing method

A technology of on-state loss and manufacturing method, which is applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of poor safe working area and increased leakage, and reduce short-circuit current and on-state loss , Improve the effect of PIN area area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

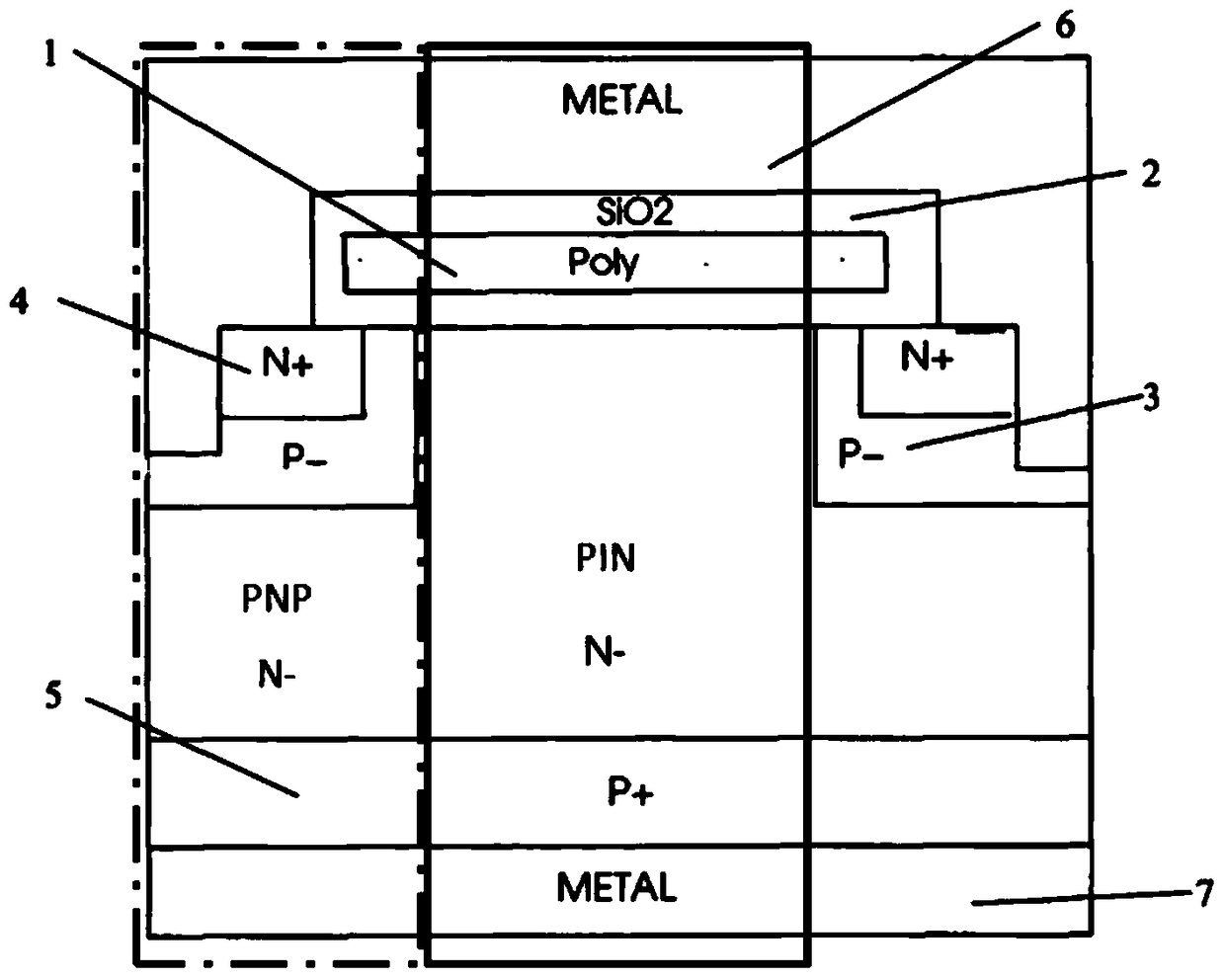

[0031] as attached Figure 4 As shown, the pattern of the pressure-resistant ring layer (PR) is changed, and the doping concentration of the P-base region is increased, so that the channel cannot be opened normally, and the channel becomes invalid. Empty cells are introduced in the IGBT active area. The left side of the graph is an empty cell structure, and the right side is a normal cell structure.

[0032] Preparation steps include:

[0033] 1) Preparation of the pressure-resistant ring layer (PR), including oxide layer growth, PR photolithography, PR implantation, and PR deglue;

[0034] 2) Active layer (OD) preparation, including field oxygen growth, OD photolithography, OD etching, and OD stripping;

[0035] 3) Preparation of polycrystalline layer (PS), including gate oxide growth, polycrystalline growth, polycrystalline doping, PS photolithography, PS etching, P well implantation, push junction, N+ source implantation, Spacer formation, anti-latch (latch -up) injecti...

Embodiment 2

[0041] as attached Figure 5 As shown, increasing the field oxygen layer (OD) pattern makes the channel current unable to be extracted and forms an empty cell structure in the IGBT active region. The left side of the graph is an empty cell structure, and the right side is a normal cell structure.

[0042] Preparation steps include:

[0043] 1) Active layer (OD) preparation, including field oxygen growth, OD photolithography, OD etching, and OD stripping;

[0044] 2) Preparation of polycrystalline layer (PS), including gate oxide growth, polycrystalline growth, polycrystalline doping, PS photolithography, PS etching, P well implantation, push junction, N+ source implantation, Spacer formation, anti-latch (latch -up) injection;

[0045] 3) Preparation of the contact layer (CO), including dielectric layer deposition, CO photolithography, CO etching, and CO debonding;

[0046] 4) Preparation of the metal layer (M1), including metal layer deposition, M1 photolithography, M1 cor...

Embodiment 3

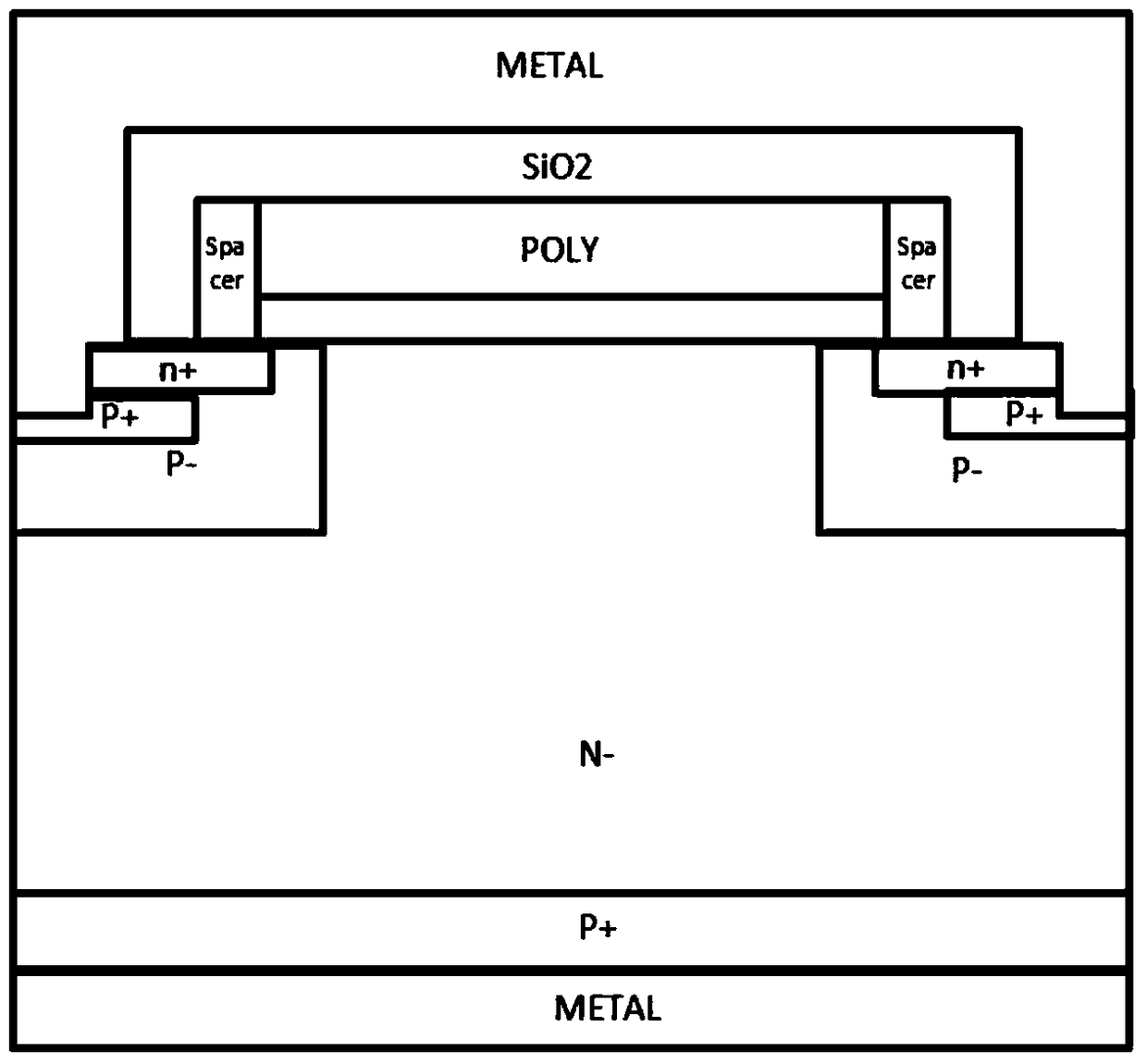

[0050] as attached Image 6 As shown, changing the polycrystalline layer (PS) pattern, isolating the polycrystalline layer from the gate signal, forming polycrystalline islands, making the channel unable to open, and forming an empty cell structure in the IGBT active region. The left side of the graph is an empty cell structure, and the right side is a normal cell structure.

[0051] Preparation steps include:

[0052] 1) Active layer (OD) preparation, including field oxygen growth, OD photolithography, OD etching, and OD stripping;

[0053] 2) Preparation of polycrystalline layer (PS), including gate oxide growth, polycrystalline growth, polycrystalline doping, PS photolithography, PS etching, P well implantation, push junction, N+ source implantation, Spacer formation, anti-latch (latch -up) injection;

[0054] 3) Preparation of the contact layer (CO), including dielectric layer deposition, CO photolithography, CO etching, and CO debonding;

[0055] 4) Preparation of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More