A method for preparing an organic semiconductor nanowire array conductive channel thin film transistor

A technology of organic semiconductors and thin film transistors, which is applied in the field of semiconductor nanomaterials and devices, can solve the problems of limited overall device performance, difficulty in meeting demands, and complex preparation processes, and achieve flexible and controllable device performance, lower threshold voltage, and simple preparation processes Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0028] The invention provides a method for preparing an organic semiconductor nanowire array conductive channel thin film transistor, which is sequentially prepared on a silicon / silicon dioxide substrate by using lift-off technology, spin-coating film-forming technology and capillary infiltration technology. A sacrificial layer ZnO strip array, a photoresist layer containing a nanowire hole array, and an organic semiconductor layer containing an organic nanowire array are formed, and metal electrodes are respectively formed on the organic semiconductor layer of the organic nanowire array and the back of the substrate. And lead out the corresponding source, drain and gate, so as to complete the preparation of organic semiconductor nanowire array conduction channel thin film transistor.

[0029] Further, in this embodiment, the following steps are also included:

[0030] Step S1: Preparation of sacrificial layer ZnO strip array: using sulfuric acid / hydrogen peroxide solution to ...

Embodiment 1

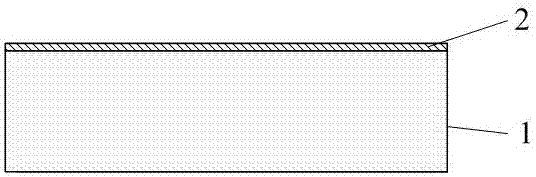

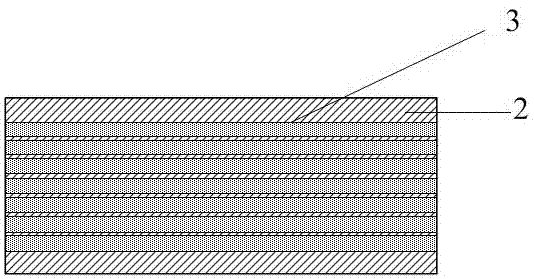

[0045] Step S1: Take a silicon / silicon dioxide substrate with a size of 1cm×1cm and an oxide layer thickness of 30nm, figure 1 It is a schematic diagram of the silicon / silicon dioxide substrate structure, where 1 is the substrate silicon, and 2 is the silicon dioxide film on the silicon surface. The silicon / silicon dioxide substrate was cleaned at high temperature in concentrated sulfuric acid / a small amount of hydrogen peroxide solution for 30 minutes, and a layer of photoresist was coated on the surface of the silicon / silicon dioxide substrate by a spin-coating process, and the photoresist was etched by an electron beam. The strip photoresist array is etched by etching technology, figure 2 Schematic diagram of the silicon / silicon dioxide substrate structure for preparing the sacrificial layer ZnO strip array, image 3 The top view of the silicon / silicon dioxide substrate structure for preparing the sacrificial layer ZnO strip array, wherein 1 is the substrate silicon, 2 is...

Embodiment 2

[0050] Step S1: Take a silicon / silicon dioxide substrate with a size of 1cm×1cm and an oxide layer thickness of 150nm, figure 1 It is a schematic diagram of the silicon / silicon dioxide substrate structure, where 1 is the substrate silicon, and 2 is the silicon dioxide film on the silicon surface. The silicon / silicon dioxide substrate was cleaned at high temperature in concentrated sulfuric acid / a small amount of hydrogen peroxide solution for 30 minutes, and a layer of photoresist was coated on the surface of the silicon / silicon dioxide substrate by a spin-coating process, and the photoresist was etched by an electron beam. The strip photoresist array is etched by etching technology, figure 2 Schematic diagram of the silicon / silicon dioxide substrate structure for preparing the sacrificial layer ZnO strip array, image 3 The top view of the silicon / silicon dioxide substrate structure for preparing the sacrificial layer ZnO strip array, wherein 1 is the substrate silicon, 2 i...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More