Method of forming mems devices

A device, wet etching technology, used in semiconductor/solid-state device parts, piezoelectric/electrostrictive/magnetostrictive devices, optical components, etc., can solve problems such as poor performance of MEMS devices, and improve the interface characteristics, to ensure accurate timing, to enhance the effect of adhesion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

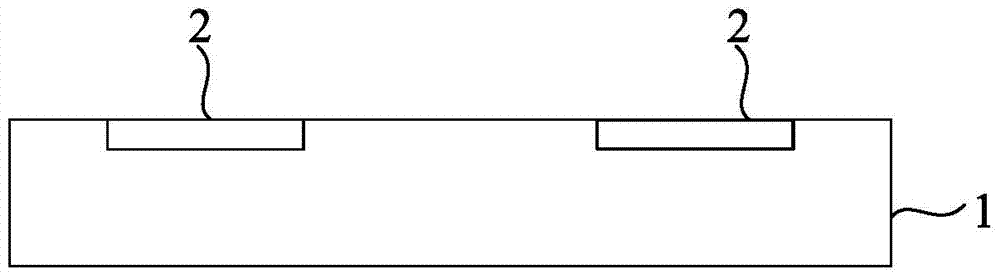

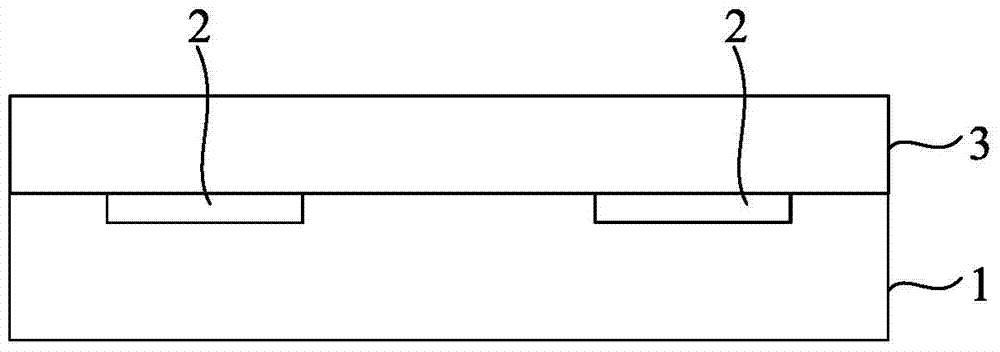

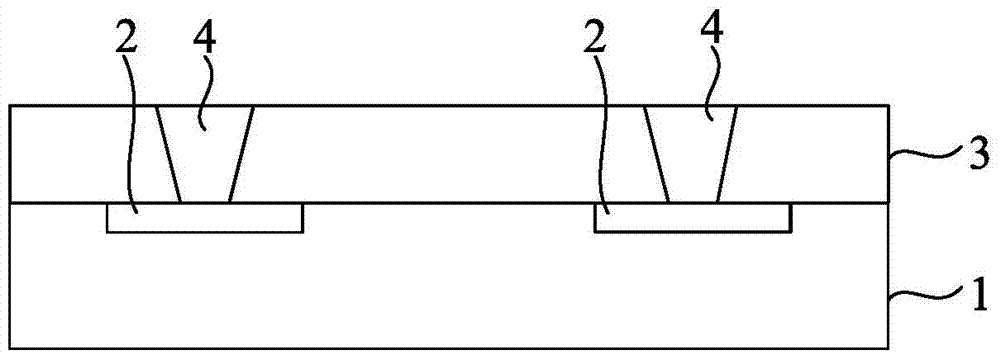

[0065] refer to figure 1 A substrate 1 is provided, and a CMOS device 2 is formed in the substrate 1. The CMOS device 2 is electrically connected to the MEMS device, and is used for outputting signals to the MEMS device and receiving signals output by the MEMS device. The MEMS device to be formed in this embodiment is a resonator or an oscillator, and the resonator will be used as an example for description below.

[0066] It should be noted, figure 1 Among them, the structure indicated by the label 2 is only used to characterize the position of the CMOS device, and cannot be used to describe the shape of the CMOS device.

[0067] In a specific embodiment, the substrate 1 may be a silicon substrate, or may be a germanium, silicon germanium, gallium arsenide or silicon-on-insulator substrate. Those skilled in the art can select the substrate according to needs, so the type of the substrate should not limit the protection scope of the present invention. The substrate 1 in t...

no. 2 example

[0088] The differences between this embodiment and the first embodiment are:

[0089] refer to Figure 11 After forming the SiGe layer 8 and the silicon oxide layer 9 on the SiGe layer 8 on the diffusion barrier layer 6 and in the first through hole, repeat the steps of forming the SiGe layer and thermal oxidation growth to form the silicon oxide layer at least once, so that A multi-layer SiGe layer 8 and a silicon oxide layer 9 are formed on the diffusion barrier layer 6 , wherein the SiGe layer 8 and the silicon oxide layer 9 are distributed vertically at intervals.

[0090] In specific embodiments, each thermal oxidation can be dry oxidation or wet oxidation. The gas used in the dry oxidation process is O 2 , O 3 one or both of them. The relevant parameters in the dry oxidation process are: the gas flow range is 100sccm-250sccm, the temperature range is 400°C-800°C, and the time range is 1min-3min. In this embodiment, the gas flow rate is less than the gas flow rate in...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| frequency temperature coefficient | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More