A Method for Optimizing CMOS Image Sensor Wafer Edge Defects

An image sensor, edge defect technology, used in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as inability to grow silicon nitride, affecting yield, and online defects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

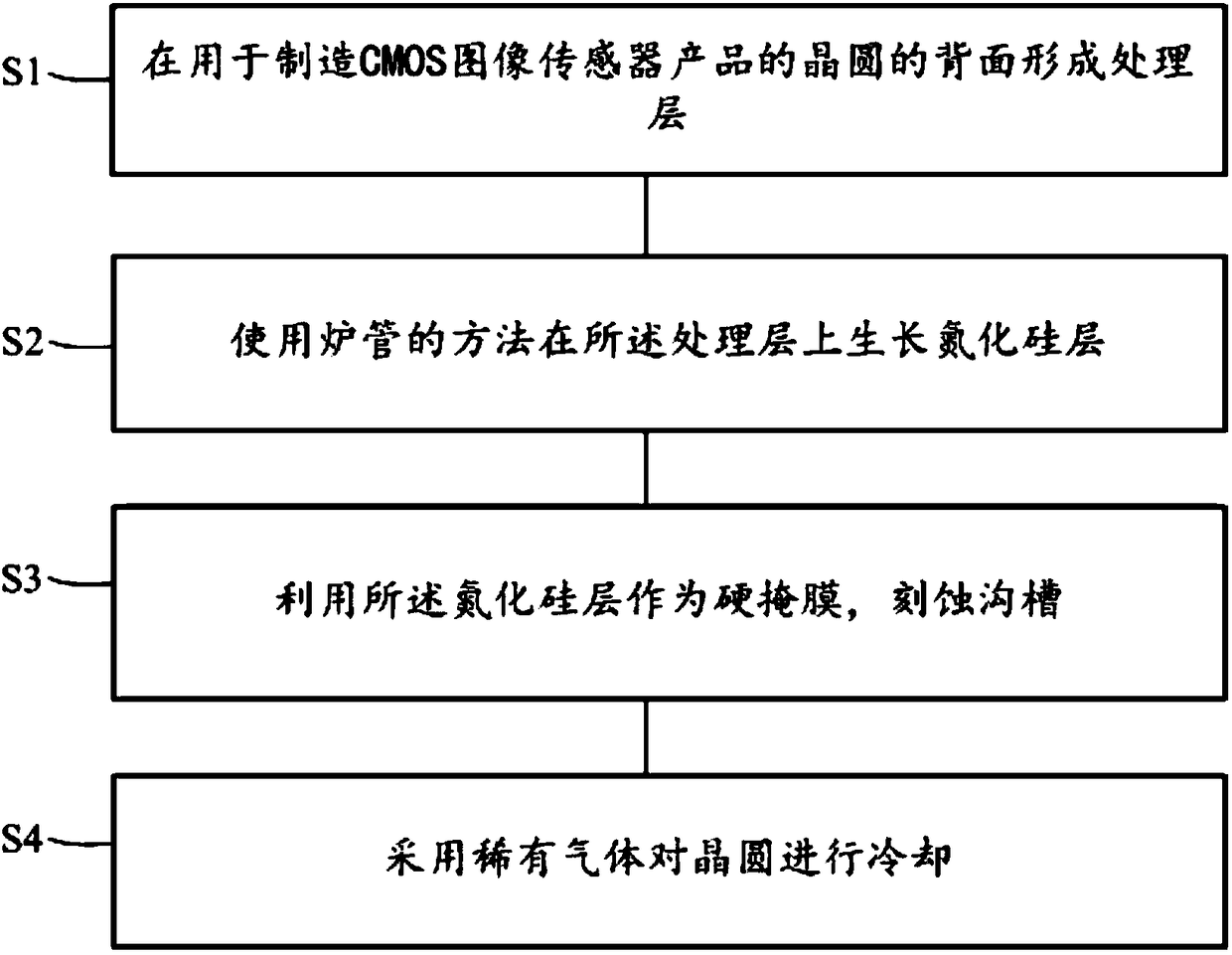

[0026] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

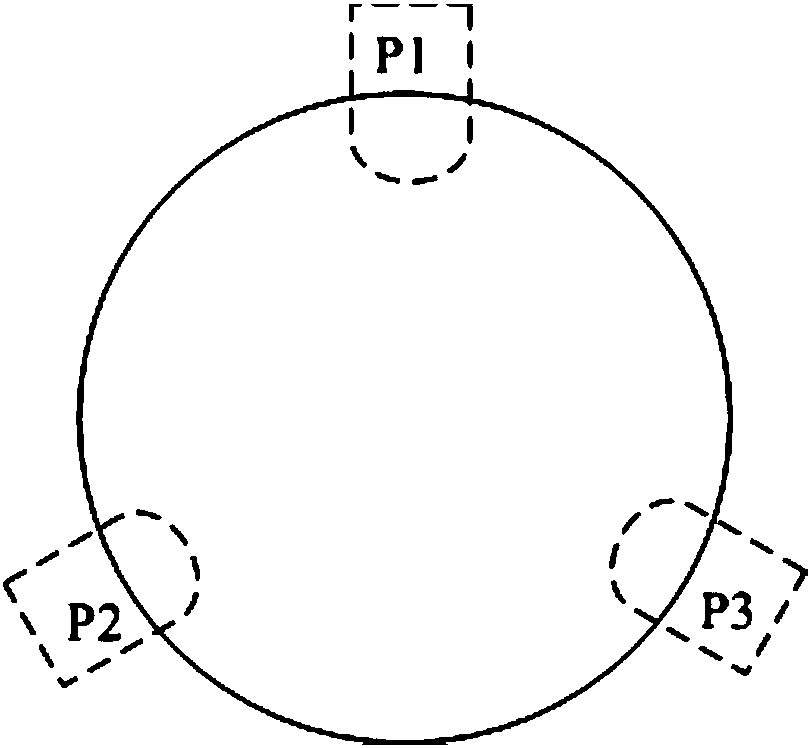

[0027] In the present invention, by changing the material of the low-temperature oxide on the back of the CMOS image sensor wafer to prevent metal contamination and reduce signal noise interference, it is optimized to a denser plasma-assisted oxide (PEOX, Plasma Enhanced Oxide) or chemical vapor phase Deposit nitride or a combination of these two films to prevent the small-sized low-temperature oxide silicon oxide particles produced by plasma bombardment on the back of the wafer during the shallow trench etching process from cooling the helium gas on the back of the wafer. The movement causes etch defects on the front side of the wafer. The invention greatly reduces online defects and improves product yield through optimization.

[0028] Prefer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More