Thermally-assisted field electron emission cathode structure and preparation method thereof

A field electron emission, cathode structure technology, applied in cold cathode manufacturing, electrode system manufacturing, discharge tube/lamp manufacturing, etc. The effect of simplicity, improved performance, wide application value

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

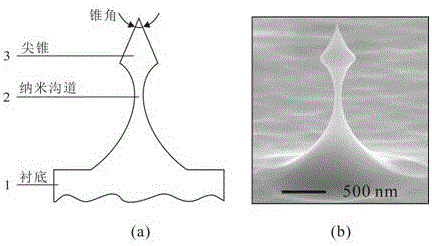

Image

Examples

Embodiment 1

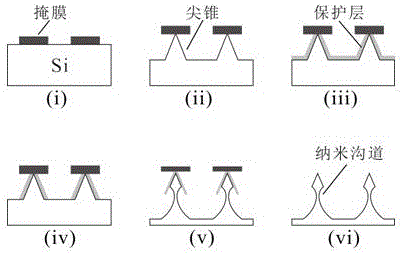

[0038] A preparation of a heat-assisted field electron emission cathode structure (the diameter or width of the narrowest part of the nanochannel is about 100 nm, and the corresponding resistance value is about 100 kΩ), including the following steps:

[0039] S1. On a clean silicon substrate, use a chemical vapor deposition system to deposit a silicon dioxide / silicon nitride mask layer with a thickness of 500-1000 nm on its surface;

[0040]S2. Spin-coat a photoresist (AR-N 7520) with a thickness of about 500-600 nm; use an electron beam lithography system to expose the photoresist; develop the exposed sample to obtain a center-to-center distance of 6 μm Circular or strip-shaped photoresist array, the diameter or width of the circle or strip can be 700-1500 nm;

[0041] S3. Use the plasma reactive etching system to etch the silicon dioxide / silicon nitride not protected by the photoresist until the silicon substrate is exposed, leaving the silicon dioxide / silicon nitride protec...

Embodiment 2

[0048] The experimental method is the same as that in Example 1, the only difference is that on the basis of preparing an emitter with a diameter or width of about 100 nm in the narrowest part of the nanochannel in S8, an additional step is added:

[0049] S81. Oxidize the sample obtained in S8 in an oxygen atmosphere at 900 °C for 50 min (the oxygen flow rate is 0.9 SLM), so that the diameter or width of the narrowest part of the nanochannel is reduced to about 70 nm (the corresponding resistance value is about is 1 MΩ), and the surface oxide layer was removed with a mixed solution of deionized water and hydrofluoric acid with a volume ratio of 5:1.

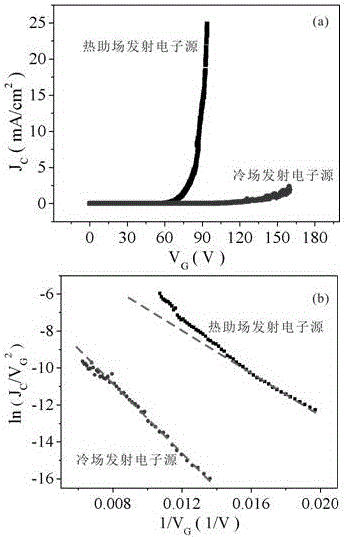

[0050] A silicon emitter array (40 × 40) with a diameter of about 70 nm in the narrowest part of the nanochannel was prepared using the above process. As a comparison, the inventors also fabricated a conventional nanochannel-free silicon tip array (40×40). The spacing between emitters in the array was all 6 μm. The gate is int...

Embodiment 3

[0052] The experimental method is the same as in Example 1, the only difference is that step S1 directly selects a substrate covered with 300 nm of silicon dioxide, or directly selects a substrate covered with 100 nm of alumina.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More