Nanowire array preparation method, nanowire array integrated device and preparation method thereof

A nanowire array and integrated device technology, which is applied in semiconductor/solid-state device manufacturing, nanotechnology, semiconductor devices, etc., can solve the problems of cumbersome steps, lower yield, and uncontrollability, so as to simplify the manufacturing process and improve yield , the effect of improving controllability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

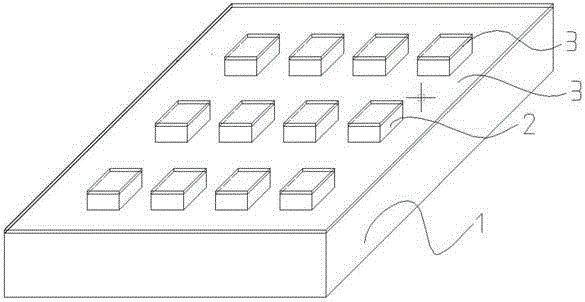

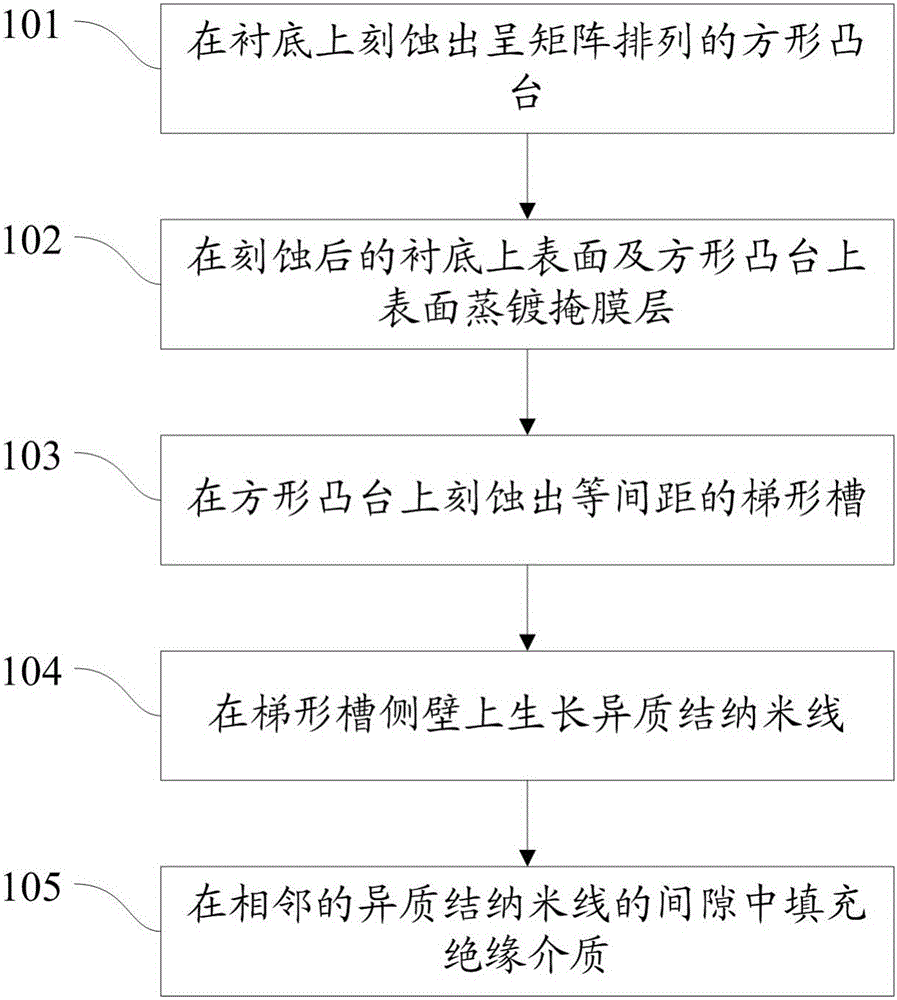

[0062] figure 1 An overall flowchart of a method for preparing a nanowire array provided by the present invention; as figure 1 As shown, a method for preparing a nanowire array provided by the present invention includes:

[0063] Step 101: etching square bosses arranged in a matrix on the substrate; the substrate is a single crystal silicon substrate;

[0064] Step 102: evaporating a mask layer on the etched upper surface of the substrate and the upper surface of the square boss; the mask layer is a silicon dioxide layer with a thickness of 100-200 nm;

[0065] Step 103: Etching equidistant trapezoidal grooves on the square boss;

[0066] Step 104: growing heterojunction nanowires on the sidewalls of the trapezoidal groove;

[0067] Specifically, first put the substrate with etched trapezoidal groove into the reaction chamber of metal organic chemical vapor deposition system, and grow an AlN buffer layer on the side wall of the trapezoidal groove to reduce the stress of the...

Embodiment 2

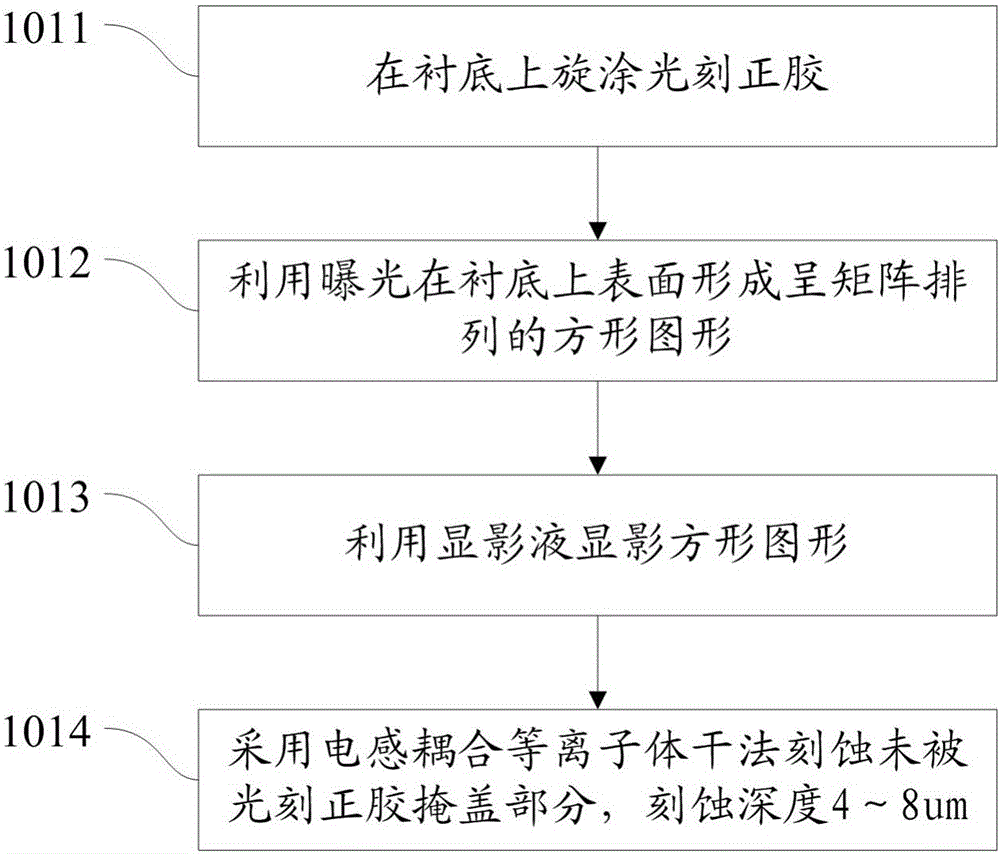

[0093] Embodiment 2: combined reference Figure 5-9 , using photoresist as a mask, combining photolithography technology and ICP technology to prepare a square boss 2, the height of the square boss 2 is 4-8um.

[0094] Evaporate a silicon dioxide mask layer 3 with a thickness of 100 to 200 nm on the surface of the substrate 1, use acetone and isopropanol to ultrasonically clean and dry the surface of the silicon dioxide mask layer 3, and spin coat on the mask layer 3 Photoresist positive resist; then use a set spacing equal-spaced stripe photolithography plate for exposure, the stripe spacing is 3-6um; then develop, remove the exposed photoresist positive resist, and the remaining photoresist forms a stripe pattern; use BOE The silicon dioxide mask layer 3 not covered by the photoresist is etched with a solution, and the etching depth is exactly 100-200 nm in thickness of the mask layer 3; then the KOH solution wet-etches the part not covered by the mask layer 3, and the etche...

Embodiment 3

[0098] Embodiment 3, in conjunction with reference Figure 5-9 , using photoresist as a mask, combining photolithography technology and ICP technology to prepare a square boss 2, the height of the square boss 2 is 4-8um.

[0099] Evaporate a silicon dioxide mask layer 3 with a thickness of 100 to 200 nm on the surface of the substrate 1, use acetone and isopropanol to ultrasonically clean and dry the surface of the silicon dioxide mask layer 3, and spin coat on the mask layer 3 Photoresist positive resist; then use a set spacing equal-spaced stripe photolithography plate for exposure, the stripe spacing is 3-6um; then develop, remove the exposed photoresist positive resist, and the remaining photoresist forms a stripe pattern; use BOE The silicon dioxide mask layer 3 not covered by the photoresist is etched with a solution, and the etching depth is exactly 100-200 nm in thickness of the mask layer 3; then the KOH solution wet-etches the part not covered by the mask layer 3, an...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More