Thin-film transistor structure visible blind photodetector and preparation method thereof

A technology of thin film transistors and photodetectors, applied in semiconductor devices, sustainable manufacturing/processing, circuits, etc., can solve the problems of low UV-visible light suppression ratio, high preparation cost, complicated process, etc., and achieve high suppression ratio and excellent preparation process Simple, enhanced photoelectric response effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

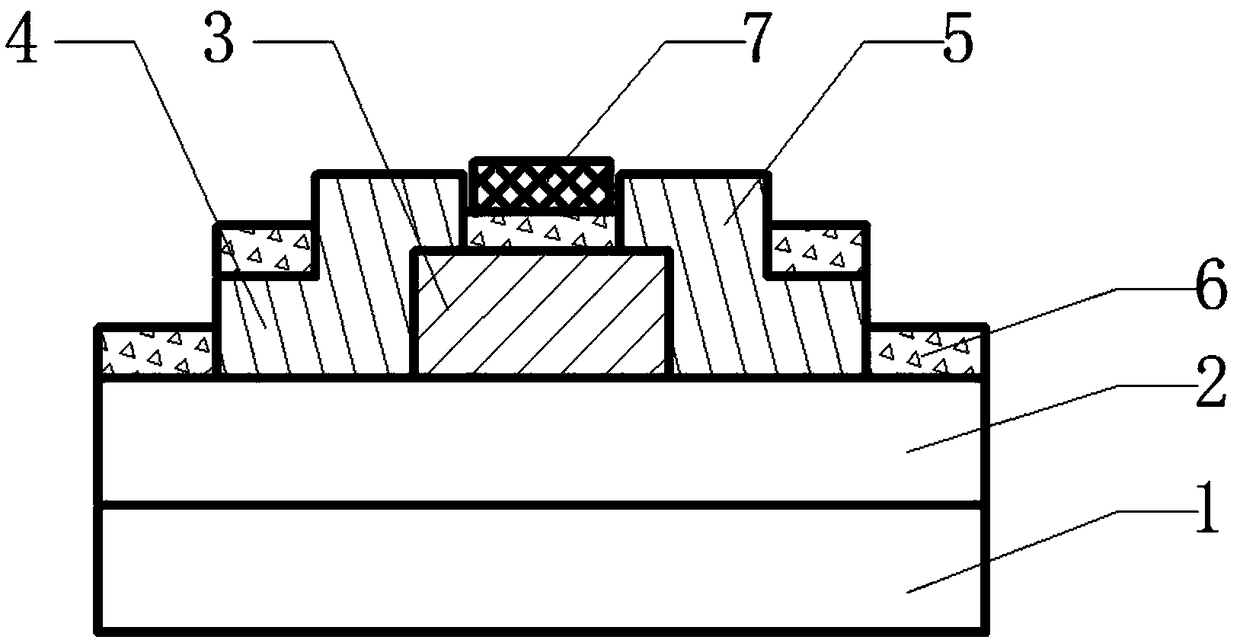

[0032] FIG. 2 is a flow chart of a method for fabricating a thin film transistor visible-blind photodetector according to an embodiment of the present application. As shown in Figure 2, the preparation method comprises:

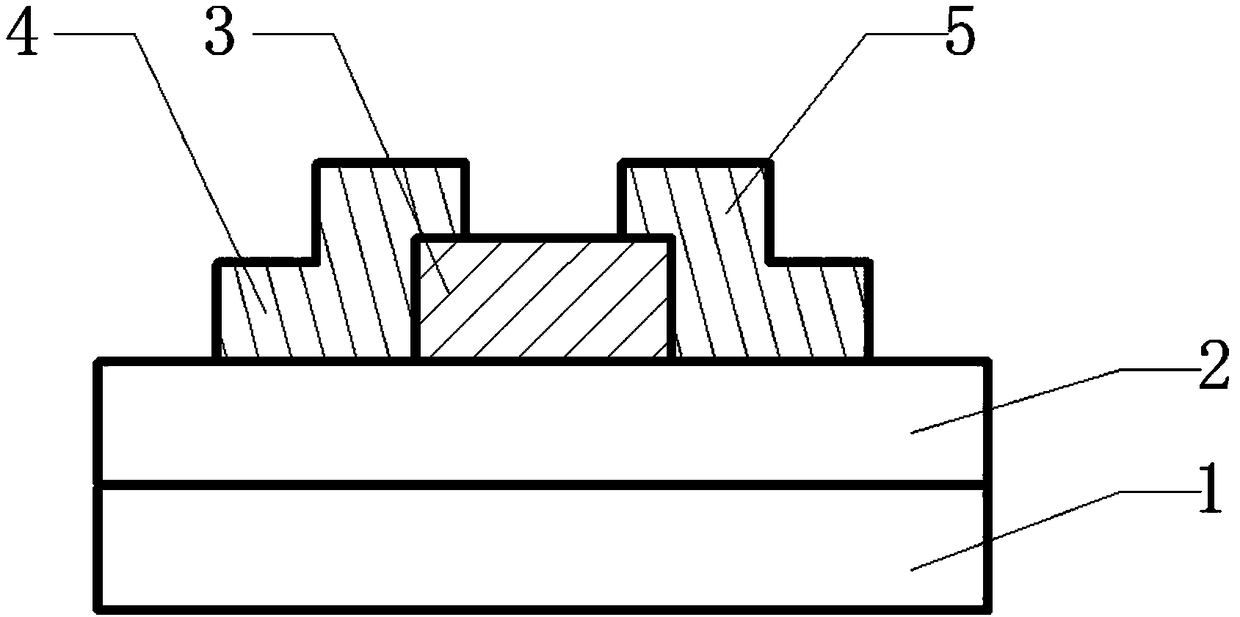

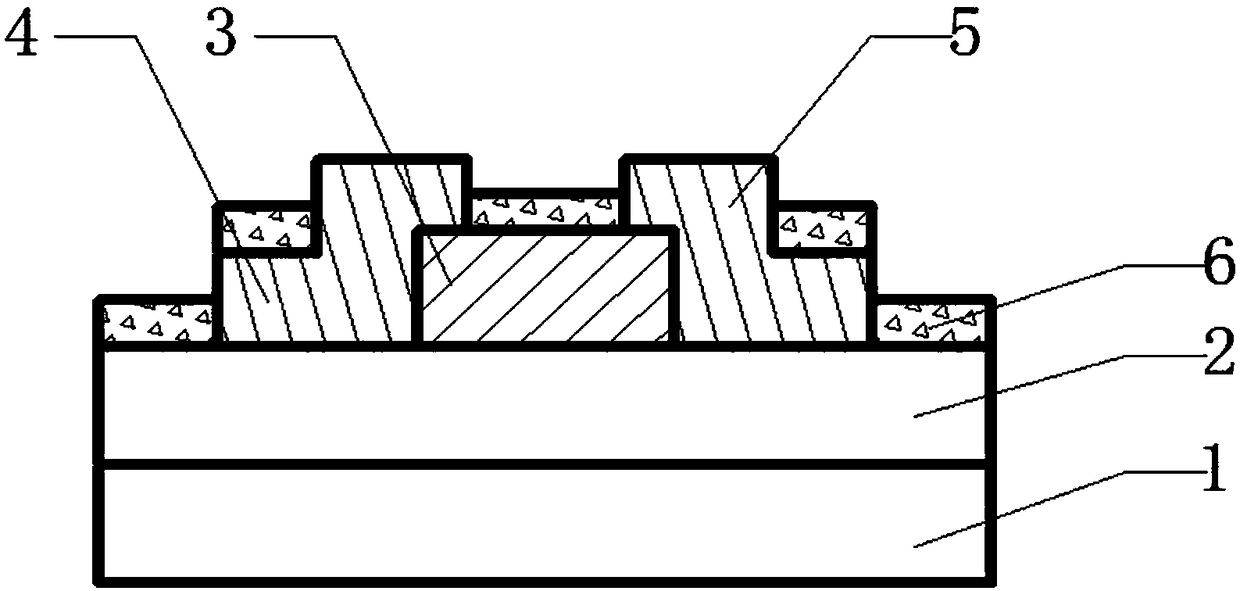

[0033] Step 1: Fabrication of Thin Film Transistors

[0034] Thermally oxidized silicon wafers (SiO) produced by the 46th Research Institute of China Electronics Technology Group Corporation 2 / p+Si(100)) as the substrate, the gate is highly doped p-type Si, the thickness is 375±15um, and the gate dielectric layer is SiO 2 , with a thickness of 100±20nm.

[0035] Use high-temperature tape to attach a mask plate with a width-to-length ratio of 800um:200um on the surface of the gate dielectric, and deposit a semiconductor channel layer in a magnetron sputtering apparatus. The target used is an indium gallium zinc oxide target (IGZO target, In 2 o 3 : Ga 2 o 3 :ZnO=1:1:1), the temperature is controlled at room temperature, the sputtering power is 60W, the...

Embodiment 1

[0049] (1) Preparation of IGZO thin film transistors

[0050] (1.1) Thermally oxidized silicon wafers (SiO 2 / p+Si(100)) as the substrate, the gate is highly doped p-type Si, the thickness is 375±15um, and the gate dielectric layer is SiO 2 , with a thickness of 100±20nm. Use high-temperature tape to attach a mask plate with a width-to-length ratio of 800um:200um on the surface of the gate dielectric, and deposit a semiconductor channel layer in a magnetron sputtering apparatus. The temperature is controlled at room temperature, the sputtering power is 60W, and the sputtering time is It takes about 25 minutes. During the sputtering process, the flow ratio of argon and oxygen into the chamber of the magnetron sputtering instrument is 6sccm:0sccm, the gas pressure in the chamber is 0.19pa, and the thickness of the deposited semiconductor channel layer is approximately 45nm.

[0051] (1.2) After the semiconductor channel layer is deposited, the source electrode and the drain el...

Embodiment 2

[0062] Example 2 adopts the same preparation process as Example 1, except that the deposited thickness is 8nm when electron beam evaporation is used to prepare the tin oxide thin film, that is, the covering layer.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More