High-linearity broadband stacking low noise amplifier based on gain compensation technology

A low-noise amplifier and low-noise amplification technology, which is applied in field-effect transistor RF low-noise amplifiers and integrated circuits, can solve the problems of increasing chip cost, low amplifier power consumption, large chip area, etc., achieve good input and output matching, and facilitate gain Compression compensation, the effect of improving the linearity index

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The principles and features of the present invention are described below in conjunction with the accompanying drawings, and the examples given are only used to explain the present invention, and are not intended to limit the scope of the present invention.

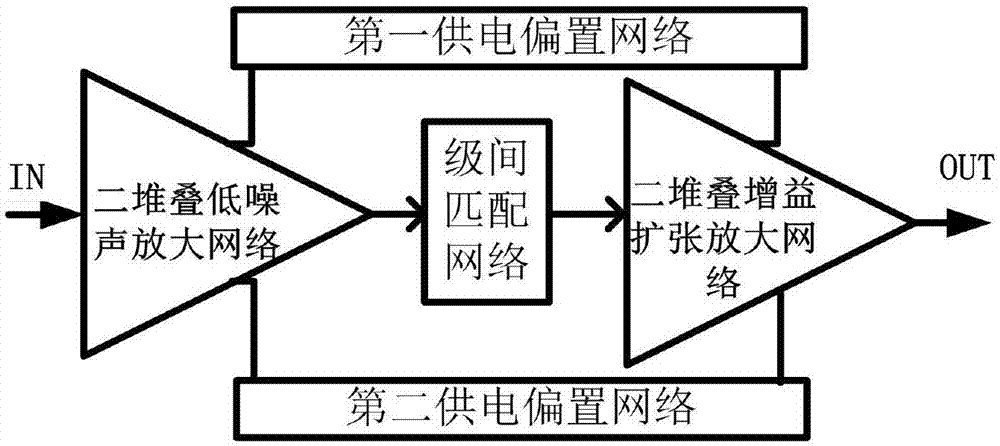

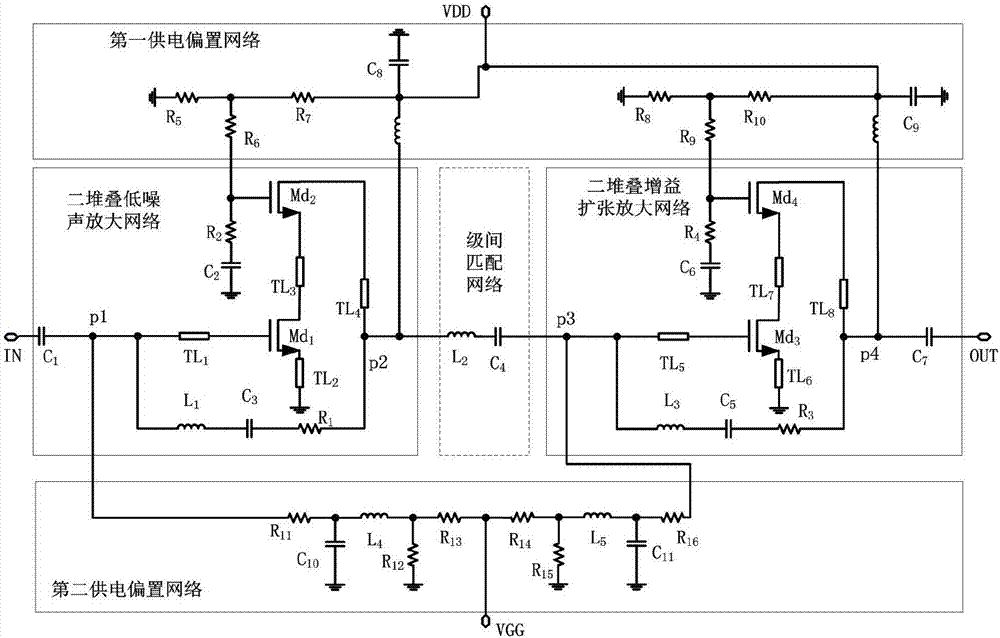

[0033] like figure 1 , figure 2 As shown, the present invention provides a high-linearity broadband stacked low-noise amplifier based on gain compensation technology, which is an ultra-wideband high-linearity stacked low-noise amplifier with two stacked low-noise amplifying networks and two-stacked gain expansion amplifying networks as the core Amplifiers, designed using integrated circuit technology.

[0034] The low noise amplifier includes two stacked low noise amplifying networks, an interstage matching network and two stacking gain expansion amplifying networks connected in sequence; and the first power supply connected to the two stacking low noise amplifying networks and the two stacking gain expanding ampl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com