N type double face battery preparation method

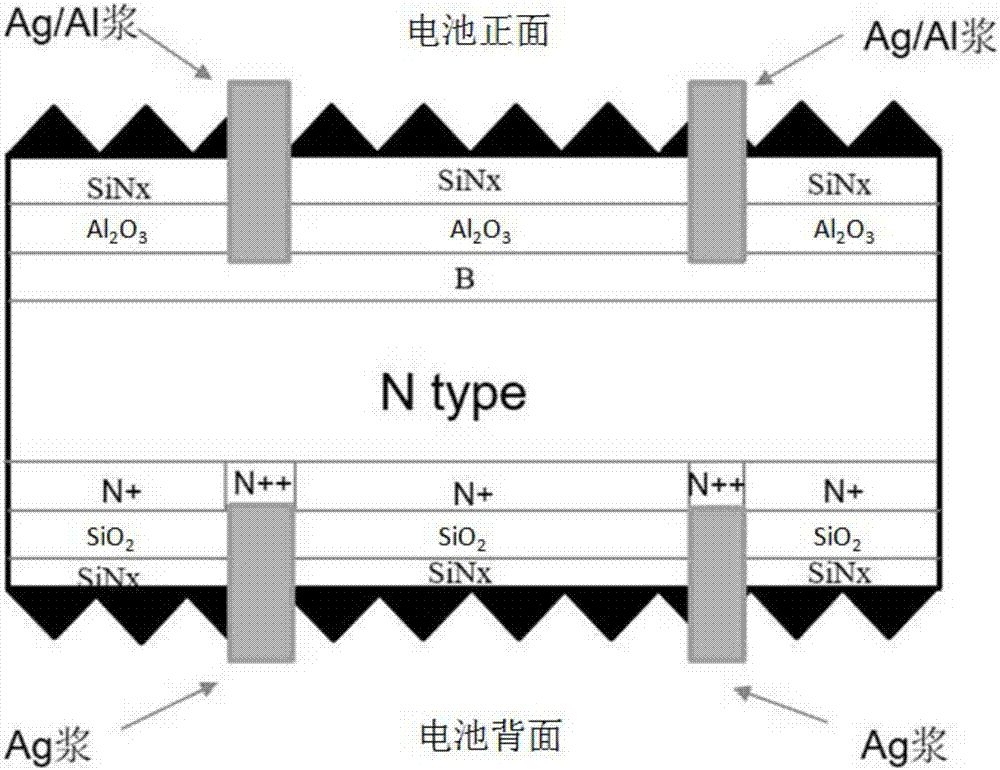

A double-sided cell, N-type technology, applied in the field of solar cells, can solve the problems of affecting the photoelectric conversion efficiency of double-sided cells, incomplete suede structure on the back, and reduced passivation quality, and achieve a uniform front and back nano suede structure, Excellent light trapping performance, improve the effect of FF

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0031] An embodiment of the present invention provides a method for preparing an N-type double-sided battery, including:

[0032] S11, performing damage treatment on the surface of the N-type silicon wafer;

[0033] Wherein, the damage treatment method can adopt conventional means, for example, treating the N-type silicon wafer with KOH solution to control the weight loss of the silicon wafer to 0.6-0.7 g.

[0034] S12, performing double-sided reactive ion etching on the N-type silicon wafer, so as to prepare a nano-textured surface on the surface of the N-type silicon wafer;

[0035] S13, performing boron diffusion on the front side of the N-type silicon wafer after the back side of the N-type silicon wafer is treated with a SiOx-SiNy mask;

[0036] S14, after removing the SiOx-SiNy mask layer on the back side of the N-type silicon wafer with an HF solution, performing a SiOx-SiNy mask on the front side of the N-type silicon wafer;

[0037] S15, performing SiO on the back s...

Embodiment 1

[0050] A method for preparing an N-type double-sided battery, comprising:

[0051] S21, performing damage treatment on the surface of the N-type silicon wafer;

[0052] S22, performing double-sided reactive ion etching on the N-type silicon wafer to prepare a nano-textured surface on the surface of the N-type silicon wafer, wherein the reflectivity of the N-type silicon wafer is controlled at 5%;

[0053] S23, after treating the back side of the N-type silicon wafer with a SiOx-SiNy mask, perform boron diffusion on the front side of the N-type silicon wafer, wherein the boron diffusion temperature is 950°C, and the square resistance is controlled at 85-95Ω / Square.;

[0054] S24, after removing the SiOx-SiNy mask layer on the back side of the N-type silicon wafer with an HF solution, and then performing a SiOx-SiNy mask on the front side of the N-type silicon wafer;

[0055] S25, performing SiO on the back side of the N-type silicon wafer 2 layer growth, where the SiO 2 Th...

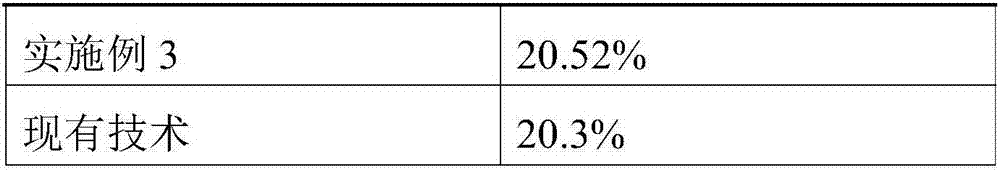

Embodiment 2

[0062] A method for preparing an N-type double-sided battery, comprising:

[0063] S31, performing damage treatment on the surface of the N-type silicon wafer;

[0064] S32, performing double-sided reactive ion etching on the N-type silicon wafer to prepare a nano-textured surface on the surface of the N-type silicon wafer, wherein the reflectivity of the N-type silicon wafer is controlled at 3%;

[0065] S33, after treating the back side of the N-type silicon wafer with a SiOx-SiNy mask, performing boron diffusion on the front side of the N-type silicon wafer, wherein the boron diffusion temperature is 900° C., and the square resistance is controlled at 80Ω / Squar. ;

[0066] S34, after removing the SiOx-SiNy mask layer on the back side of the N-type silicon wafer with an HF solution, and performing a SiOx-SiNy mask on the front side of the N-type silicon wafer;

[0067] S35, performing SiO on the back side of the N-type silicon wafer 2 layer growth, where the SiO 2 The th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More