Method for improving alignment accuracy of lithographic marks, method for preparing superjunction products, and superjunction products

A technology of alignment accuracy and lithographic marking, which is applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device testing/measurement, electrical components, etc., can solve the problem that the quality of the epitaxial layer is difficult to guarantee, the lithography machine is difficult to automatically identify, and the product is affected Production efficiency and other issues, achieve the effect of high alignment accuracy of lithography marks, reduce the number of lithography times, and reduce the probability of contamination

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0067] A method of improving alignment accuracy of lithographic marks comprising the steps of:

[0068] (a) performing the first epitaxial growth on the substrate to form a first epitaxial layer to obtain an epitaxial wafer; the thickness of the first epitaxial layer is 10 μm;

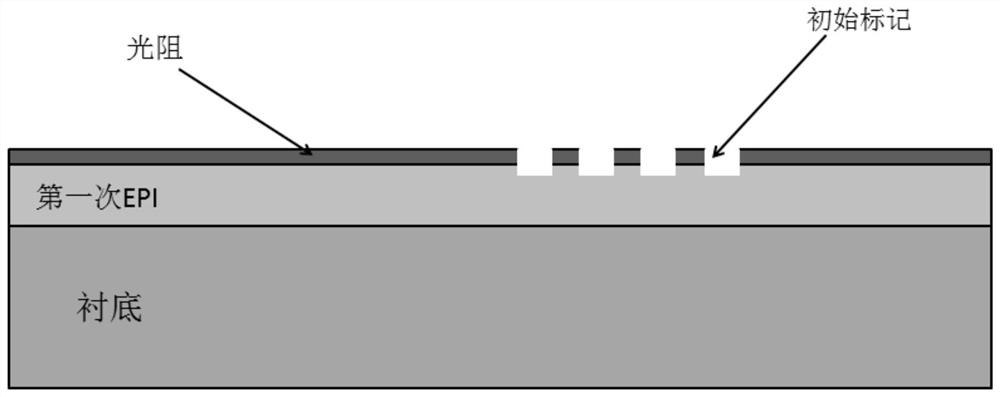

[0069] (b) performing photolithography and etching on the epitaxial wafer to form an initial mark to obtain an epitaxial wafer with an initial mark; the depth of the initial mark is 0.5 μm;

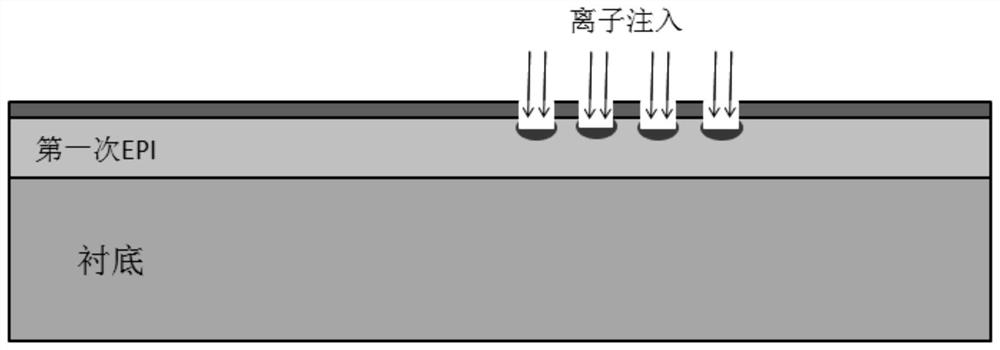

[0070] (c) Perform ion implantation on the epitaxial wafer with the initial mark, the ion implantation position is the bottom of the initial mark, and the implanted ion element is at least one kind;

[0071] (d) performing a second epitaxial growth on the first epitaxial layer to form a second epitaxial layer; the thickness of the second epitaxial layer is 6 μm;

[0072] (e) performing a third epitaxial growth on the second epitaxial layer to form a third epitaxial layer; the thickness of the third epitaxial laye...

Embodiment 2

[0075] A method of improving alignment accuracy of lithographic marks comprising the steps of:

[0076] (a) performing the first epitaxial growth on the substrate to form a first epitaxial layer to obtain an epitaxial wafer; the thickness of the first epitaxial layer is 20 μm;

[0077] (b) performing photolithography and etching on the epitaxial wafer to form an initial mark to obtain an epitaxial wafer with an initial mark; the depth of the initial mark is 0.5 μm;

[0078] (c) Perform ion implantation on the epitaxial wafer with the initial mark, the ion implantation position is the bottom of the initial mark, and the implanted ion element is at least one kind;

[0079] (d) performing a second epitaxial growth on the first epitaxial layer to form a second epitaxial layer; the thickness of the second epitaxial layer is 12 μm;

[0080] (e) performing a third epitaxial growth on the second epitaxial layer to form a third epitaxial layer; the thickness of the third epitaxial lay...

Embodiment 3

[0083] A method of improving alignment accuracy of lithographic marks comprising the steps of:

[0084] (a) performing the first epitaxial growth on the substrate to form a first epitaxial layer to obtain an epitaxial wafer; the thickness of the first epitaxial layer is 15 μm;

[0085] (b) performing photolithography and etching on the epitaxial wafer to form an initial mark to obtain an epitaxial wafer with an initial mark; the depth of the initial mark is 0.5 μm;

[0086] (c) Perform ion implantation on the epitaxial wafer with the initial mark, the ion implantation position is the bottom of the initial mark, and the implanted ion element is at least one kind;

[0087] (d) performing a second epitaxial growth on the first epitaxial layer to form a second epitaxial layer; the thickness of the second epitaxial layer is 10 μm;

[0088] (e) performing a third epitaxial growth on the second epitaxial layer to form a third epitaxial layer; the thickness of the third epitaxial lay...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| electrical resistivity | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More