Fabrication method of ultra-thin silicon transfer plate without temporary bonding and un-bonding processes

A production method and temporary bonding technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of colloid residual pollution, high equipment cost, and many process steps, and achieve low process cost and high reliability , The effect of low process difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

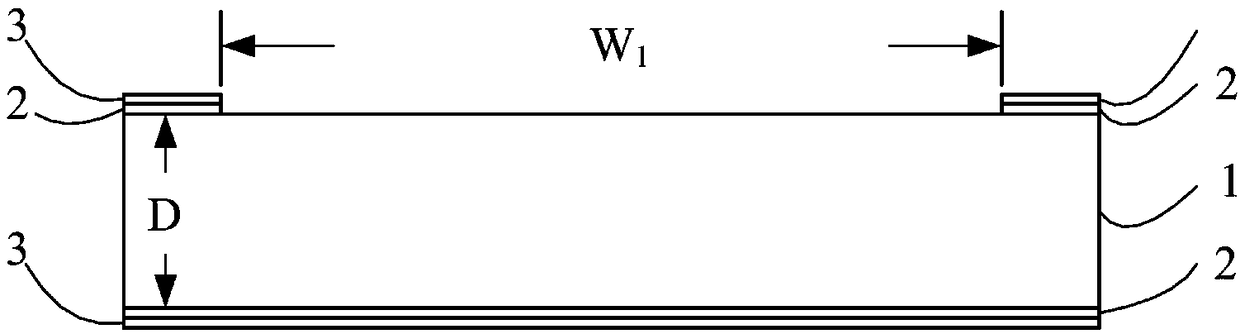

[0047] A method for making an ultra-thin silicon adapter plate without temporary bonding, which is suitable for making an ultra-thin silicon adapter plate. The thickness range of the obtained ultra-thin silicon adapter plate is between 50-200 μm, and the area is 25mm×25mm , the wiring width is more than 1 μm, and the through-silicon via has a diameter of more than 30 μm, and the said through-silicon via is only used for side wall metallization and has no solid hole feature.

[0048] As a specific embodiment, in this embodiment, an ultra-thin silicon interposer board with a thickness of 150 μm, an area of 25 mm×25 mm, a wiring width of 20 μm, and a TSV diameter of 60 μm is taken as an example for illustration.

[0049] In this embodiment, the side of the ultra-thin silicon interposer silicon chip where the chip circuit is arranged is called the front side, and the other side opposite to the chip circuit is called the back side.

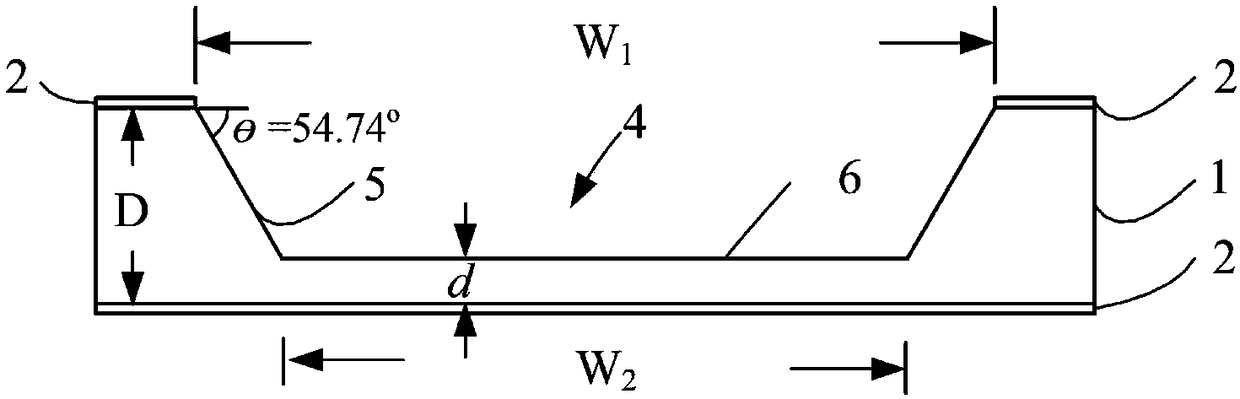

[0050] The manufacturing method of the ultra-t...

Embodiment 2

[0074] The difference between this embodiment and embodiment 1 is that the process methods of step 3 and step 10 are adjusted, and other steps are the same as embodiment 1. Compared with Embodiment 1, this embodiment is more suitable for making an ultra-thin silicon interposer with a thickness less than 100 μm.

[0075] As a specific embodiment, in this embodiment, an ultra-thin silicon interposer board with a thickness of 50 μm, an area of 25 mm×25 mm, a wiring line width of 20 μm, and a TSV diameter of 60 μm is taken as an example for illustration.

[0076] In step 3 of this embodiment, a silicon cavity 4 with a depth of 180 μm is manufactured, that is, the thickness d of the functional region of the interposer board obtained is 100 μm.

[0077] Step 10 of this embodiment specifically includes:

[0078] On the front side of the silicon wafer 1, spray glue to form a photoresist protective layer; on the back side of the silicon wafer 1, remove the silicon dioxide layer on t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More