SPAD with high detection efficiency and low dark count based on standard CMOS process

A detection efficiency and process technology, applied in the direction of electrical components, circuits, semiconductor devices, etc., can solve the problem that the detection efficiency is only 15%, achieve the effects of reducing tunneling dark counts, facilitating light absorption, and reducing electrical crosstalk

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

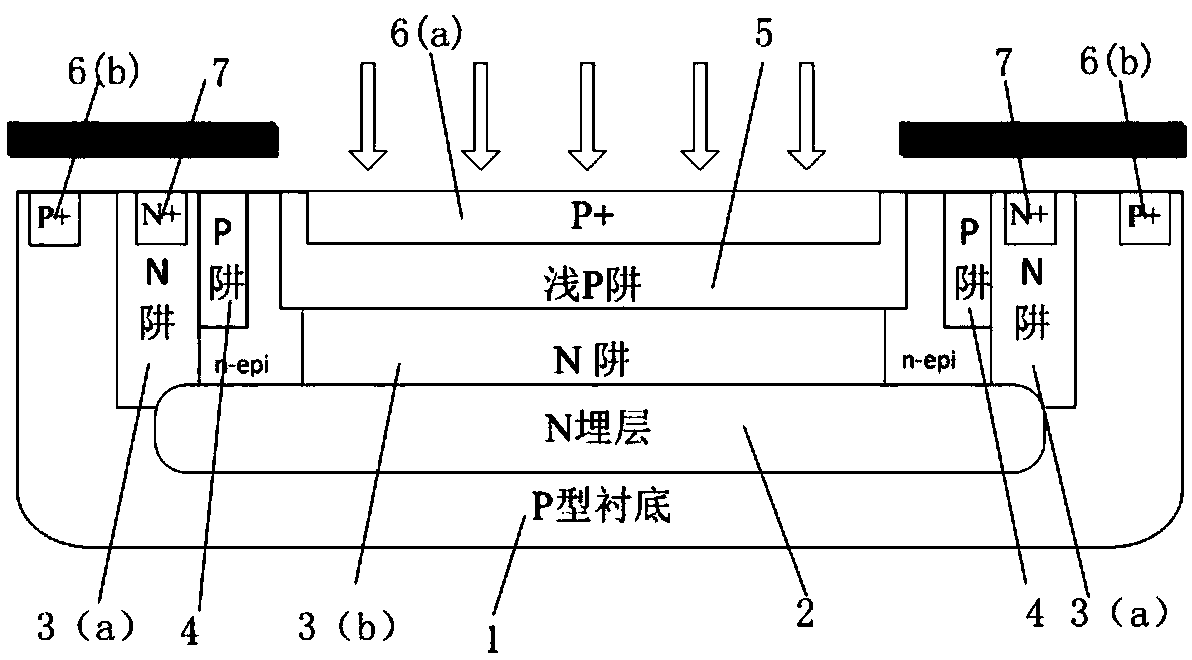

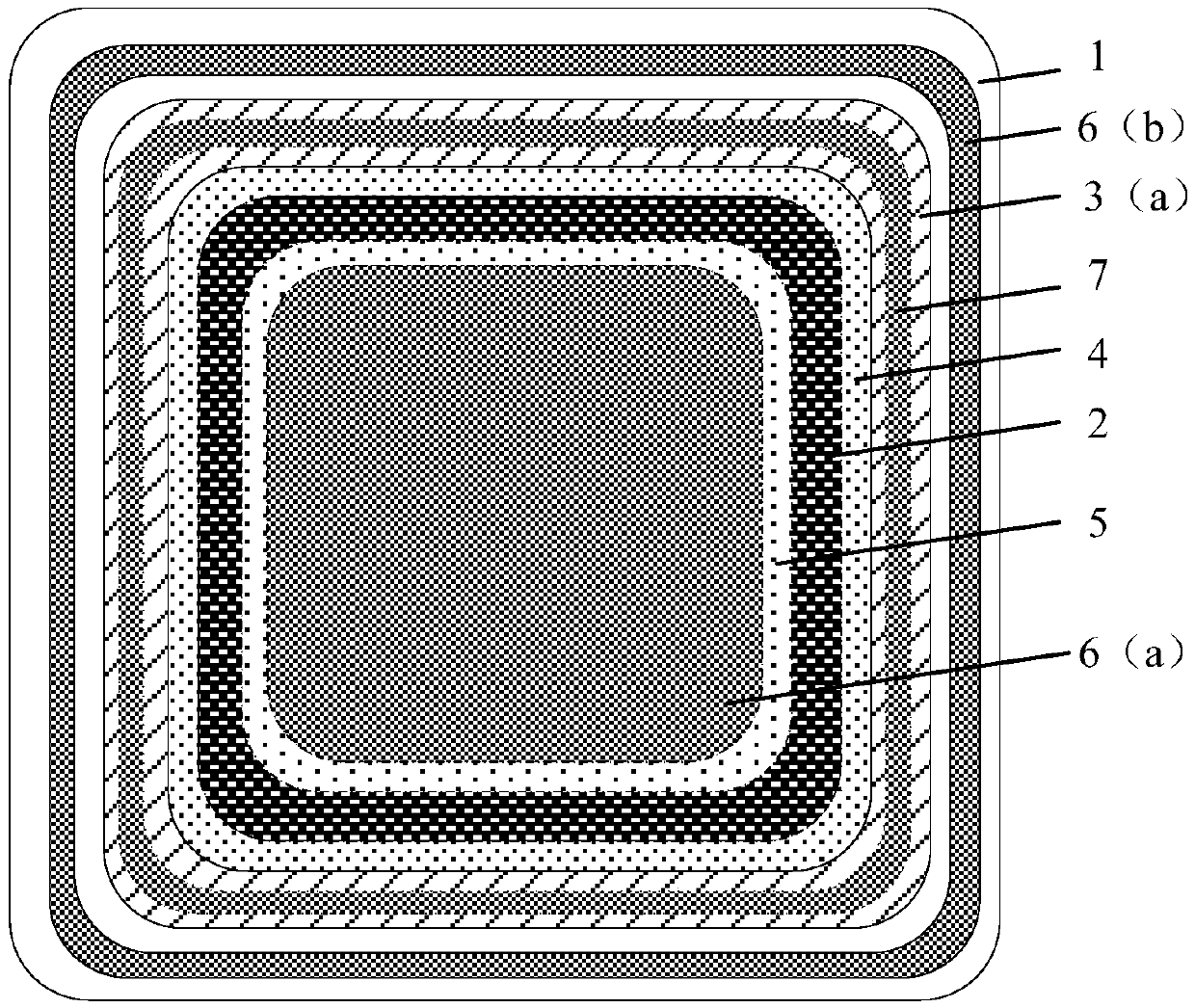

[0029] The embodiment of the present invention proposes a single photon avalanche diode detector structure with high detection efficiency, low dark count and compatible with standard CMOS technology, see figure 1 And figure 2 The floor plan, see the description below for details:

[0030] The detector is mainly composed of heavily doped P + Region, shallow P well region and N-type diffusion region together constitute P + The photosensitive PN junction formed by the P / N well, two P-type injections of different concentrations form a gradual junction, which greatly reduces the dark count of tunneling. The N buried layer 2 has the characteristics of an inverted doping distribution, and the surface doping increases with the increase in depth to form a virtual guard ring, which forms a double guard ring structure with the P well guard ring to improve the reliability and detection performance of the device.

[0031] When the device is working, due to the low doping concentration of the N-...

Embodiment 2

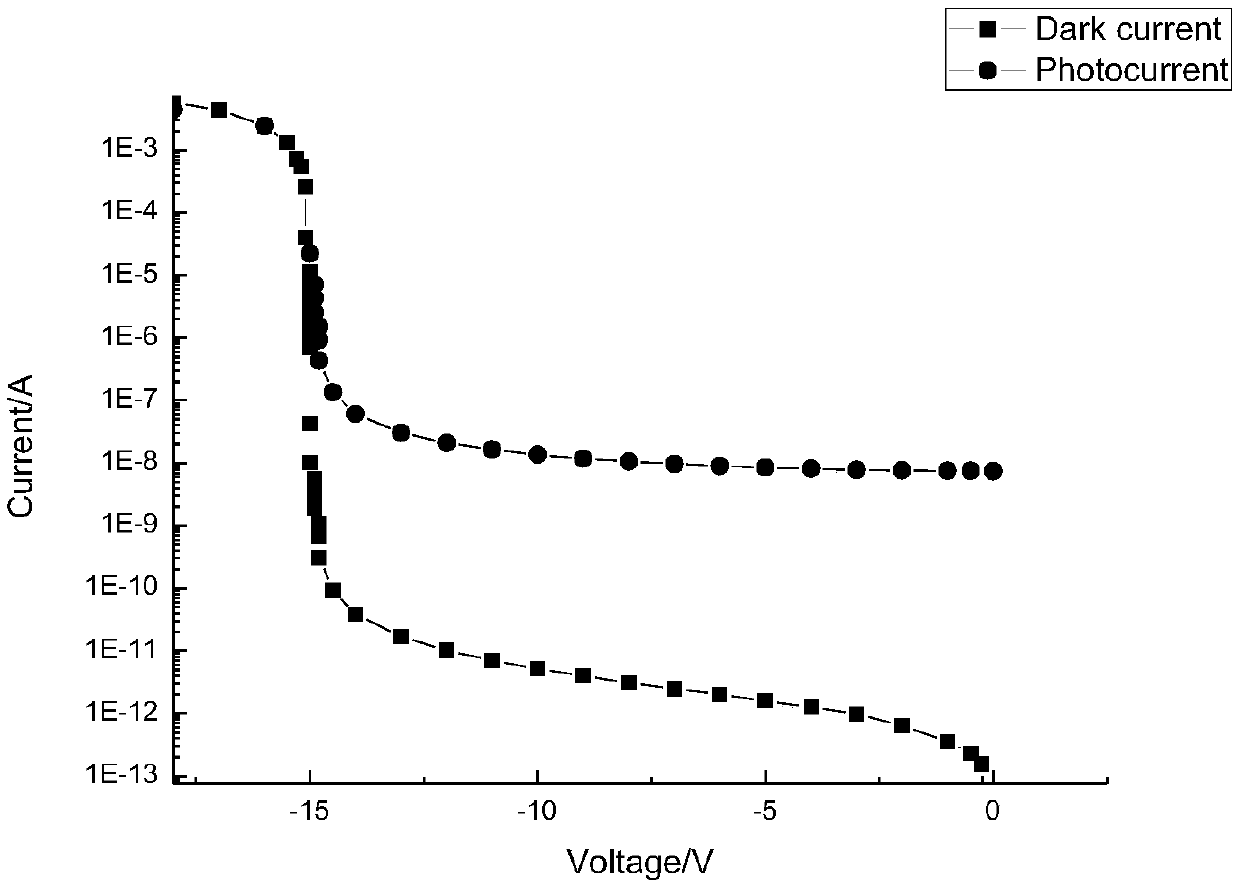

[0033] The following combines specific experimental data (attached Figure 1-5 ), the solution in embodiment 1 is further explained, see the following description for details:

[0034] figure 1 It is the structure diagram of the low dark count SPAD photodetector based on standard CMOS process according to the embodiment of the present invention, with an area of 13×13μm 2 As an example, the specific structure of the photodetector in the embodiment of the present invention is as follows:

[0035] 1) Part 1 in the figure is the P-type substrate of the detector. The material of the P-type substrate 1 is a lightly doped P-type silicon wafer. The P-type substrate 1 serves as a supporting base of the detector according to the embodiment of the present invention;

[0036] 2) Part 2 in the figure is the N buried region. Due to the unique doping characteristics of the N buried layer 2, two doping concentrations under different junction depths are used for calculation, and the concentration...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More