FinFET enhanced device of P-GaN cap layer and manufacturing method

A manufacturing method and enhanced technology, applied in the field of microelectronics, can solve problems such as low switching characteristics of devices, threshold voltage drift, increase in series resistance of source electrodes and drain electrodes, etc., achieve good process repeatability and temperature stability, and improve Effects of Threshold Voltage Stability and Gate Control Capability Enhancement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

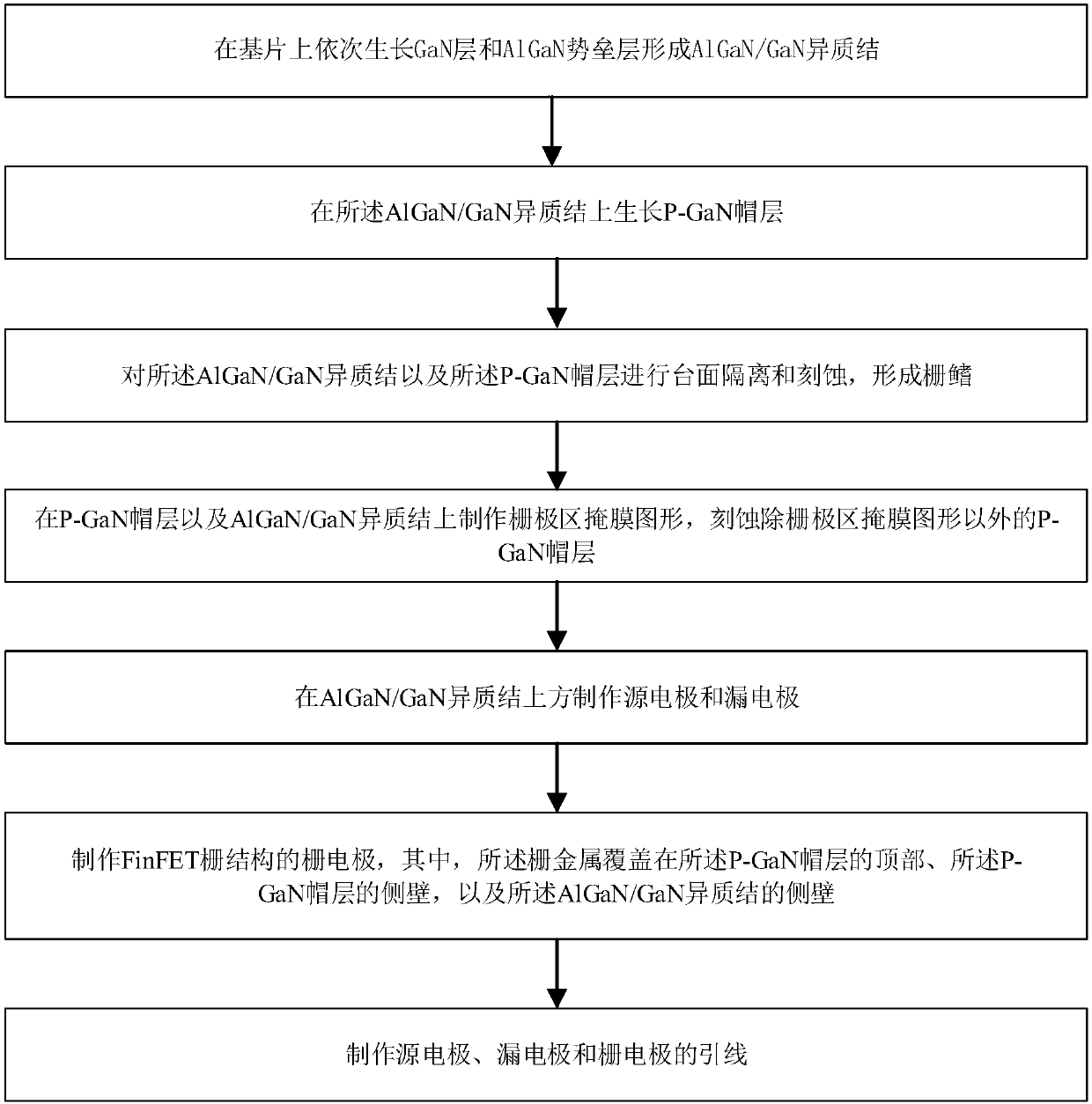

[0054] See figure 1 , figure 1 A schematic diagram of a method for manufacturing a FinFET enhanced device with a P-GaN cap layer provided by an embodiment of the present invention, including the following steps:

[0055] S1. Grow a GaN layer and an AlGaN barrier layer sequentially on the substrate to form an AlGaN / GaN heterojunction, where the substrate can be a sapphire substrate or a SiC substrate, and grow a GaN layer with a thickness of 1-2 μm on the selected substrate , and then grow an AlGaN barrier layer with a thickness of 10-20nm on the GaN layer, wherein the composition content of Al in the AlGaN barrier layer is 20%-30%; two-dimensional electrons are formed at the contact position between the GaN layer and the AlGaN barrier layer gas to obtain AlGaN / GaN heterojunction.

[0056] S2. Grow a P-GaN cap layer on the AlGaN / GaN heterojunction, grow a Mg-doped GaN cap layer with a thickness of 40-60 nm on the AlGaN barrier layer, and then heat the Mg-doped GaN cap layer an...

Embodiment 2

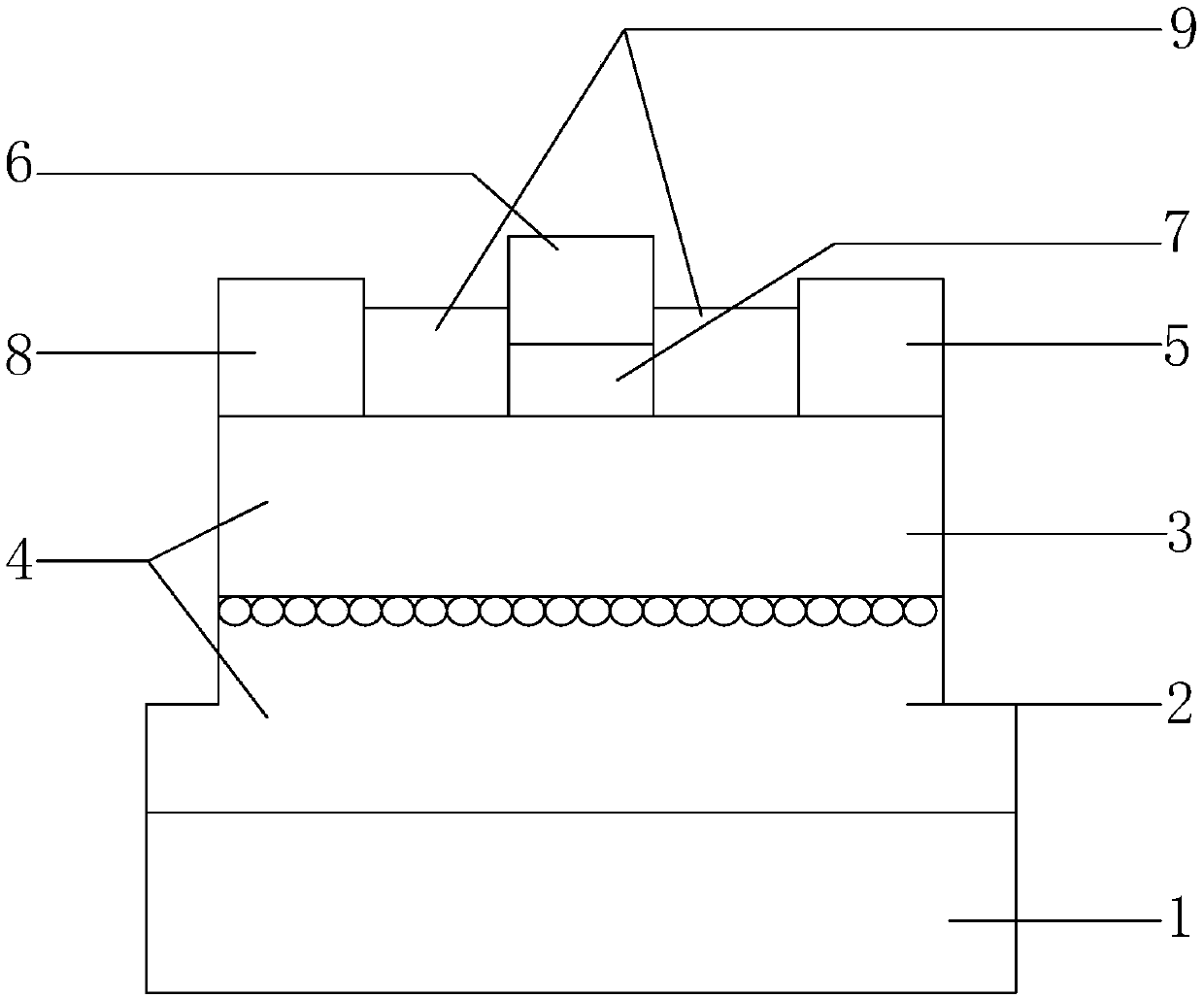

[0063] See figure 2 , figure 2 A schematic structural diagram of a FinFET enhancement device with a P-GaN cap layer provided by an embodiment of the present invention. Including: substrate 1, AlGaN / GaN heterojunction 4, SiN passivation layer 9, P-GaN cap layer 7, source electrode 8, drain electrode 5 and gate electrode 6;

[0064] The source electrode 8, the gate electrode 6, the drain electrode 5 and two pairs of SiN passivation layers 9 are located above the AlGaN / GaN heterojunction 4, wherein the first SiN passivation layer is located on the gate electrode 6 Between the source electrode 8, the second SiN passivation layer is located between the gate electrode 6 and the drain electrode 5, and the drain electrode 5 and the source electrode 8 are located at the AlGaN / GaN heterojunction 4 both sides;

[0065] The P-GaN cap layer 7 is located between the gate electrode 6 and the AlGaN barrier layer 3 , and the P-GaN cap layer 7 can effectively reduce the barrier height on o...

Embodiment 3

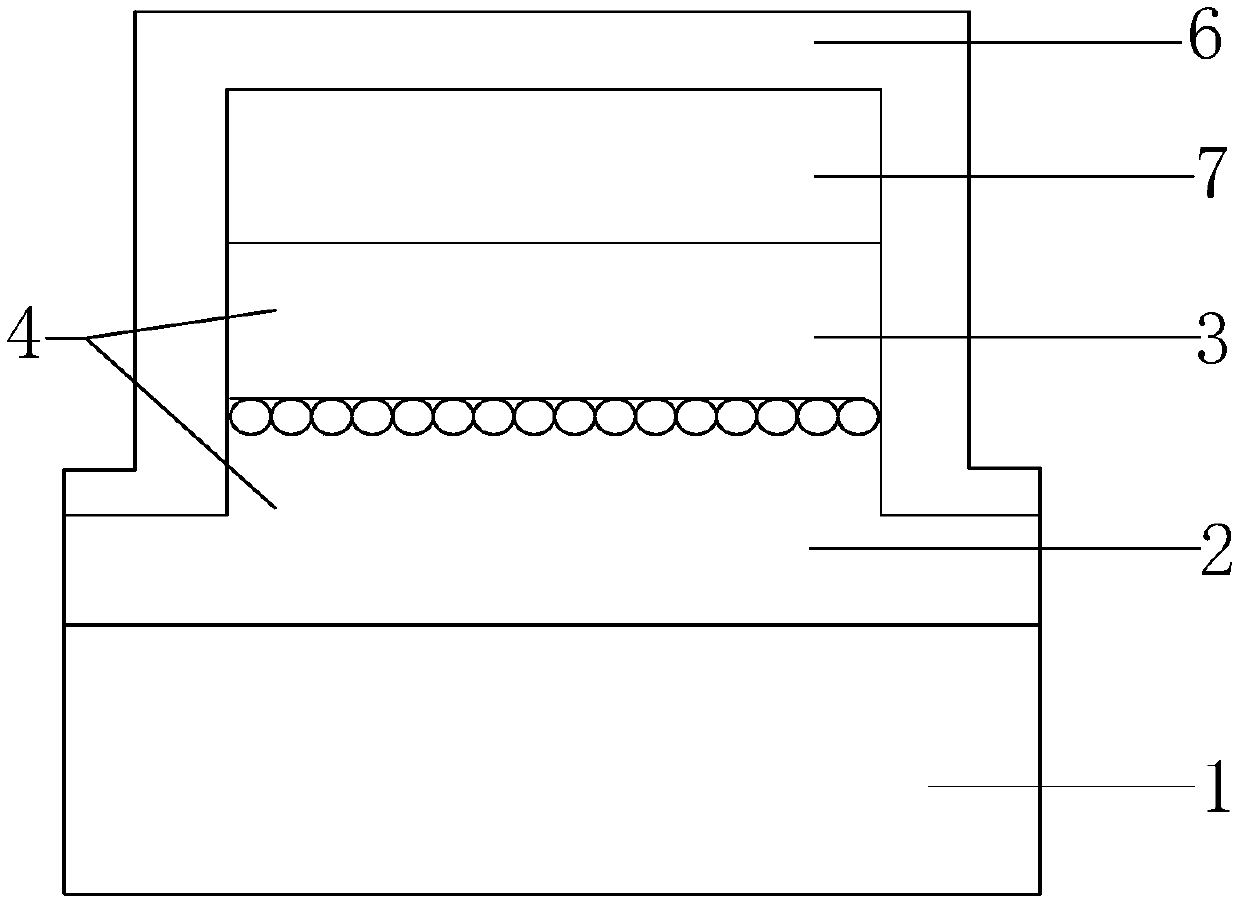

[0068] See Figure 4 , Figure 4 It is a schematic flow chart of the manufacturing process of a FinFET enhanced device with a P-GaN cap layer provided by an embodiment of the present invention. In this embodiment, on the basis of the above-mentioned embodiments, a detailed description will be focused on the manufacturing process of the device. Specifically, a FinFET enhancement device with a gate fin width of 30 nm and a P-GaN cap layer is manufactured.

[0069] Step 1. Using the MOCVD process to epitaxially grow the heterojunction:

[0070] 1.1. In this embodiment, SiC is selected as the substrate 1, and the GaN layer 2 with a thickness of 1 μm is grown on the SiC substrate substrate;

[0071] 1.2. Growing the AlGaN barrier layer 3 with a thickness of 10 nm on the GaN layer 2, wherein the Al composition is 25%, and forming two layers at the contact position between the GaN layer 2 and the AlGaN barrier layer 3 Dimensional electron gas to obtain the AlGaN / GaN heterojunctio...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More