Preparation method of medium-voltage shield gate field effect transistor

A technology of field-effect transistors and shielding gates, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of high process cost, shortened channel length, and high matching requirements, so as to reduce process cost and difficulty, prevent thick oxygen step difference, and ensure the effect of etching quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037]In order to make the objects, technical solutions, and advantages of the present invention, the technical solutions of the present invention will be further explained below.

[0038]The present invention proposes a method of preparing a medium pressure shield gate effect transistor, comprising the steps of:

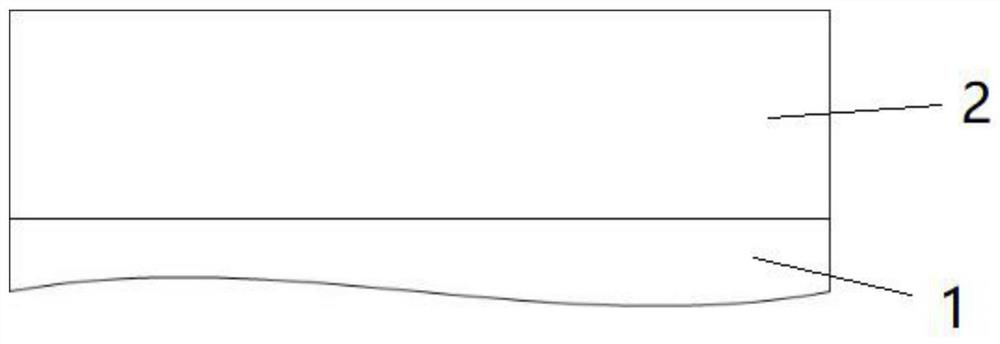

[0039]Step 1: Prepare the substrate;figure 1 As shown, the bottom layer is an N-type arsenic strain substrate 1, a resistivity range: 1mohm.cm ~ 3mohm.cm, located on the bottom surface of N-arsenic epitaxial layer 2, resistivity range: 150mohm.cm ~ 400mohm.cm , Thickness: 5 um ~ 10um.

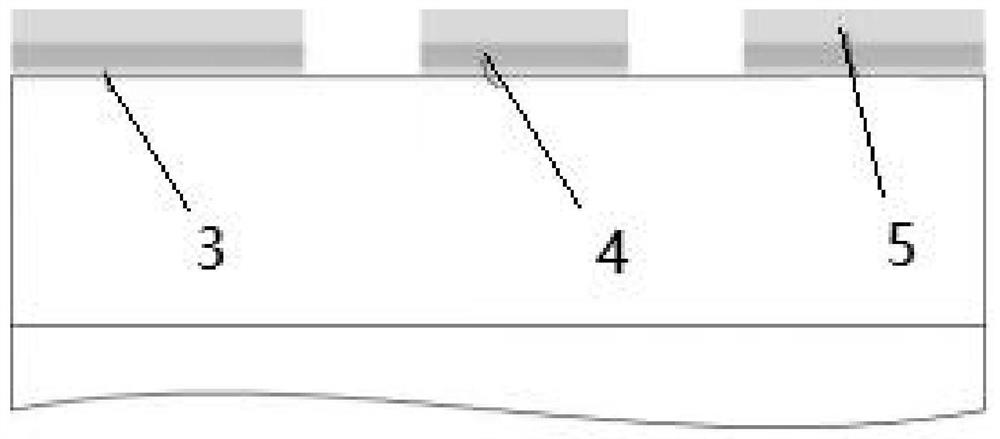

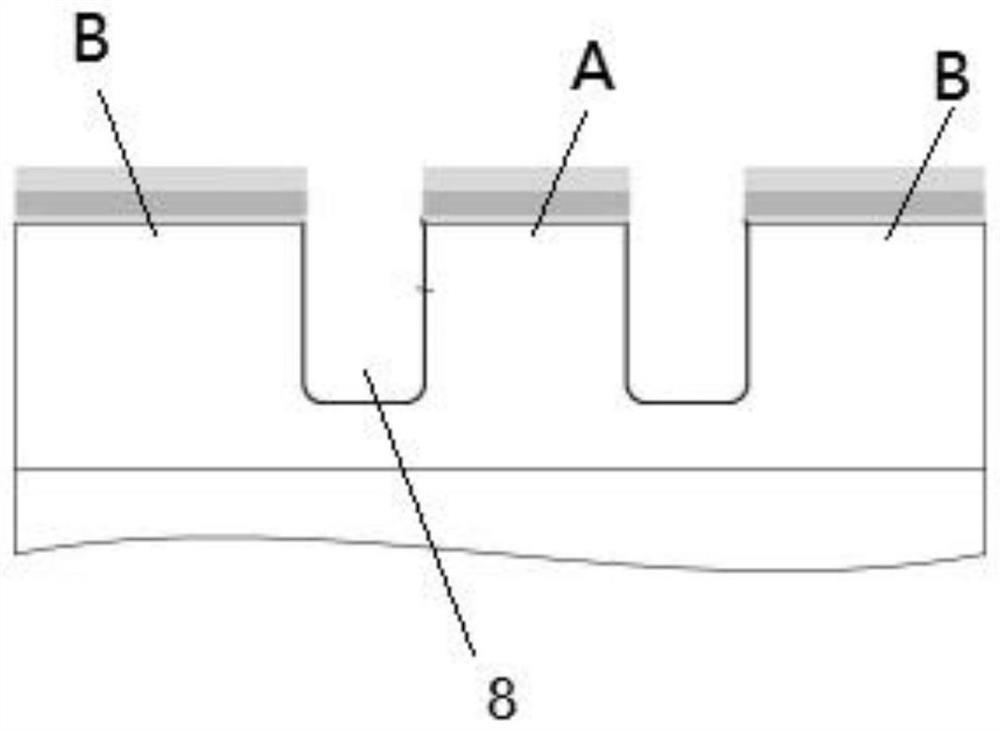

[0040]Step 2: The first layer of silica layer 3 is generated in the active region and the terminal region of the substrate surface and the terminal region, the first layer of silica layer 3 thickness is 500 angstroms ~ 1000 angstroms; preventing the trench 8 thick field oxygen 6 The thick silica is also grown in an active region during the growth process.

[0041]Step 3: A layer of silicon nitride lay...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com