Crystal pulling furnace for semiconductor monocrystalline silicon

A single crystal silicon and crystal pulling furnace technology, applied in the direction of single crystal growth, single crystal growth, crystal growth, etc., can solve the problems of scrap, defects, melt temperature, impurity concentration and other problems, and achieve consistency improvement , the effect of low defect density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

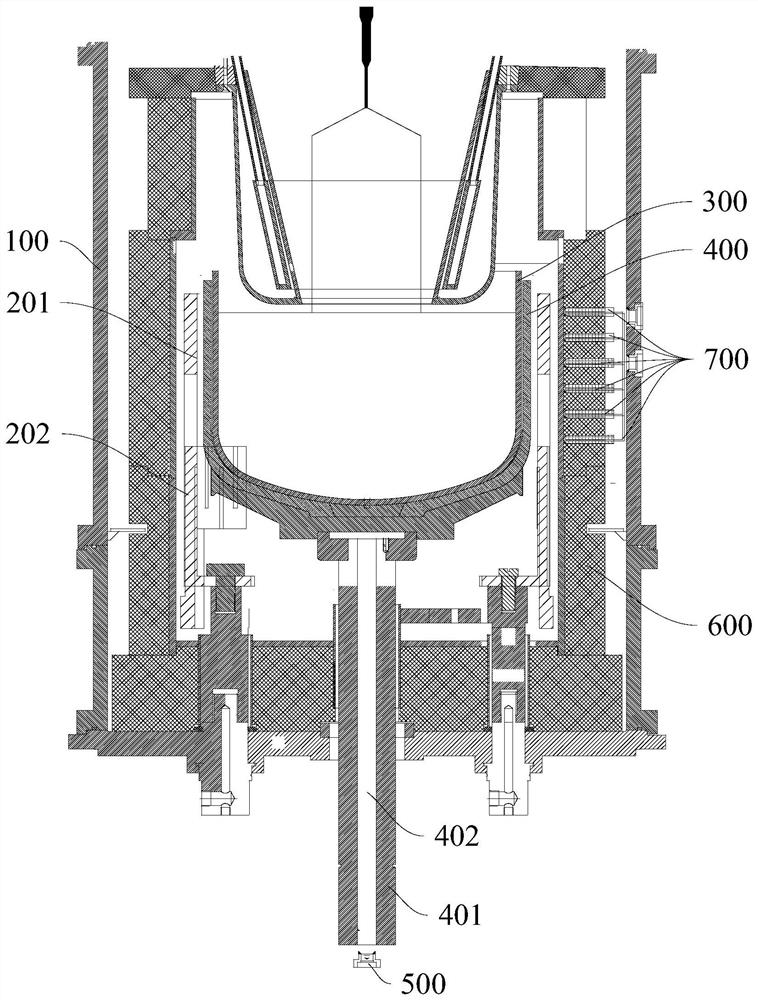

[0025] see figure 1 The crystal pulling furnace for semiconductor monocrystalline silicon in this embodiment includes a furnace body 100, a crucible and a heater 200 disposed in the furnace body 100, a gradient temperature measuring device is arranged in the furnace body, and a temperature tester is arranged at the bottom of the furnace body.

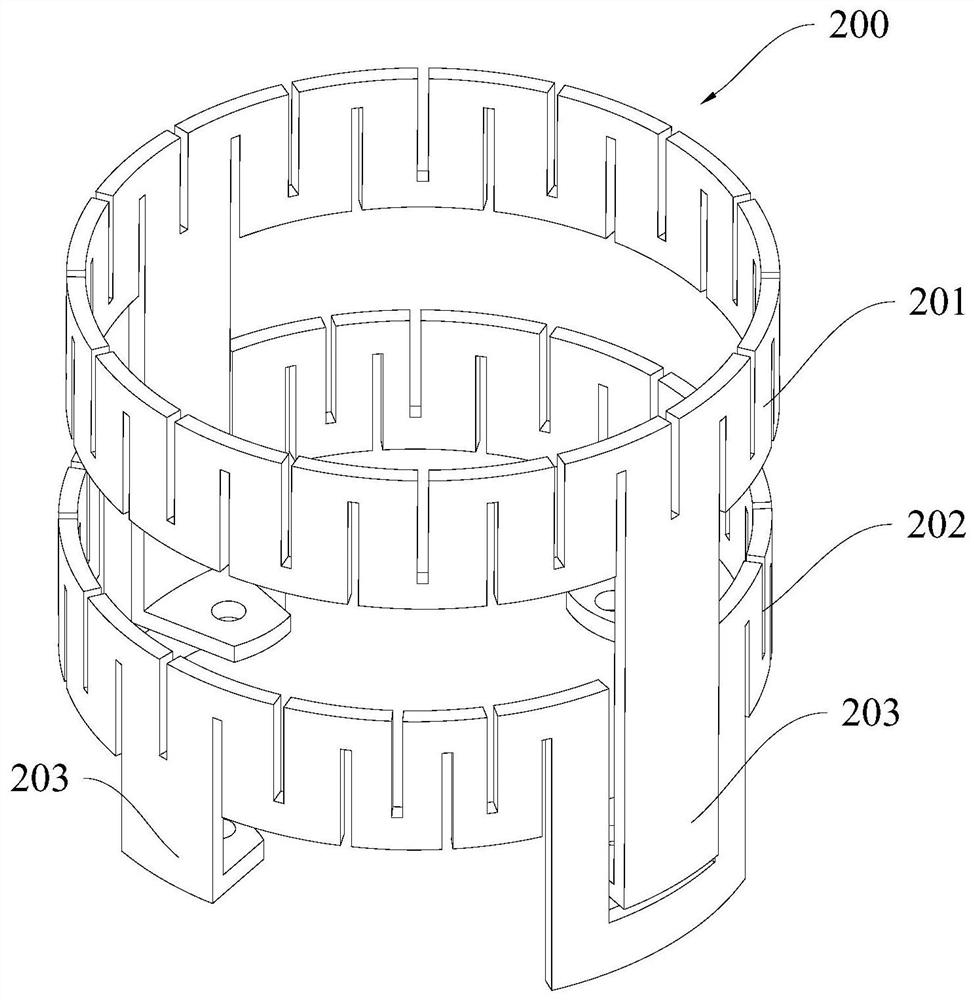

[0026] In this embodiment, the heater is arranged on the periphery of the crucible, including an upper heater 201 and a lower heater 202 arranged up and down at a certain distance. The height of the heating area of the conventional thermal field heater covers the height of the entire melt in the quartz crucible. The height of the heating area of the short thermal field heater is much smaller than the height of the melt in the crucible so as to achieve the effect of reducing oxygen. In this embodiment, two independently controlled upper heaters 201 and lower heaters 202 are arranged on the outside of the crucible. The upper and lower...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com