Diode chip structure and preparation method thereof

A chip structure and diode technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as large overshoot voltage, poor diode softness, and damage to system circuit components, to improve withstand voltage capability, reduce Reverse leakage current, the effect of slowing down the reverse pumping speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

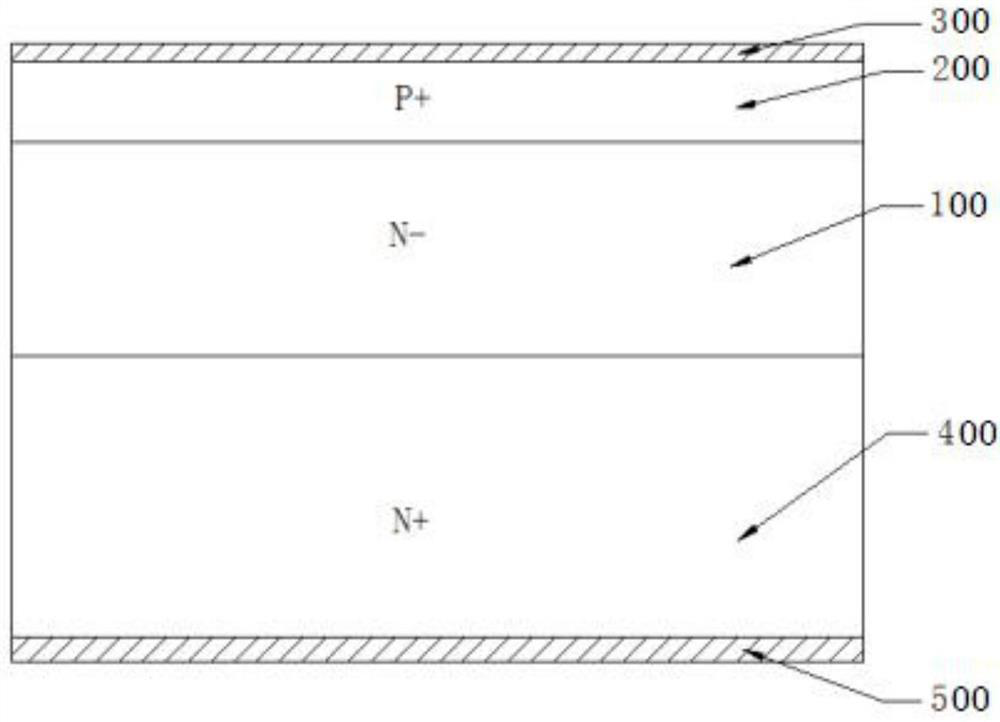

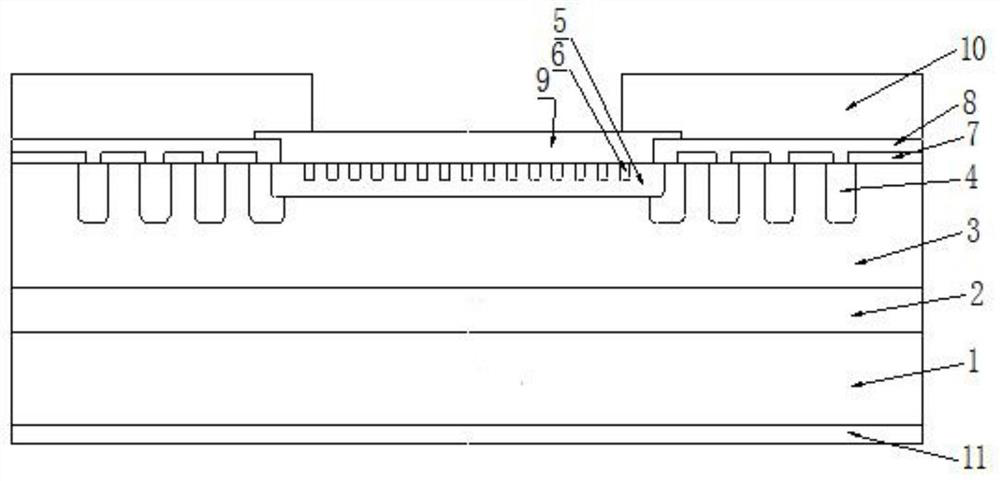

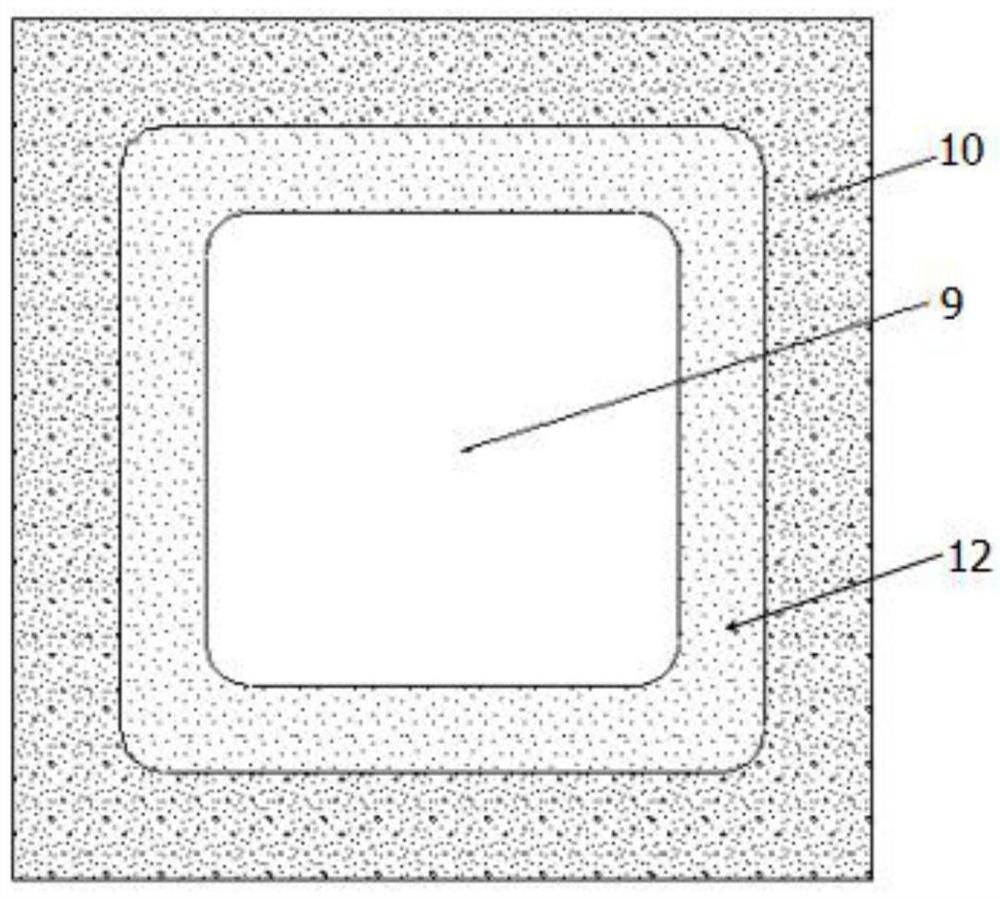

[0049] An embodiment of the present invention provides a diode chip structure, such as figure 2 As shown, a double-base structure is adopted, including an N+ substrate 1 and an N buffer layer 2 and an N- epitaxial region 3 that are sequentially grown on top of it; 4. The central area in the top of the N- epitaxial region 3 is the P base region 5, the P base region 5 is periodically inlaid with the active P+ region 6, the metallized anode 9 is made on the top of the P base region 5, and the oxidation is made on the top of the P+ring region 4 The top of silicon 7 and silicon oxide 7 passivates borophosphosilicate glass 8 , and borophosphosilicate glass 8 is covered by silicon nitride 10 , and the back of N+ substrate 1 is a metallized cathode 11 .

[0050] Among them, the metallized anode is an aluminum electrode with a thickness of 3-4um, and the metallized cathode is a titanium, nickel or silver electrode with a thickness of 0.1±0.01um / 0.6±0.1um / 0.8±0.1um respectively.

[00...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

| electrical resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More