FeFET based on anti-ferroelectric gate dielectric and oxide semiconductor channel and preparation method thereof

An oxide semiconductor and antiferroelectric technology, applied in the field of micro-nano electronics, can solve the problems of large operating voltage, breakdown, and insufficient, and achieve the goal of reducing operating voltage, improving durability, reducing charge injection and defect generation Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

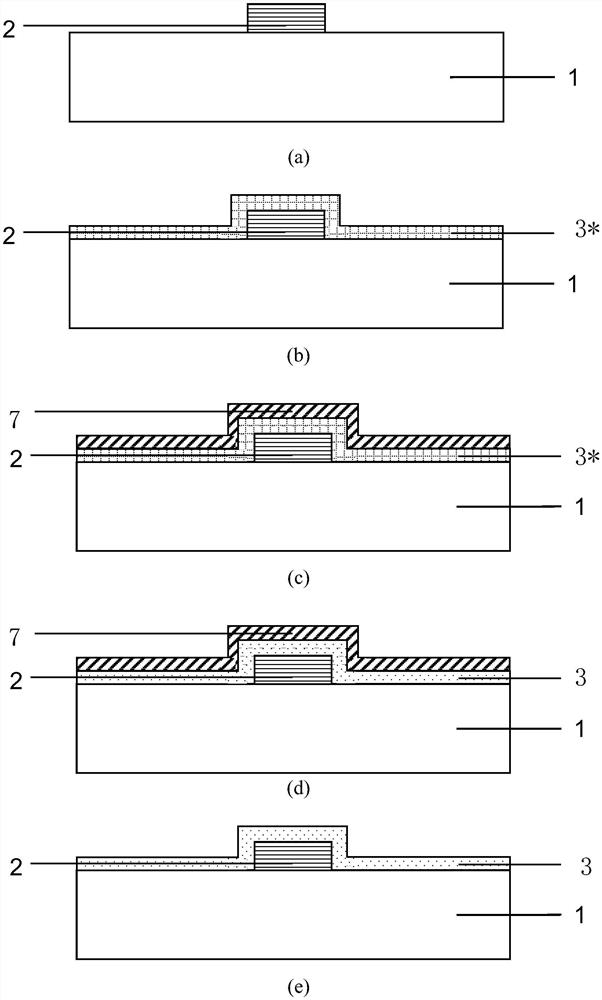

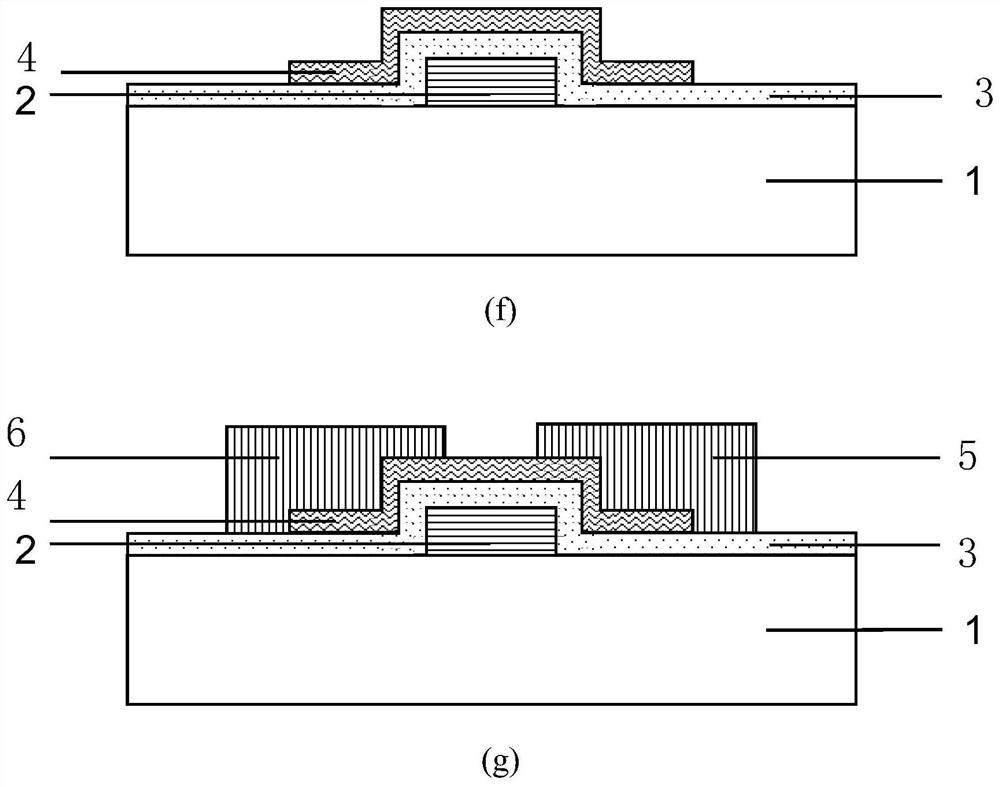

[0044] The present invention will be further described through the embodiments below in conjunction with the accompanying drawings.

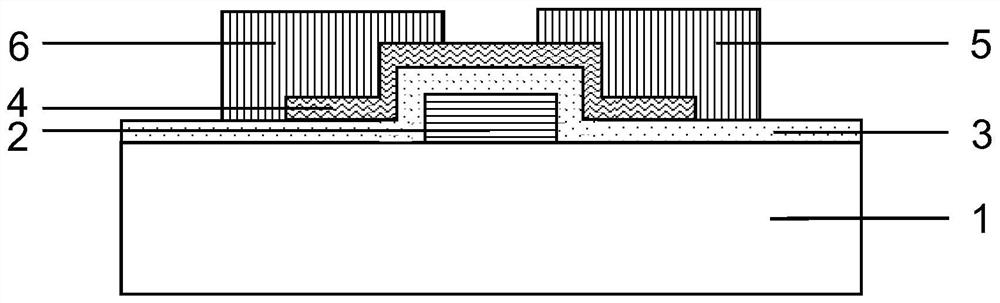

[0045] Such as figure 1 As shown, the high-durability FeFET based on the antiferroelectric gate dielectric and the oxide semiconductor channel of the present invention includes an insulating substrate 1, a back gate electrode layer 2, an activated antiferroelectric gate dielectric material layer 3, and an oxide semiconductor channel 4. The source electrode 5 and the drain electrode 6 . Wherein, the patterned gate electrode layer 2 is located on the insulating substrate 1, the activated antiferroelectric gate dielectric material layer 3 is located on the insulating substrate 1 and the gate electrode layer 2, and the patterned oxide semiconductor channel 4 is located on the activated Above the final antiferroelectric gate dielectric material layer 3 , the source contact electrode 5 and the drain contact electrode 6 are respectively located on the...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More