Chip manufacturing method, chip connecting method and chip

A production method and connection method technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device parts, semiconductor devices, etc., can solve problems such as solder diffusion and chip failure, and achieve stable performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

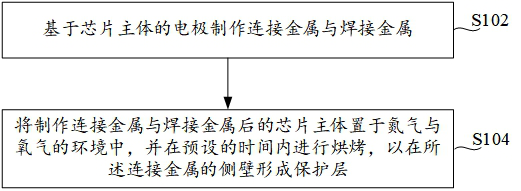

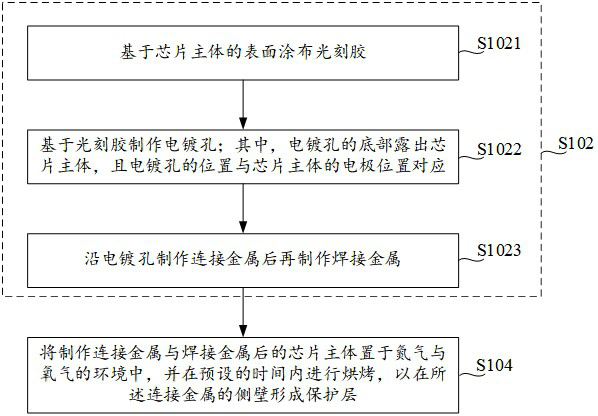

Method used

Image

Examples

Embodiment Construction

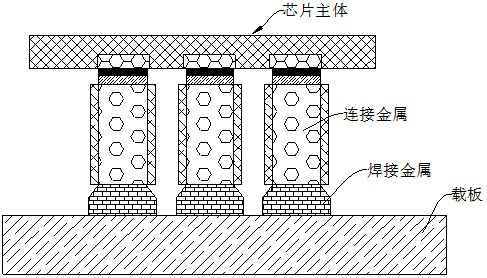

[0045] After making the chip theme, a layer of photoresist can be coated on the surface of the chip body, and the structure after coating the photoresist is as follows Figure 4 shown. Figure 4 In , the chip body includes electrodes, and the chip body also includes a metal layer, wherein the metal layer may be multi-layered, such as Figure 4 Among them, the metal layer can be two layers, and the metal layer can be used to realize different functions, for example, to realize Schottky contact, etc., which is not limited here. In the manufacturing process of the present application, the metal layer is actually deposited first, then photoresist is coated on the surface of the metal layer, and the photoresist is grooved to form plating holes.

[0046] It should also be noted that in the chip manufacturing process, multiple chips are actually manufactured at the same time, such as Figure 4 , shows the production of two chips, one chip is on the left side of the dotted line A, a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More