Self-aligning silicide method for RF lateral diffusion field-effect transistor

A field-effect transistor and self-aligned silicide technology, which is used in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem of large series resistance in source and drain regions, lack of design flexibility, and difficult self-aligned silicide in LDMOS. And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

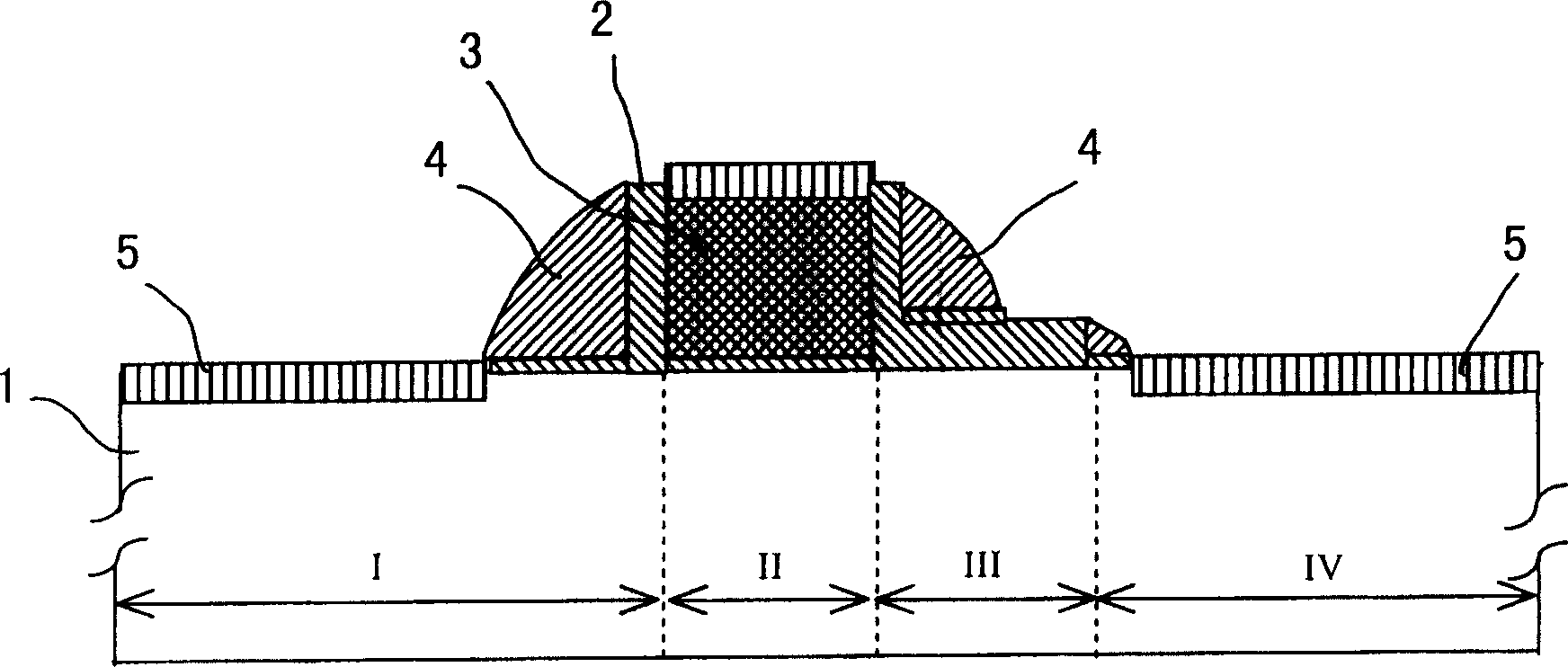

Image

Examples

Embodiment Construction

[0029] A self-aligned silicide method for radio frequency lateral diffusion field effect transistors of the present invention comprises the following steps:

[0030] Step 1: On the silicon wafer, perform maskless drift region implantation after polycrystalline gate etching;

[0031] Step 2: Deposit a thin layer of silicon dioxide by thermal decomposition of ethyl orthosilicate; this step 2 uses the thermal decomposition of ethyl orthosilicate to deposit silicon dioxide, and its thickness is 40-80nm;

[0032] Step 3: Protect the drift region with photoresist, etch silicon dioxide back, and form a silicon dioxide sidewall near the source side of the gate; this step 3 uses a photolithography plate to protect the drift region, and etches the silicon dioxide sidewall conditions For: power 400W, pore 1.2cm, argon 300sccm, carbon tetrafluoride 15sccm, trifluoromethane 35sccm, overcut 30%, endpoint trigger control;

[0033] Step 4: Source-drain self-alignment injection and deglue; in...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More