Process for fabricating semiconductor device

a technology of semiconductor devices and fabrication processes, applied in semiconductor devices, electrical devices, transistors, etc., can solve the problems of thermal influence on the substrate, low productivity, and inferior physical properties of crystalline silicon semiconductors, so as to prevent heat damage on the substrate, improve crystal character, and improve the effect of crystal character

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

example 1

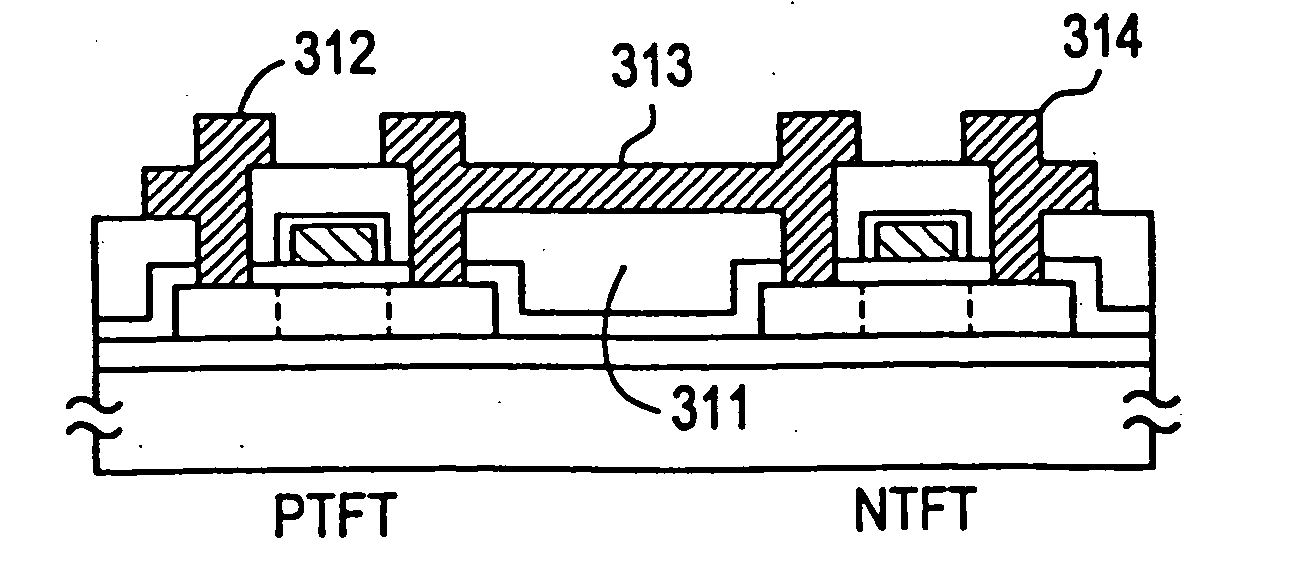

[0033] Referring to FIGS. 1(A) to 1(D), the present example relates to a process for fabricating a circuit comprising a p-channel TFT (hereinafter referred to simply as a “PTFT”) and an n-channel TFT (hereinafter referred to simply as an “NTFT”) formed in a complementary arrangement using a crystalline silicon film formed on a glass substrate. The structure obtained in the present example is applicable to switching elements of pixel electrodes and to peripheral driver circuits of active liquid crystal display devices, as well as to image sensors and three-dimensional integrated circuits.

[0034] Referring to the cross section views in FIGS. 1(A) to 1(D), the fabrication process of the present example is described below. A 2,000 Å thick silicon oxide film was deposited as a base film 102 on the surface of a Coming 7059 glass substrate 101 by a sputtering process. Mask alignment in the later steps can be facilitated by annealing the substrate either before or after depositing the base ...

example 2

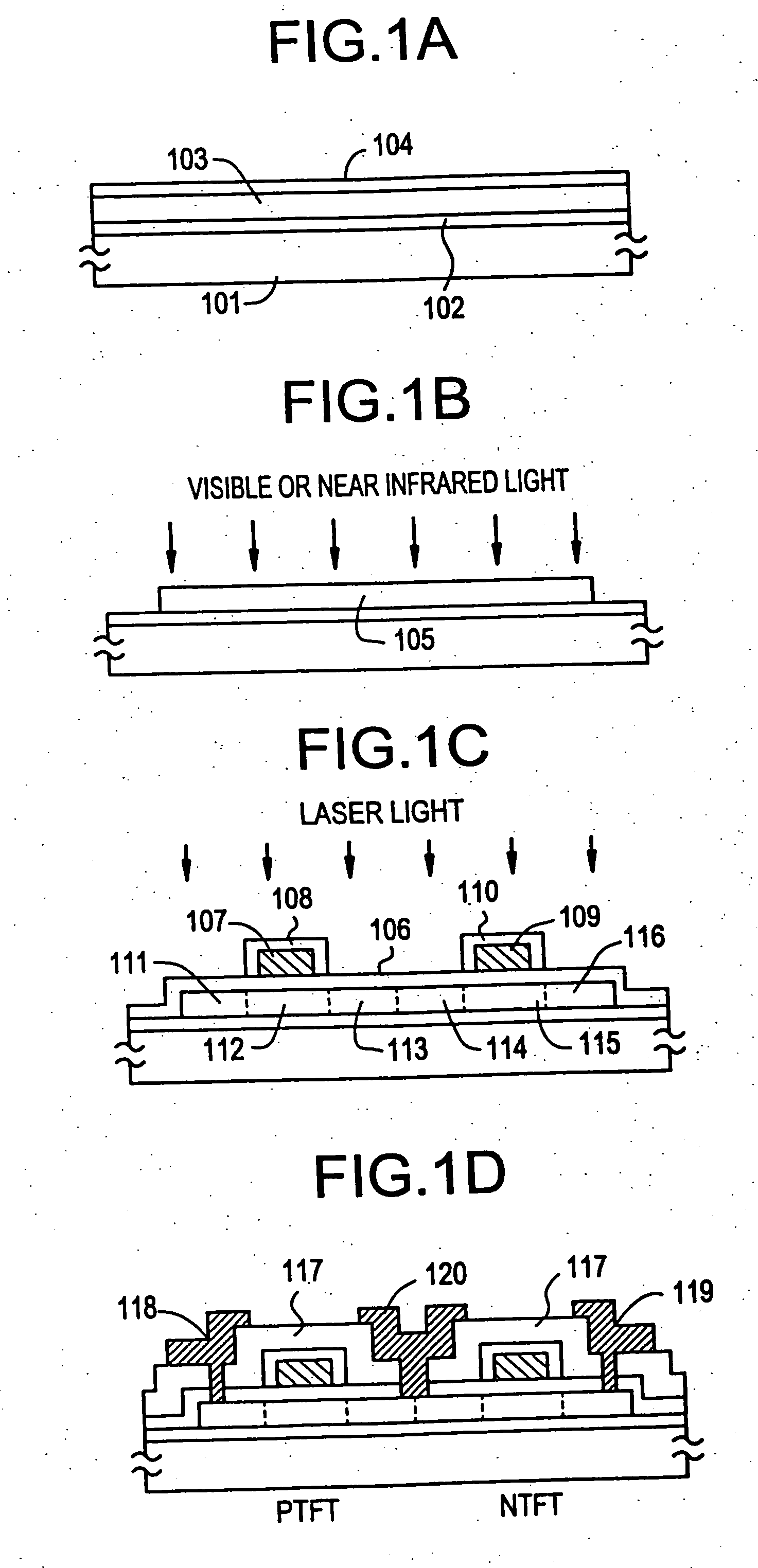

[0053] The present example relates to an active-matrix type liquid crystal display device having N-channel TFTs (NTFTs) each attached as a switching element to each of the pixels. The following description refers to a single pixel only, however, a practical active-matrix type liquid crystal device comprises a great number (generally several hundred thousands) of pixels all having the same structure simultaneously. Furthermore, the TFT not necessarily be an NTFT, and a PTFT can be employed as well. The TFT need not be provided to the pixel portion of the liquid crystal display, and it can be used in the peripheral circuits. Moreover, it can be used in image sensors and in other devices. In short, the application is not limited as long as it is used as a thin film transistor.

[0054] Referring to the step sequential structures shown in FIGS. 2(A) to 2(D), the process for fabricating the structure according to an embodiment of the present invention is described below. A 2,000 Å thick fi...

example 3

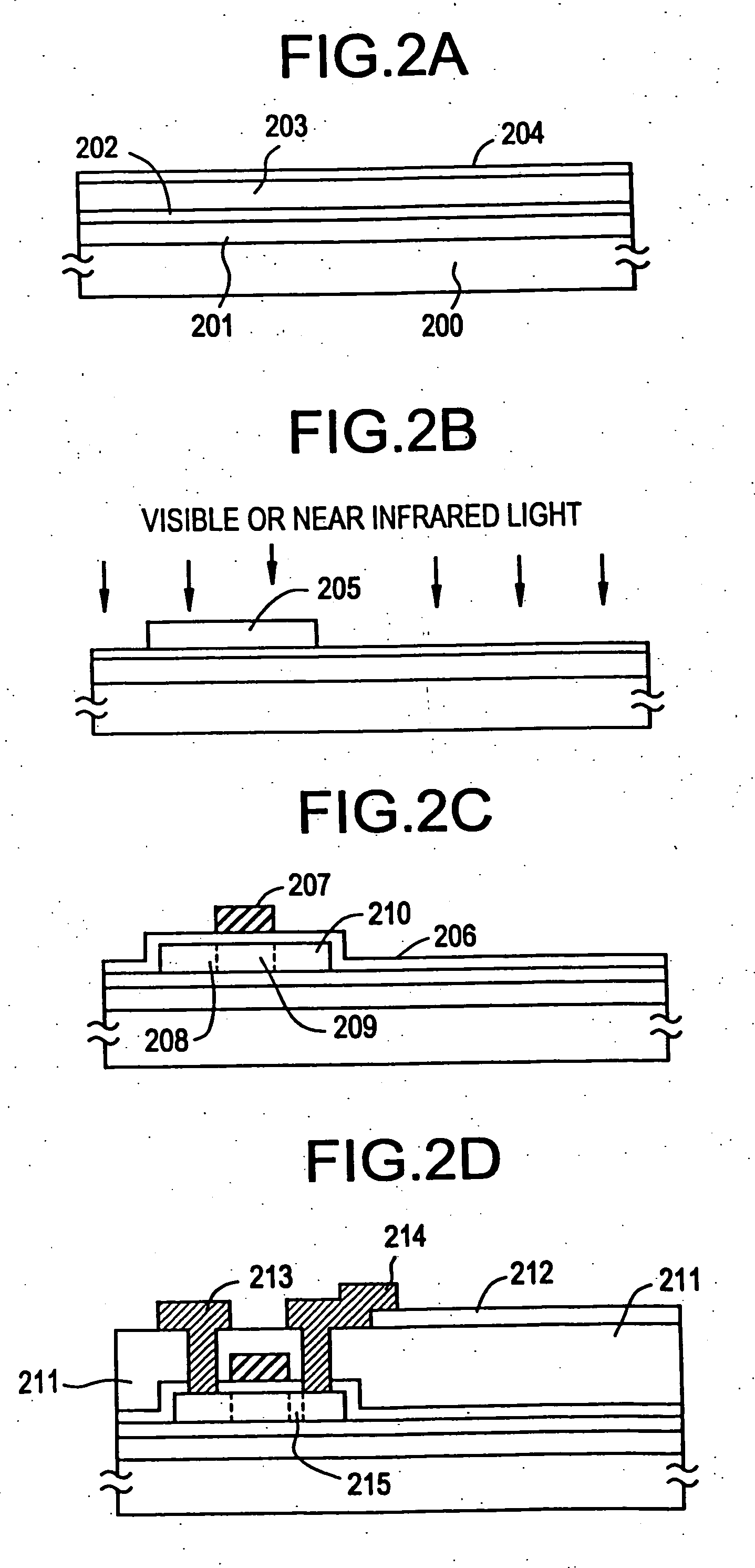

[0061] Referring to FIGS. 3(A) to 3(E), a process for fabricating a TFT circuit according to an embodiment of the present invention is described below. A substrate of a glass having a strain point in the range of from 550 to 650° C., such as an AN2 glass substrate having a strain point of 616° C., was used. To prevent shrinking from occurring, the substrate was subjected previously to pre-annealing at 670° C. for a duration of 4 hours and to cooling to 450° C. at a rate of 0.1° C. / min in a manner similar to that in Example 1. A base film 302 was formed on the substrate 301, and an amorphous silicon film 303 having thickness from 300 to 800 Å and a 200 Å thick silicon oxide film 304 were deposited thereafter by plasma CVD. The resulting structure was heated for annealing at 620° C. for a duration of 30 minutes. After the thermal annealing, the substrate was rapidly cooled to 450° C. at a rate of from 2 to 200° C. / sec, preferably, at a rate of 10° C. / sec or higher. This treatment prev...

PUM

| Property | Measurement | Unit |

|---|---|---|

| with wavelength | aaaaa | aaaaa |

| temperature | aaaaa | aaaaa |

| surface temperature | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More