Process to minimize and/or eliminate conductive material coating over the top surface of a patterned substrate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

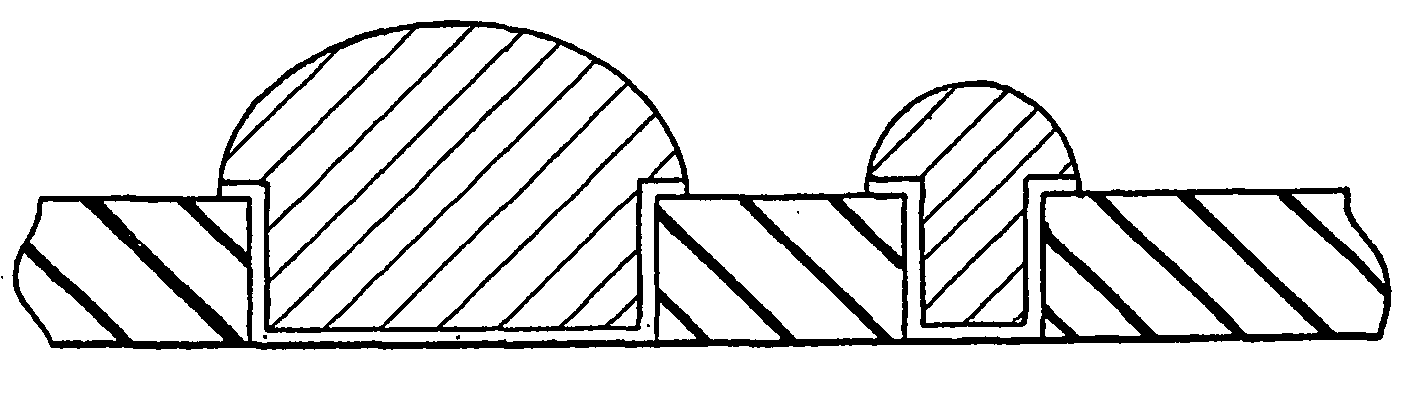

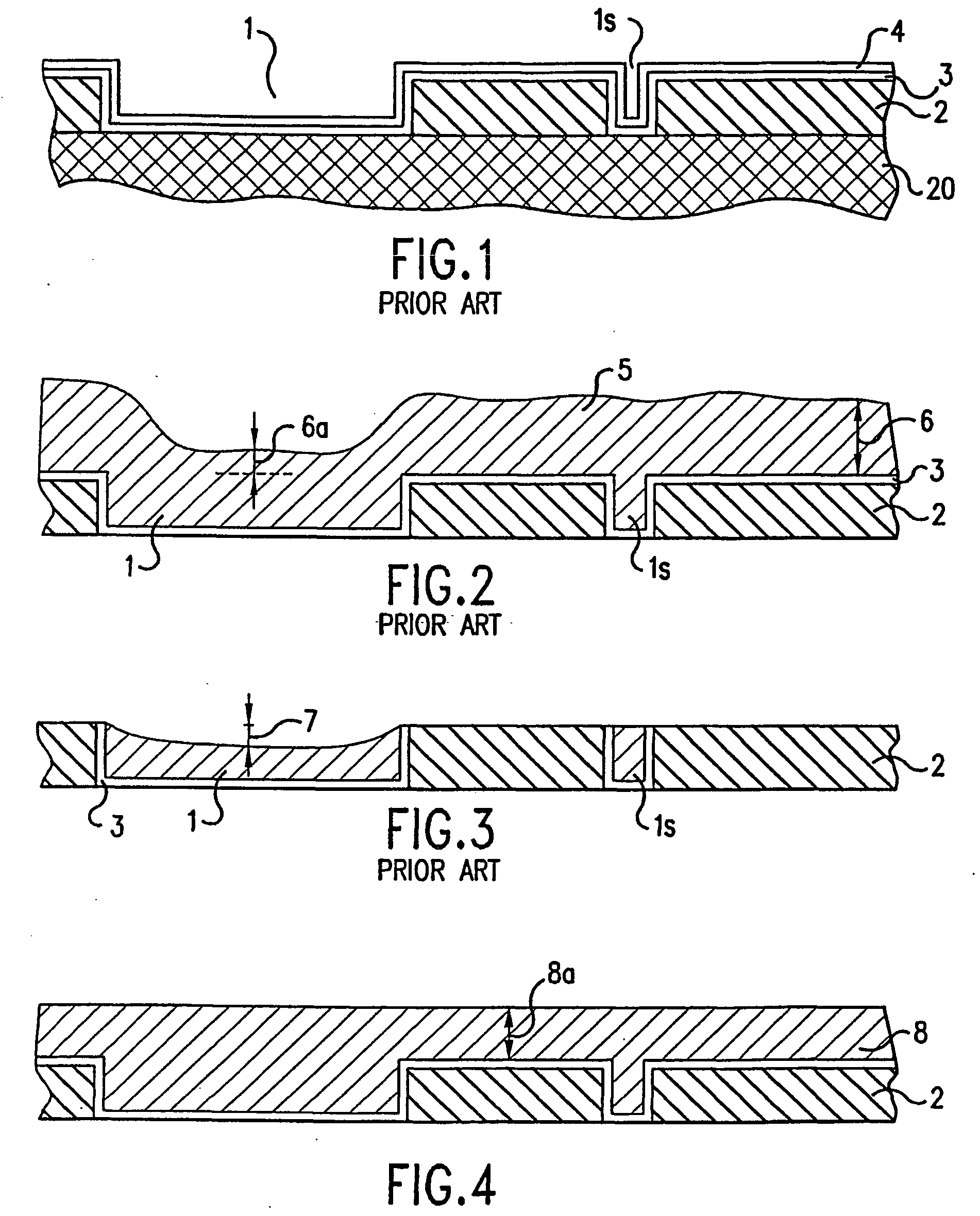

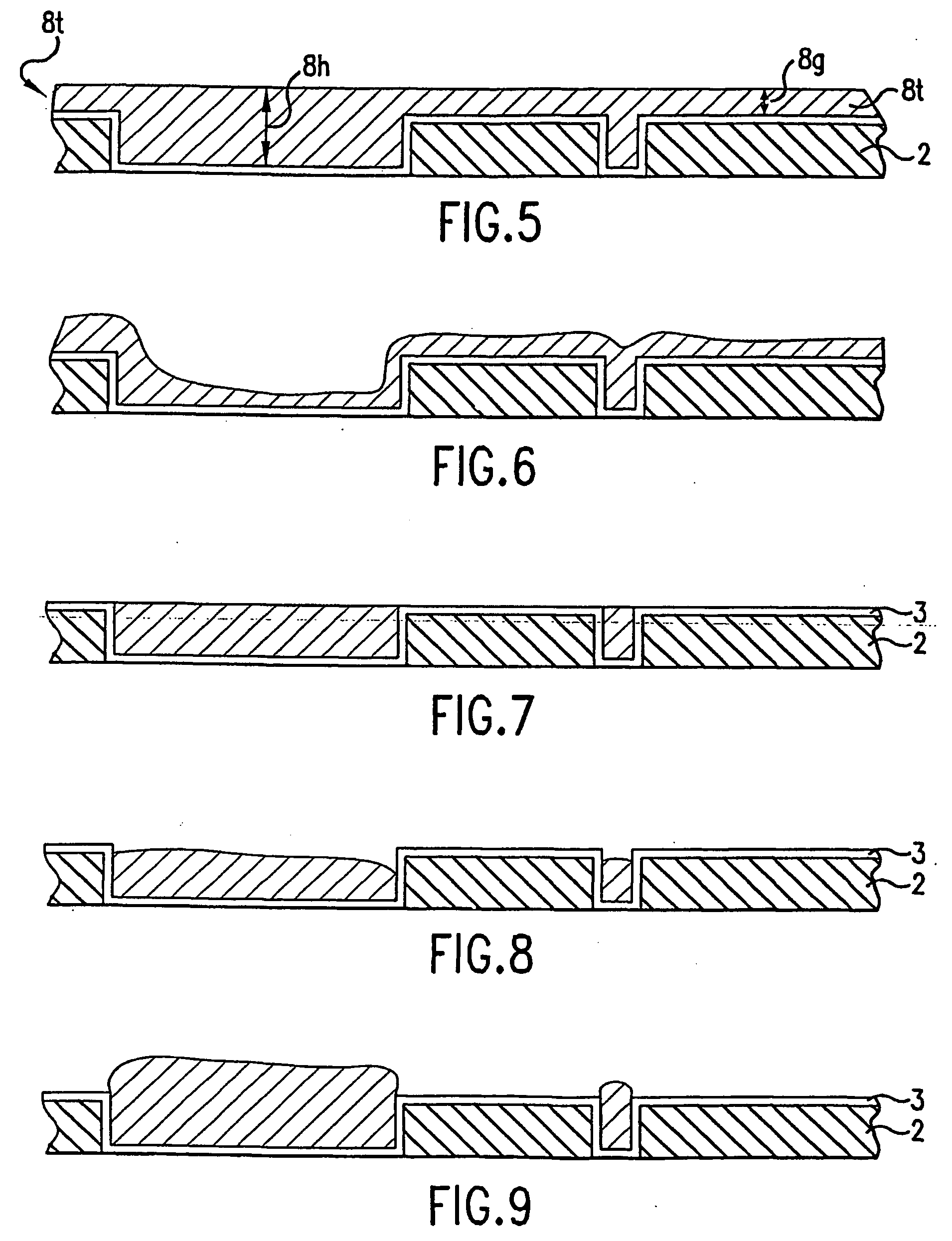

Image

Examples

example 1

Standard Electrolyte Solution

[0041] A Cu-sulfate based Cu plating solution was prepared as follows:

[0042] 70 grams per liter of CuSO4+5H2O, 150 grams per liter of concentrated H2SO4, and 70 ppm per liter of Cl− ions were mixed in enough water to make 10 liters of solution. Twenty-five ml of Ultrafill S2001®, 1.0 ml of Ultrafill A2001® from Shipley were then added to obtain a standard good quality plating electrolyte.

[0043] This solution was used for Cu plating on a 200 mm diameter wafer surface. The wafer surface contained sub-micron size features as well as features in the 10-100 micron range. The pad was a fixed abrasive pad supplied by 3M® company. The diameter of the pad was 180 mm and the anode assembly was oscillated in the horizontal direction so that plating could be achieved on all areas on the larger wafer surface. During plating, the distance between the pad and the wafer surface was kept at around 0.1 cm. The plating current was 2 amperes and the plating solution flow...

example 2

Polishing and Planarization Using Standard Electrolyte Solution

[0044] The plating experiment of Example 1 was repeated, except this time, after an initial period of 30 seconds, the pad was pushed against the wafer surface at a pressure of 1 psi for plating as well as polishing and planarization. The resulting Cu deposit had a rough surface with deep scratches apparently caused by the abrasive pad. There were also Cu particles smeared all over the surface of the wafer. Very little amount of material removal was achieved because material removed from one region of the surface by the action of the abrasive pad was probably deposited back onto the surface at another region in the form of smeared particles, which were welded or bonded to the substrate surface. The substrate defect level was extremely high and feature filling was poor.

example 3

Modified Electrolyte Solution

[0045] Five ml per liter of butyl-nitrite were added as a modifying agent to the electrolyte of Example 1 and the plating and polishing experiment of Example 2 was repeated using this modified plating solution. The resulting Cu deposit was highly planar and was similar to the structure shown in FIG. 4. Copper layer resistivity was still below 2×10−6 ohm-cm, demonstrating the ability of the modified electrolyte to yield high quality Cu deposits. The copper film was planar with uniform overburden over the sub-micron size features as well as the large features.

[0046] An anode assembly is disclosed in co-pending U.S. patent application Ser. No. 09 / 568,584, filed May 11, 2000, titled ANODE ASSEMBLY FOR PLATING AND PLANARIZING A CONDUCTIVE LAYER. A substrate holder / head assembly design is provided by co-pending U.S. patent application Ser. No. 09 / 472,523, filed Dec. 27, 1999, titled WORK PIECE CARRIER HEAD FOR PLATING AND POLISHING. The disclosures of these ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More