I-shaped gate electrode for improved sub-threshold mosfet performance

a technology of mos transistor and gate electrode, which is applied in the field of integrated circuits, can solve the problems of high flicker noise, low efficiency, and low efficiency of mos transistor, and achieve the effect of improving the performance of sub-threshold mos transistors and reducing the risk of mos transistor flicker nois

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026]This invention will be described in connection with its embodiments, namely as implemented into an integrated circuit including metal-oxide-semiconductor (MOS) transistors, as it is contemplated that the invention will be especially beneficial in such an implementation. However, it is contemplated that this invention can provide significant benefit when applied to many other integrated circuit structures and methods. Accordingly, it is to be understood that the following description is provided by way of example only, and is not intended to limit the true scope of this invention as claimed.

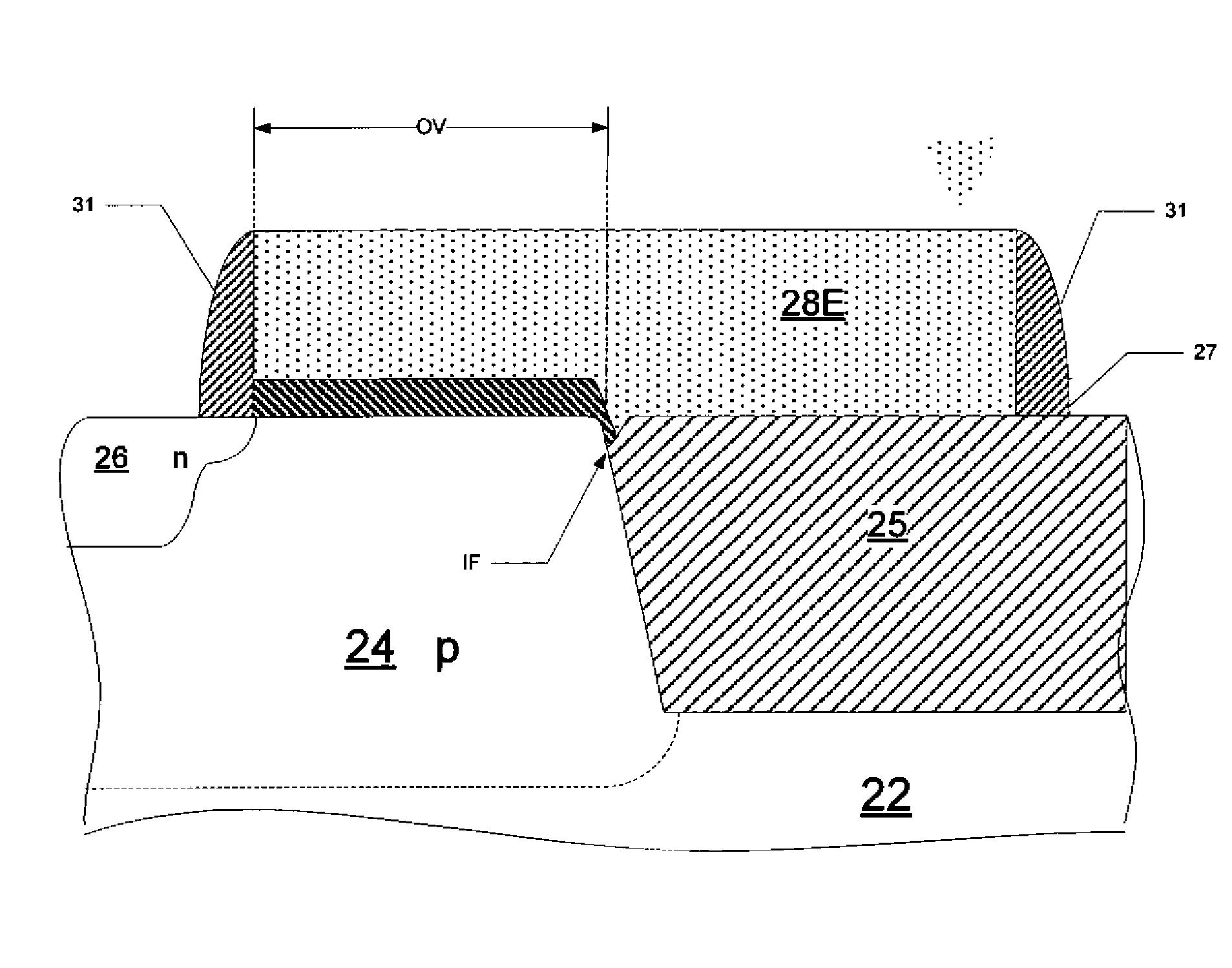

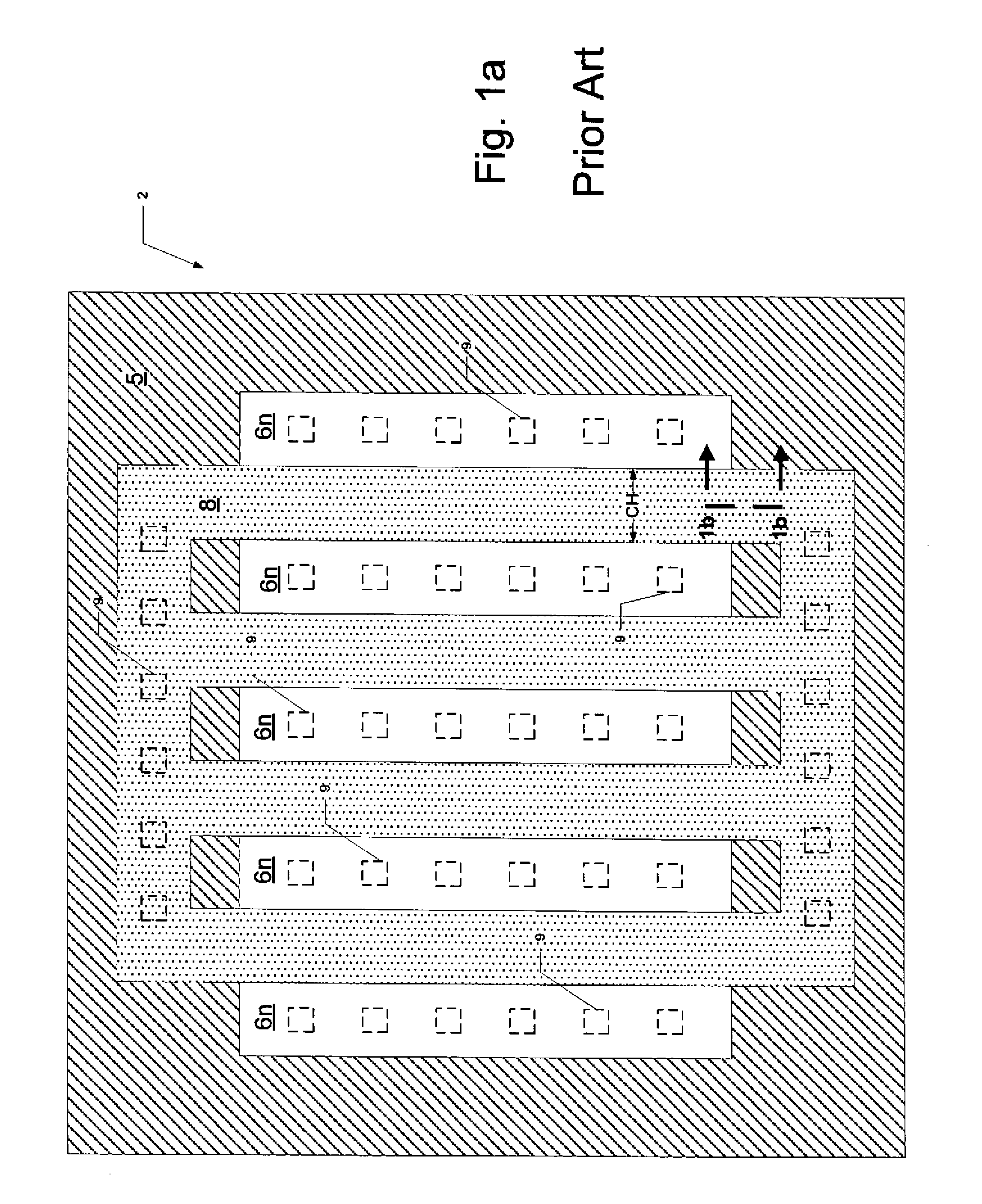

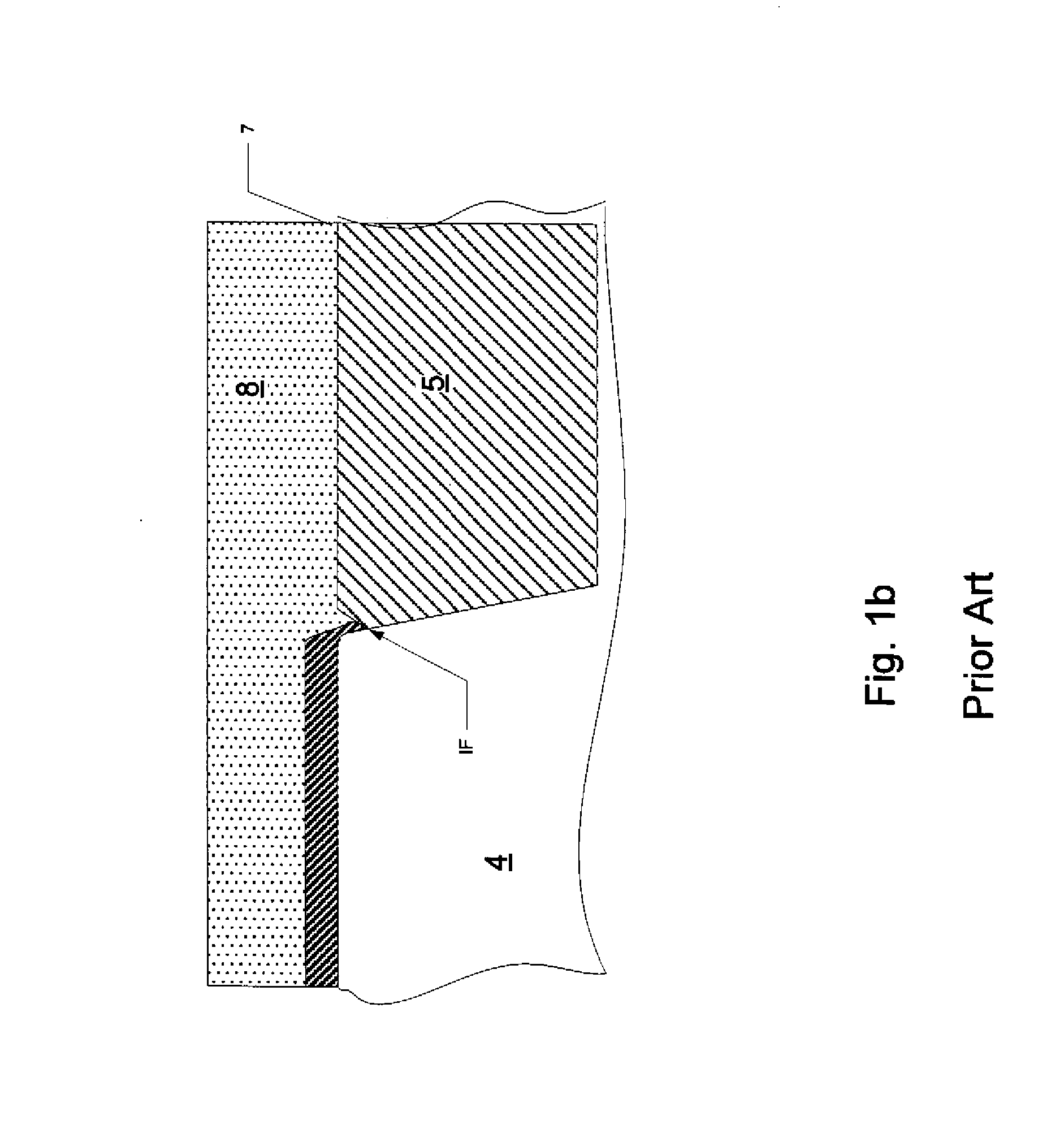

[0027]FIGS. 2a and 2b illustrate in plan view, and FIGS. 2c and 2d in cross-sectional views, the construction of transistor 20 according to embodiments of this invention. In this example, transistor 20 is a metal-oxide semiconductor (MOS) transistor formed at a selected location of the surface of single-crystal silicon substrate 22. More specifically, transistor 20 is an n-channel MOS transi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More