Patents

Literature

49 results about "Subthreshold conduction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

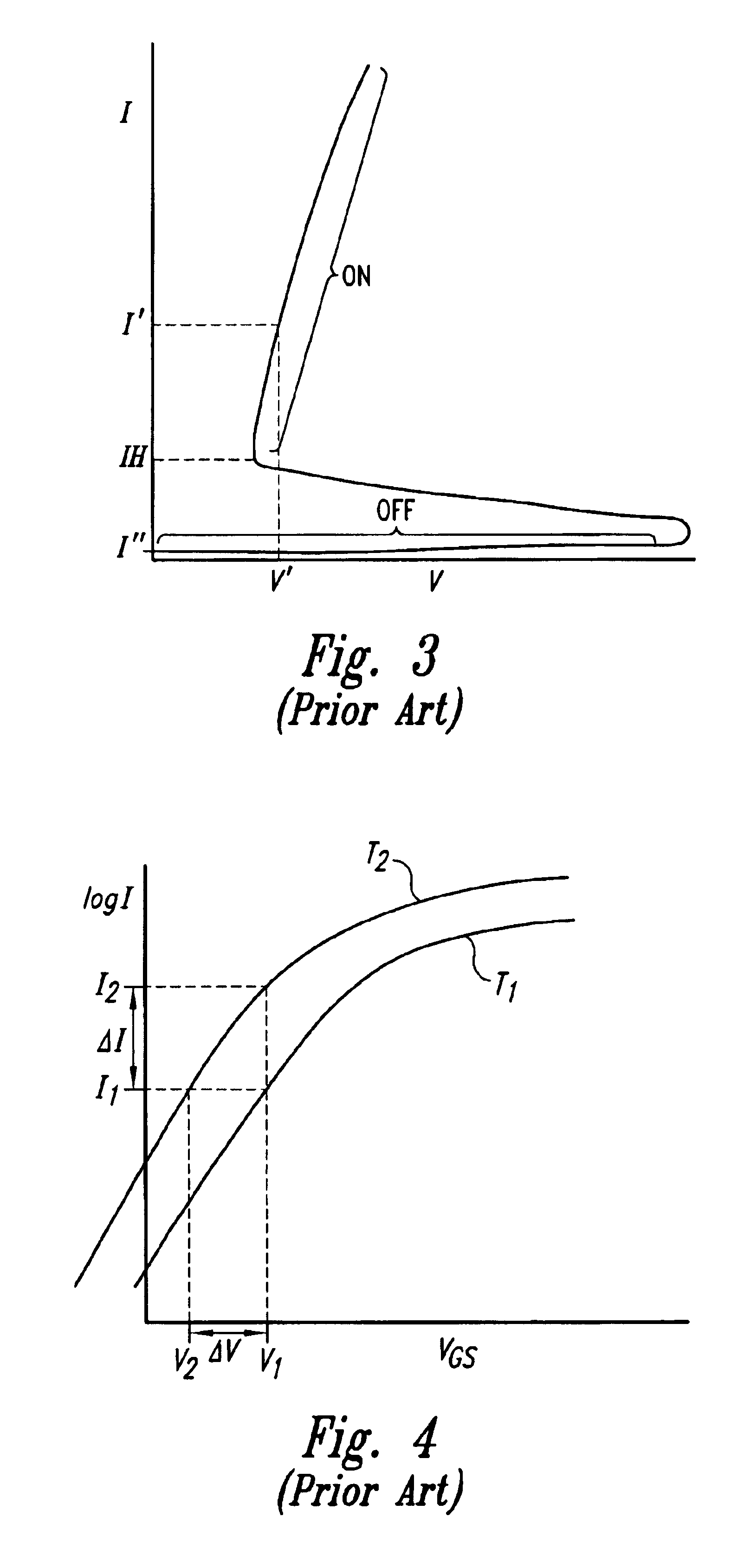

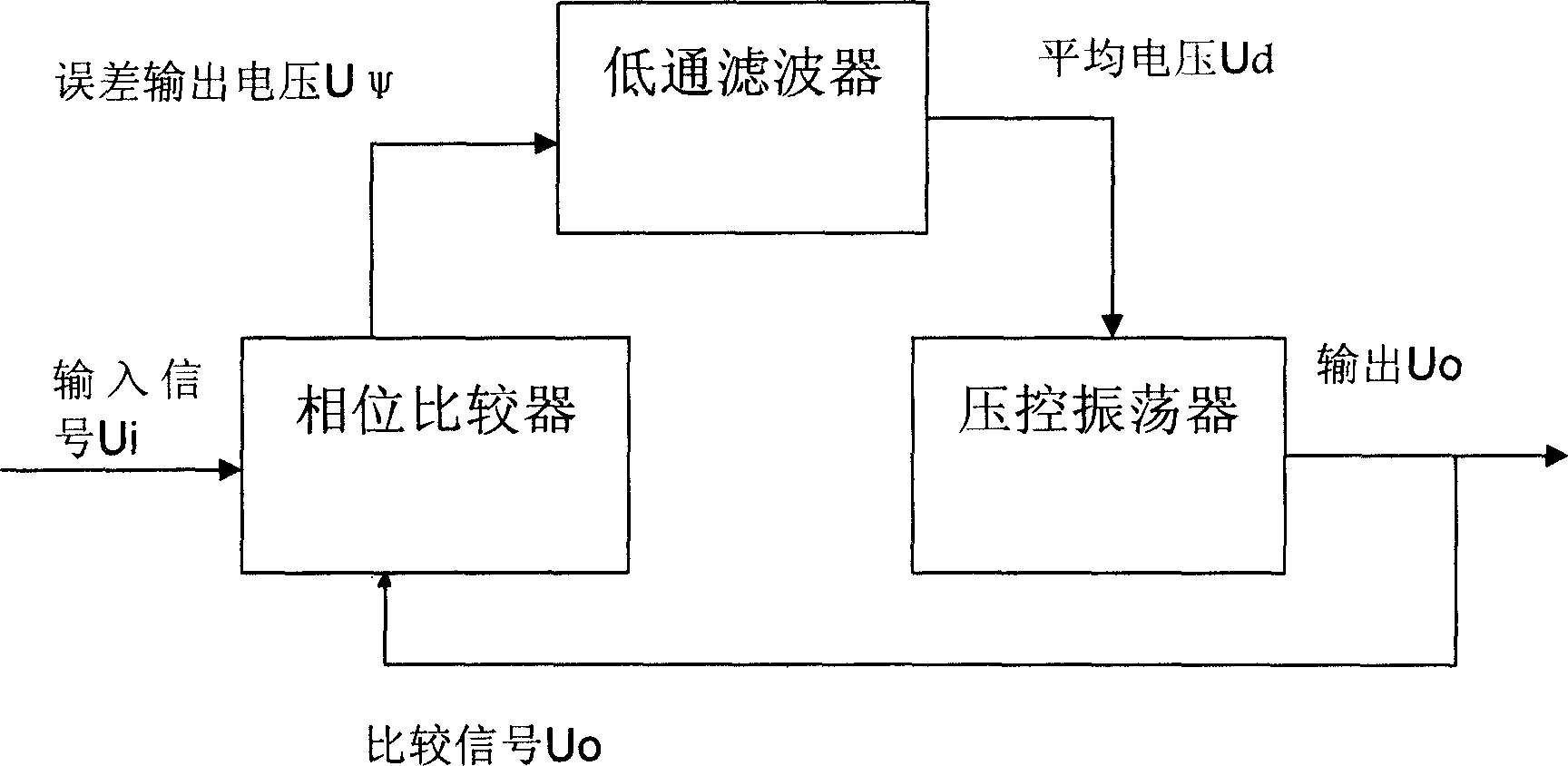

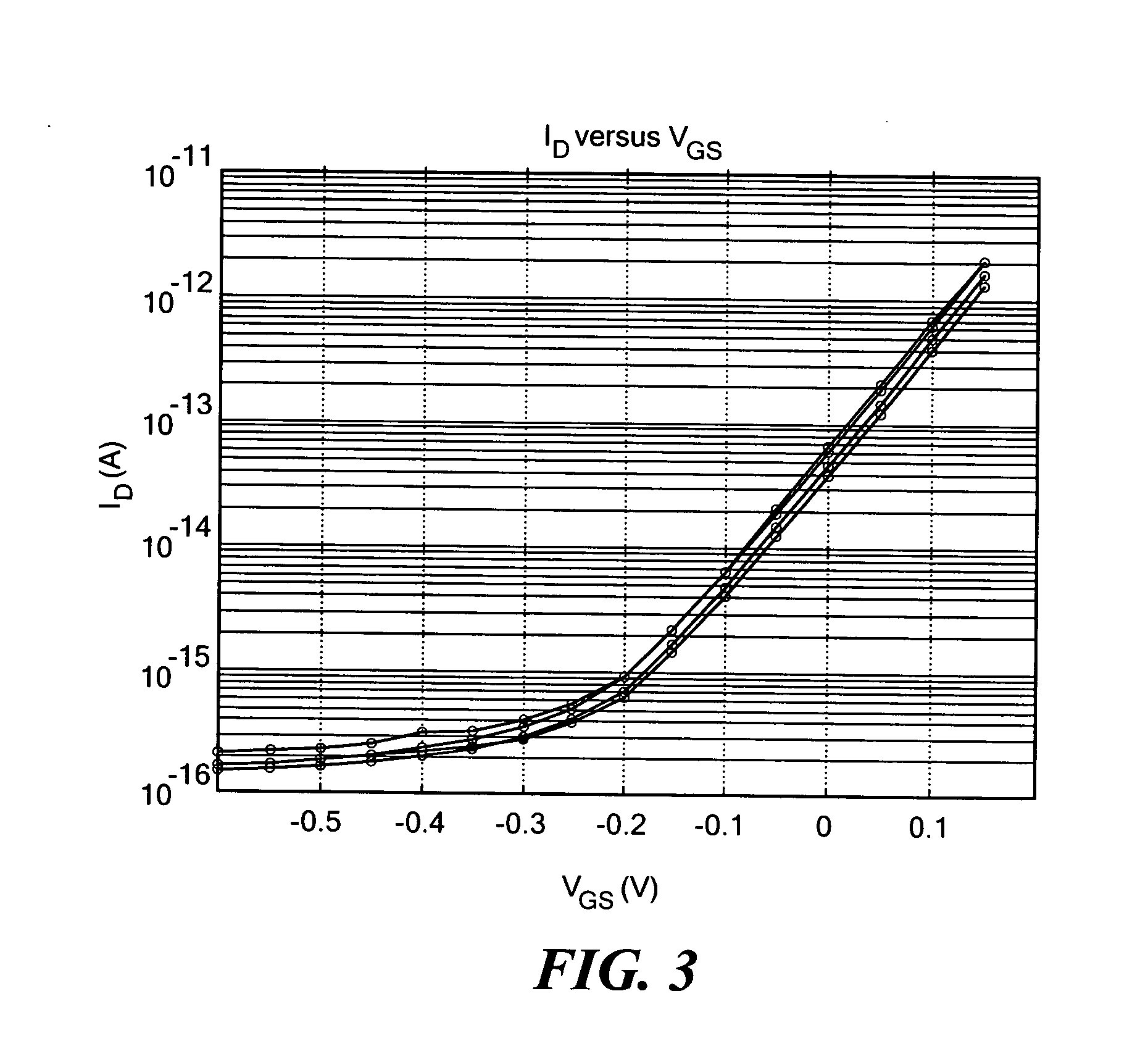

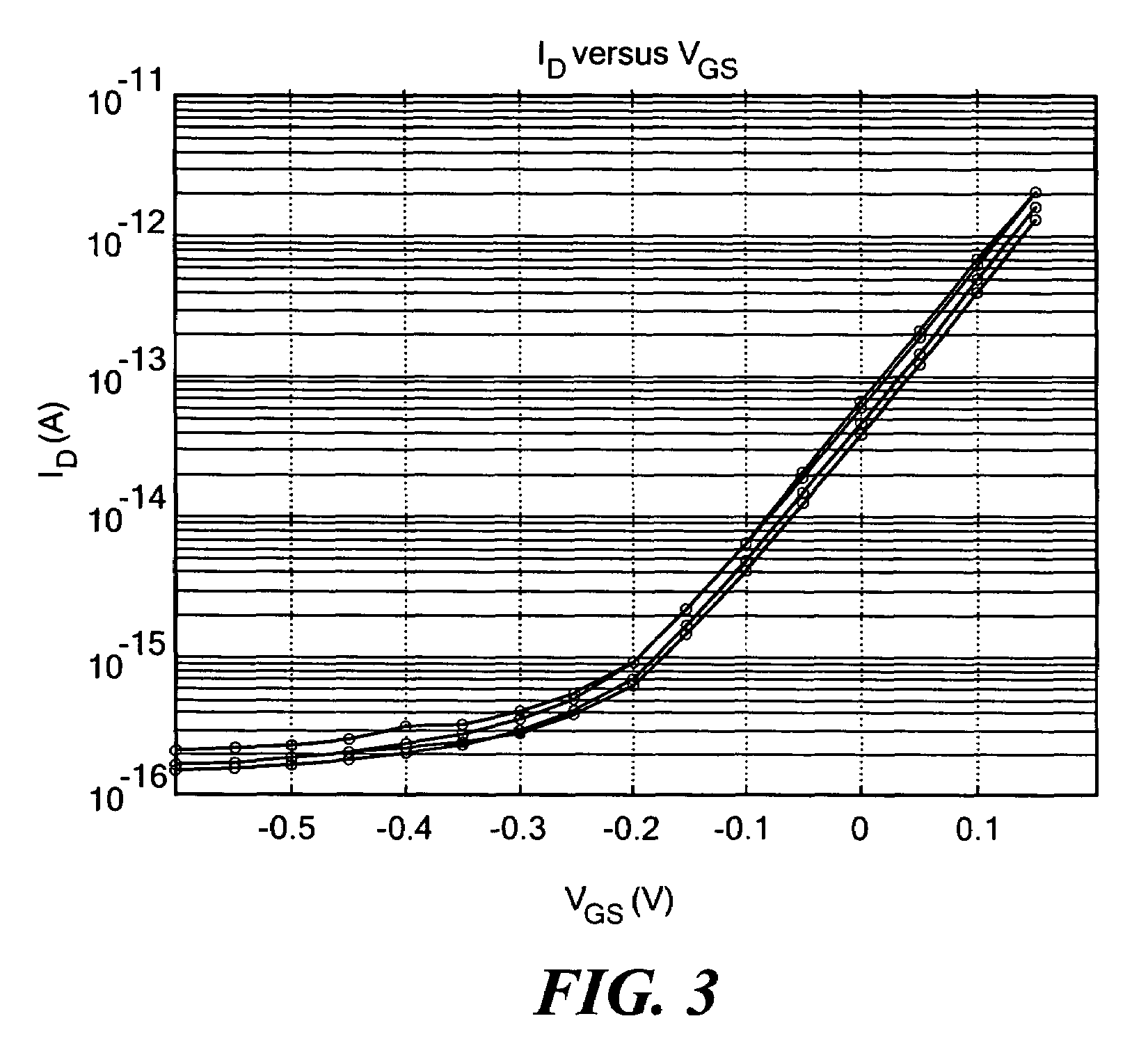

Subthreshold conduction or subthreshold leakage or subthreshold drain current is the current between the source and drain of a MOSFET when the transistor is in subthreshold region, or weak-inversion region, that is, for gate-to-source voltages below the threshold voltage. The terminology for various degrees of inversion is described in Tsividis.

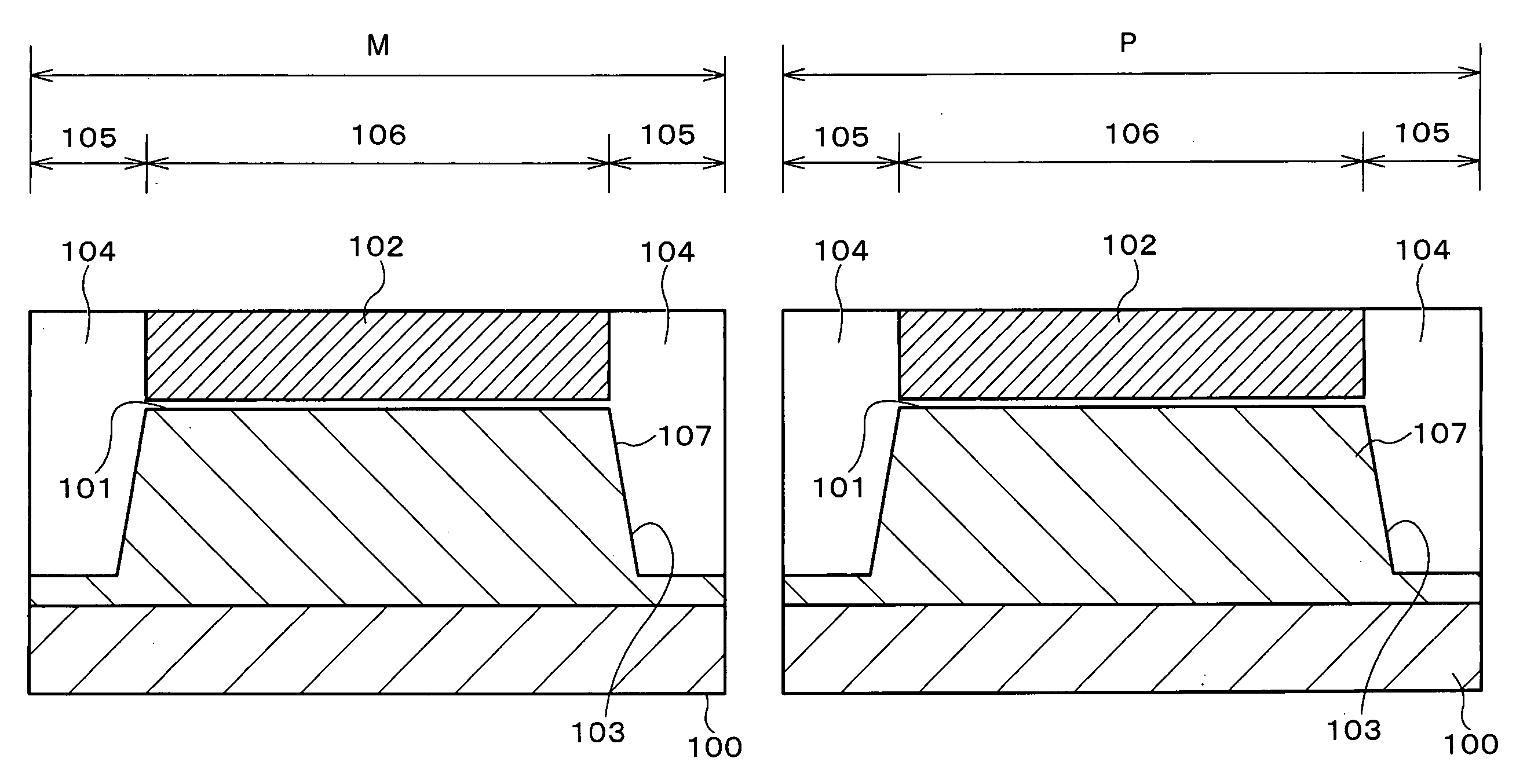

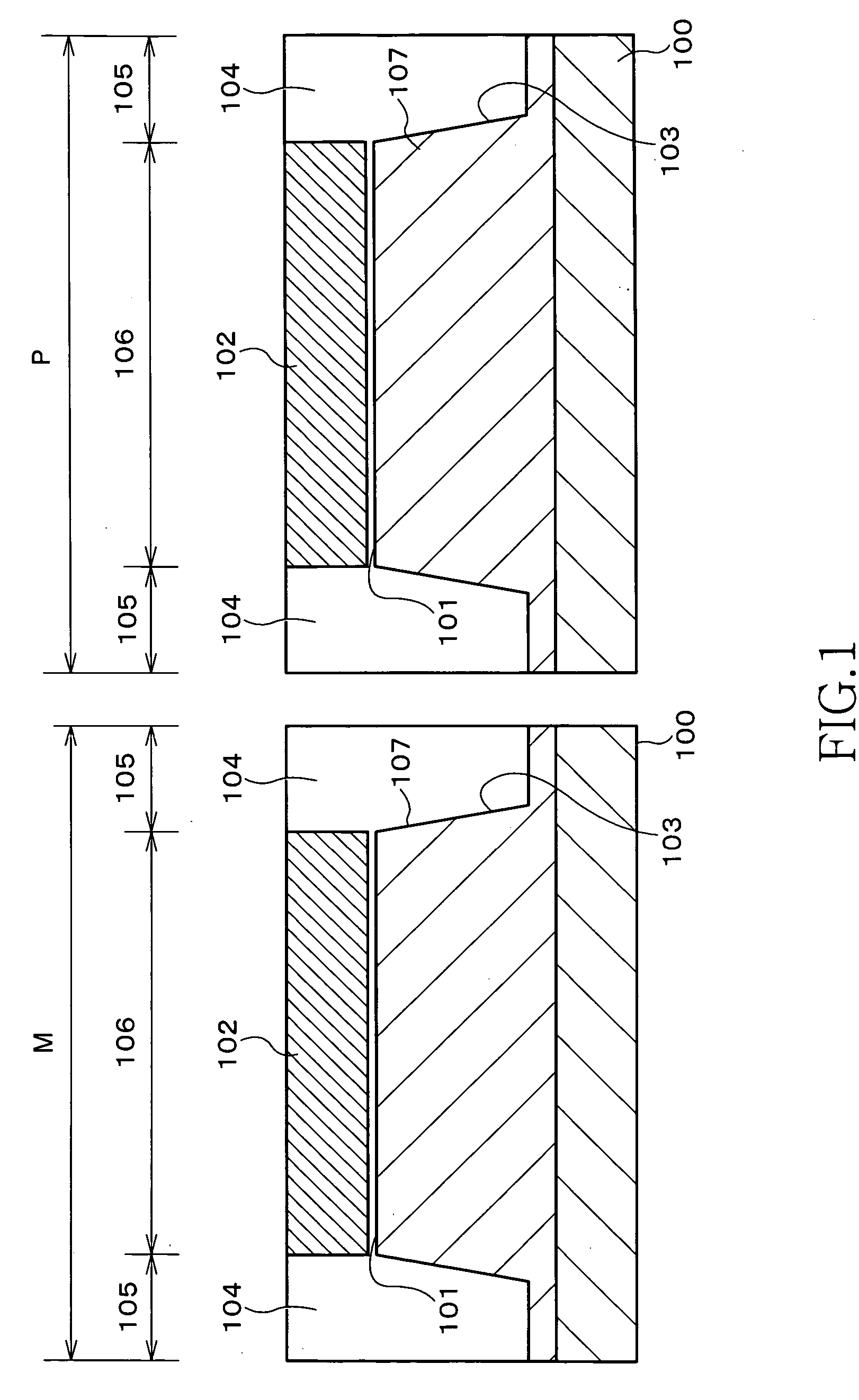

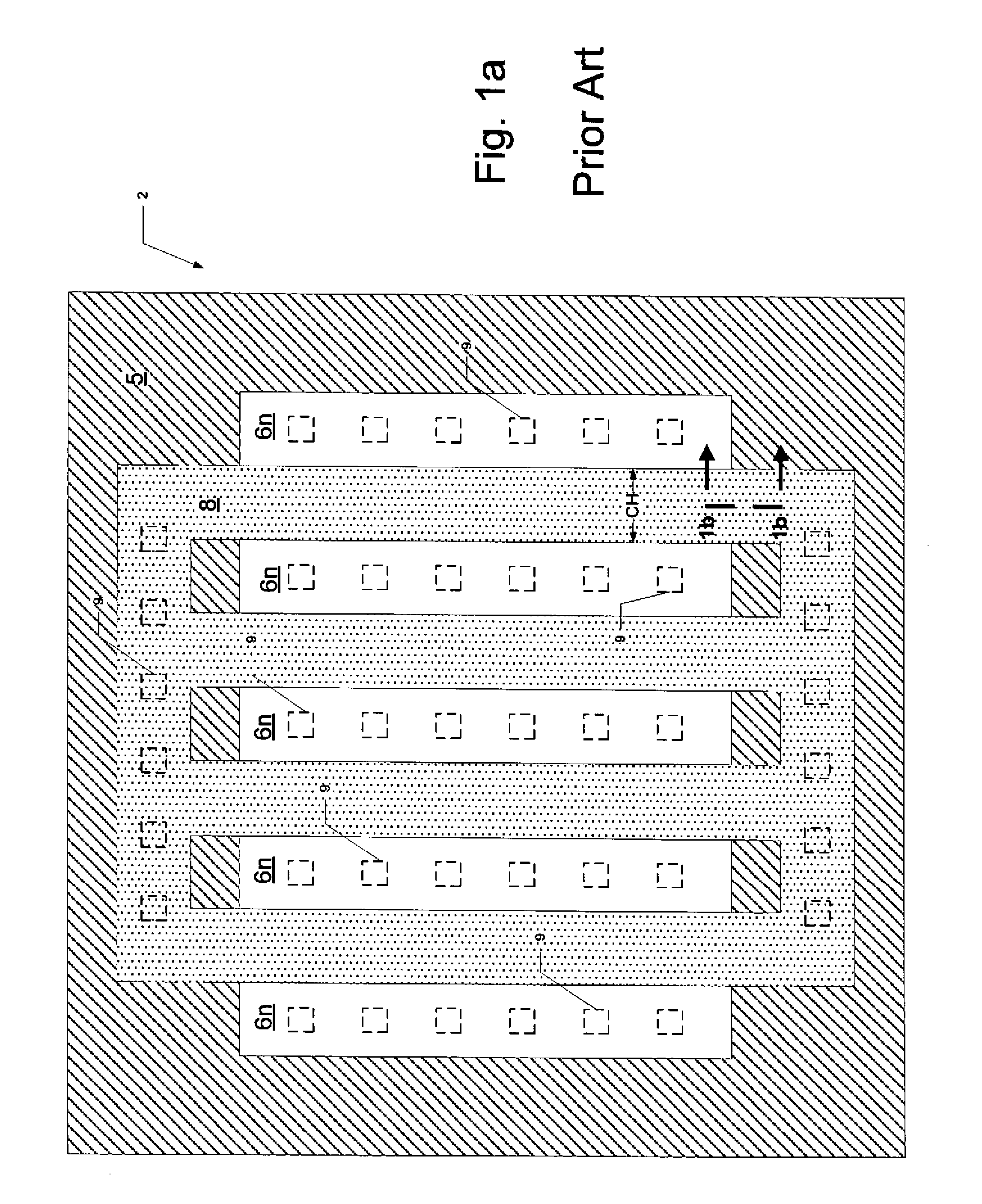

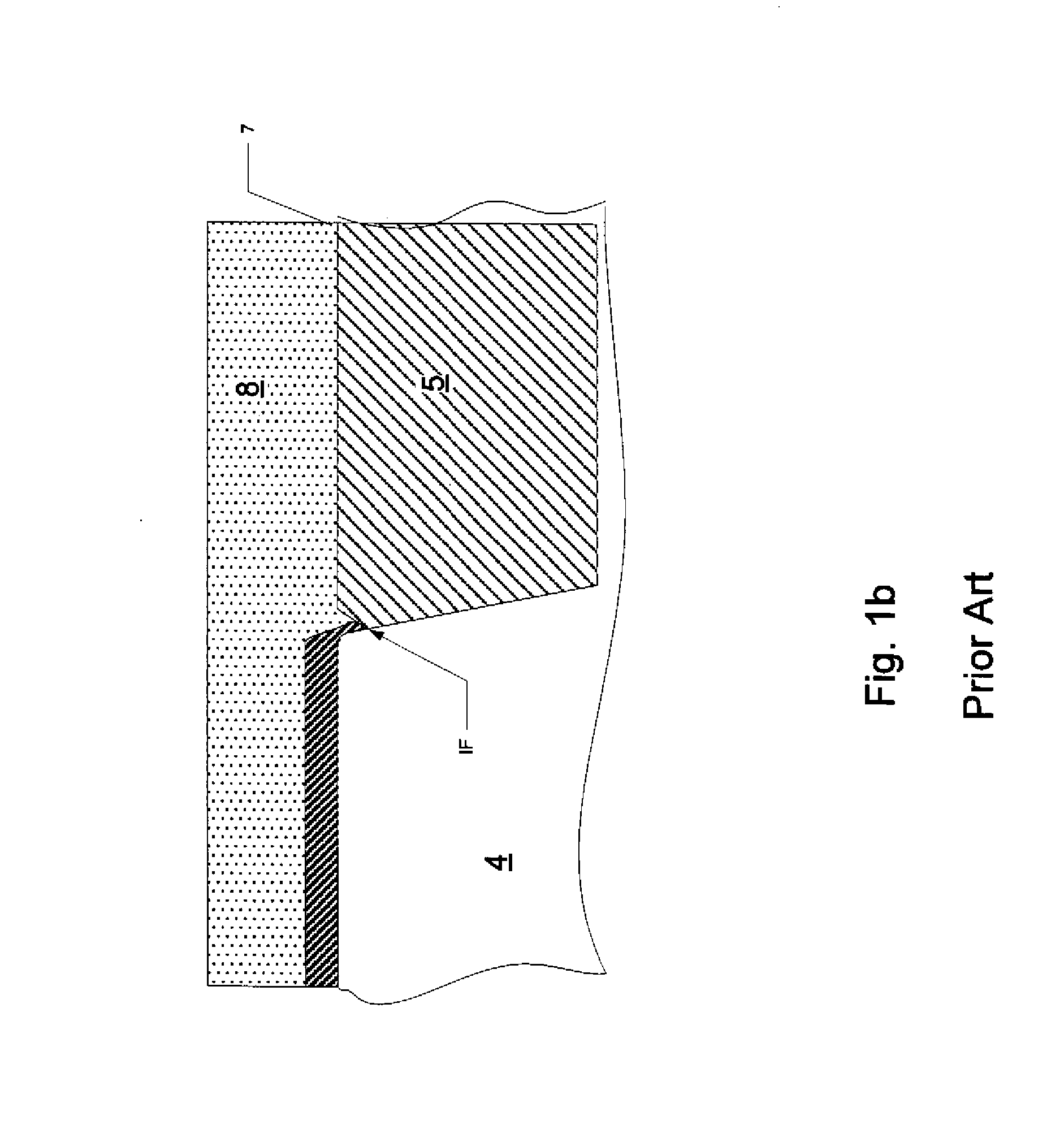

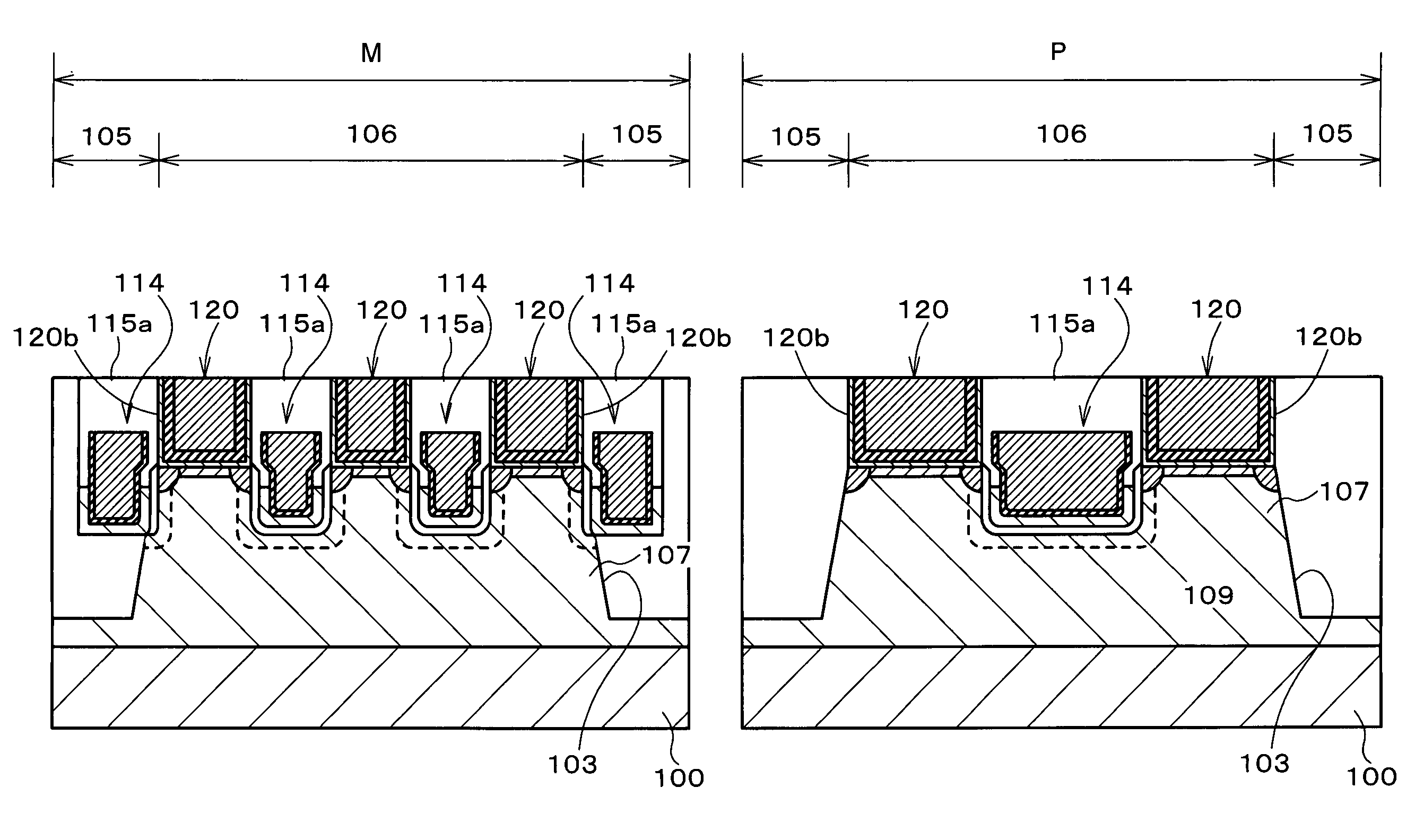

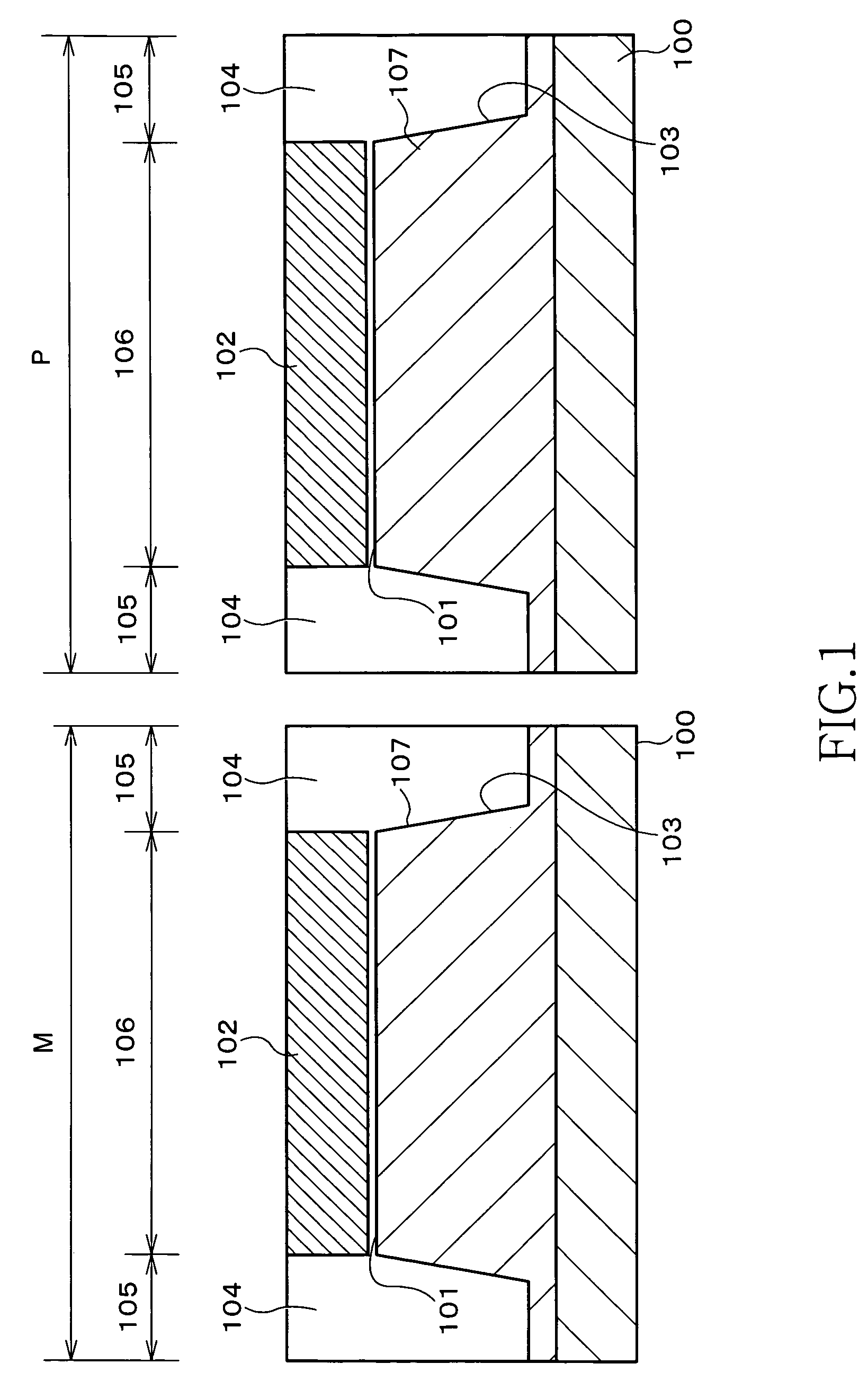

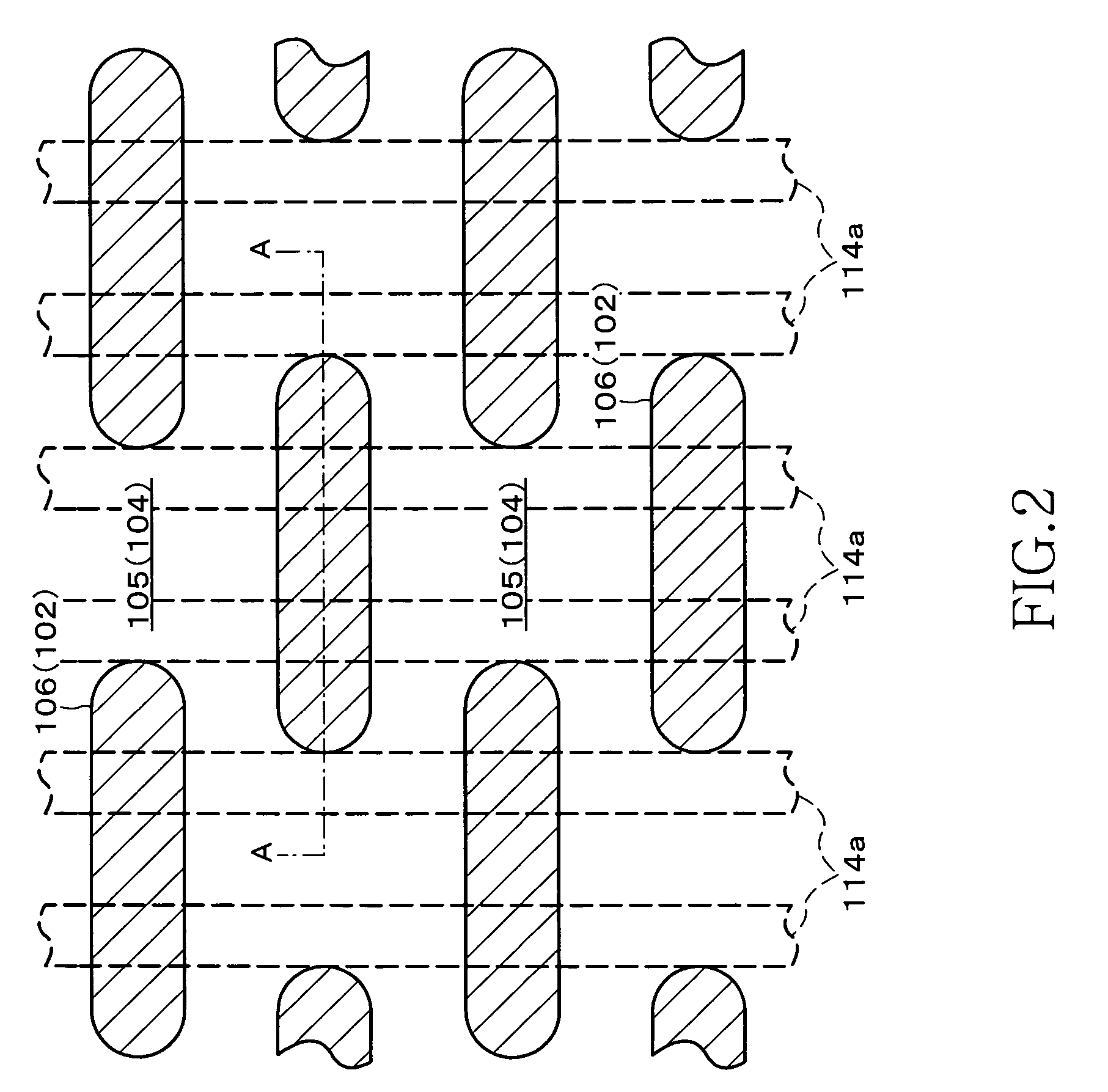

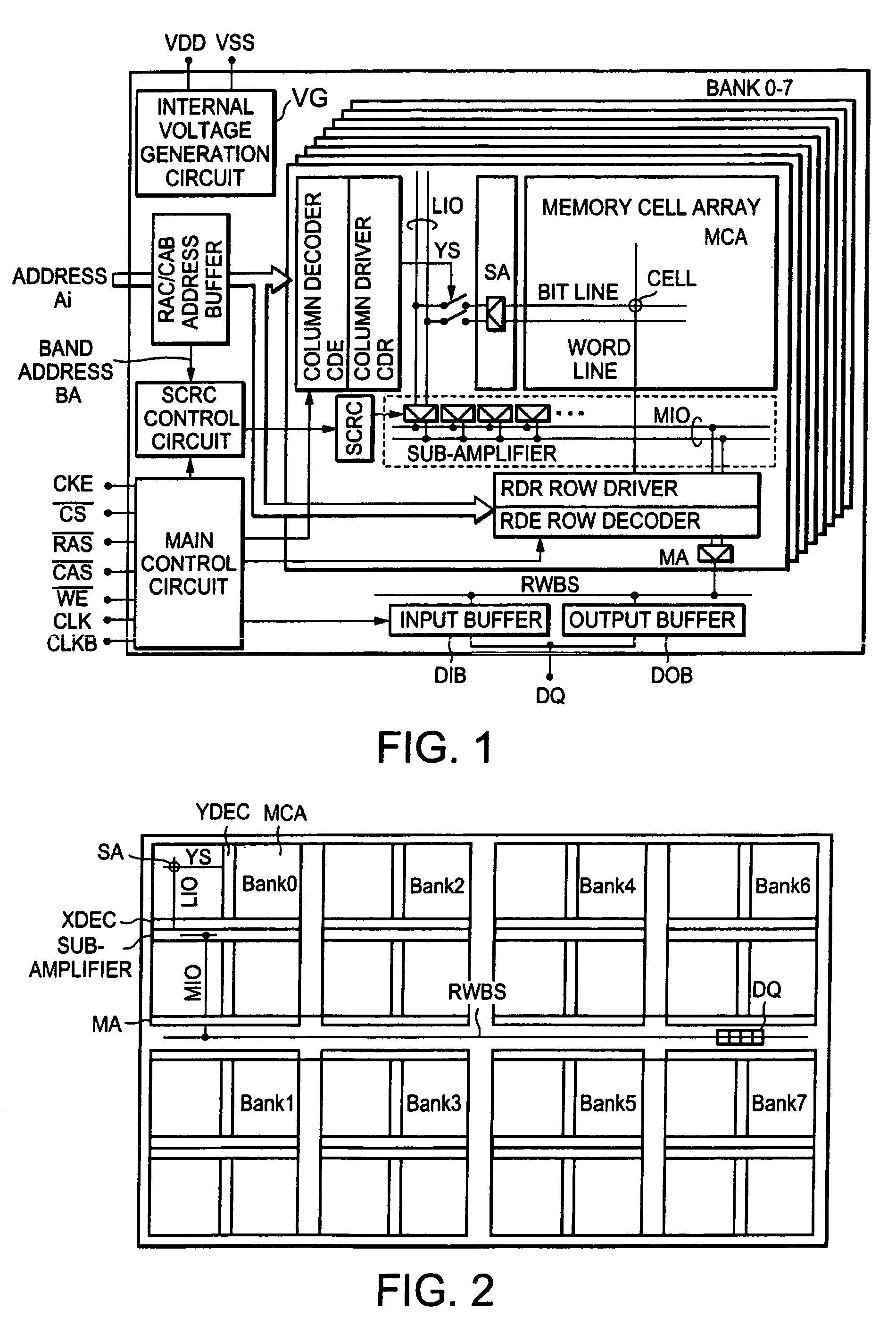

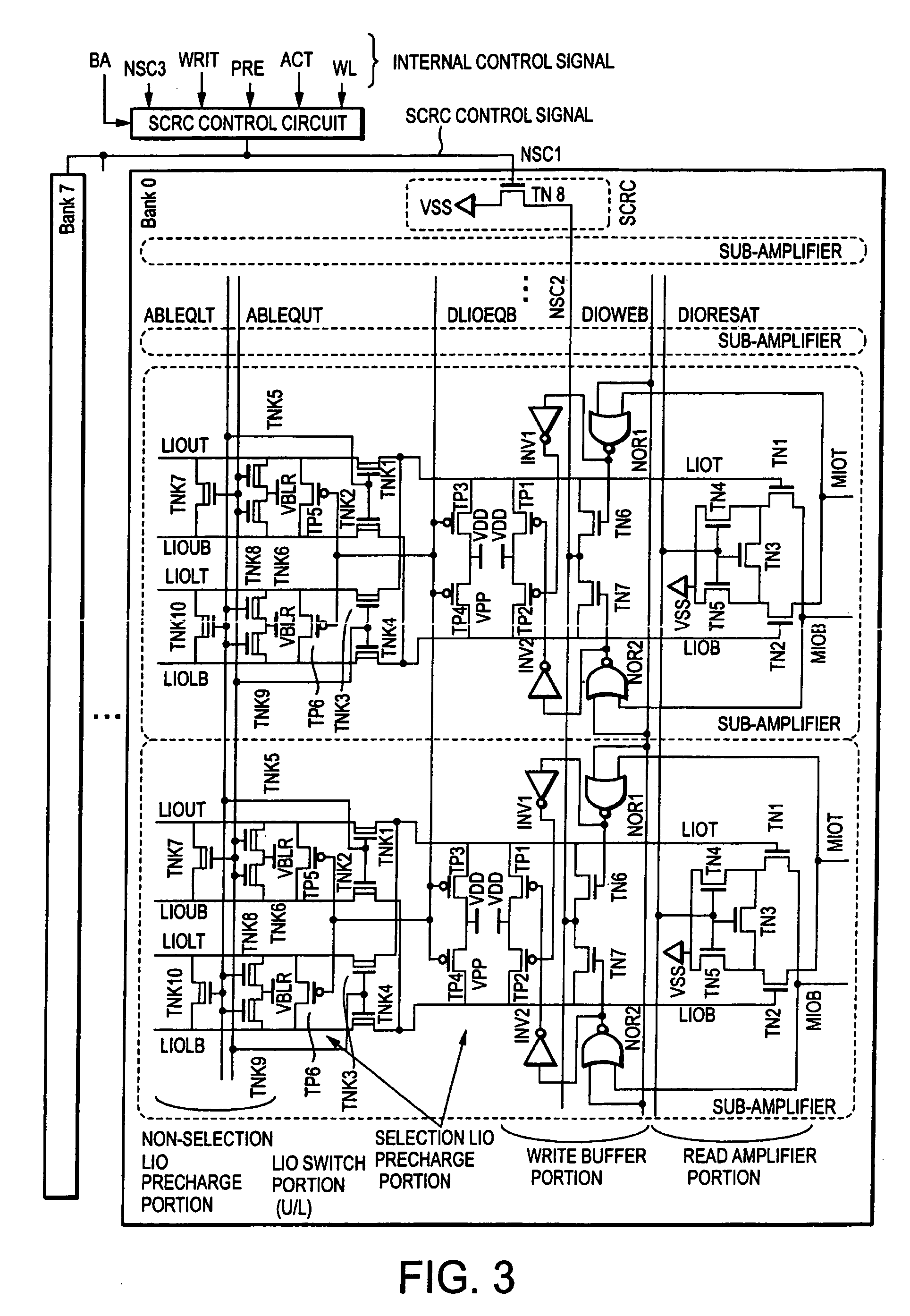

Semiconductor device and method of manufacturing the same

ActiveUS20060097314A1Reduce stepsHighly integratedSolid-state devicesSemiconductor/solid-state device manufacturingSub thresholdSubthreshold conduction

After an element isolation region is formed using a field-forming silicon nitride film, the silicon nitride film and a semiconductor substrate are patterned. Thereafter, the silicon nitride film and the semiconductor substrate are patterned, thereby forming a gate trench reaching the semiconductor substrate in an active region. Next, after a gate electrode is formed within a gate trench, the silicon nitride film is removed, thereby forming a contact hole. A contact plug is buried into this contact hole. Accordingly, a diffusion layer contact pattern becomes unnecessary, and the active region can be reduced. Because a gate electrode is buried in the gate trench, a gate length is increased, and a sub-threshold current can be reduced.

Owner:LONGITUDE LICENSING LTD

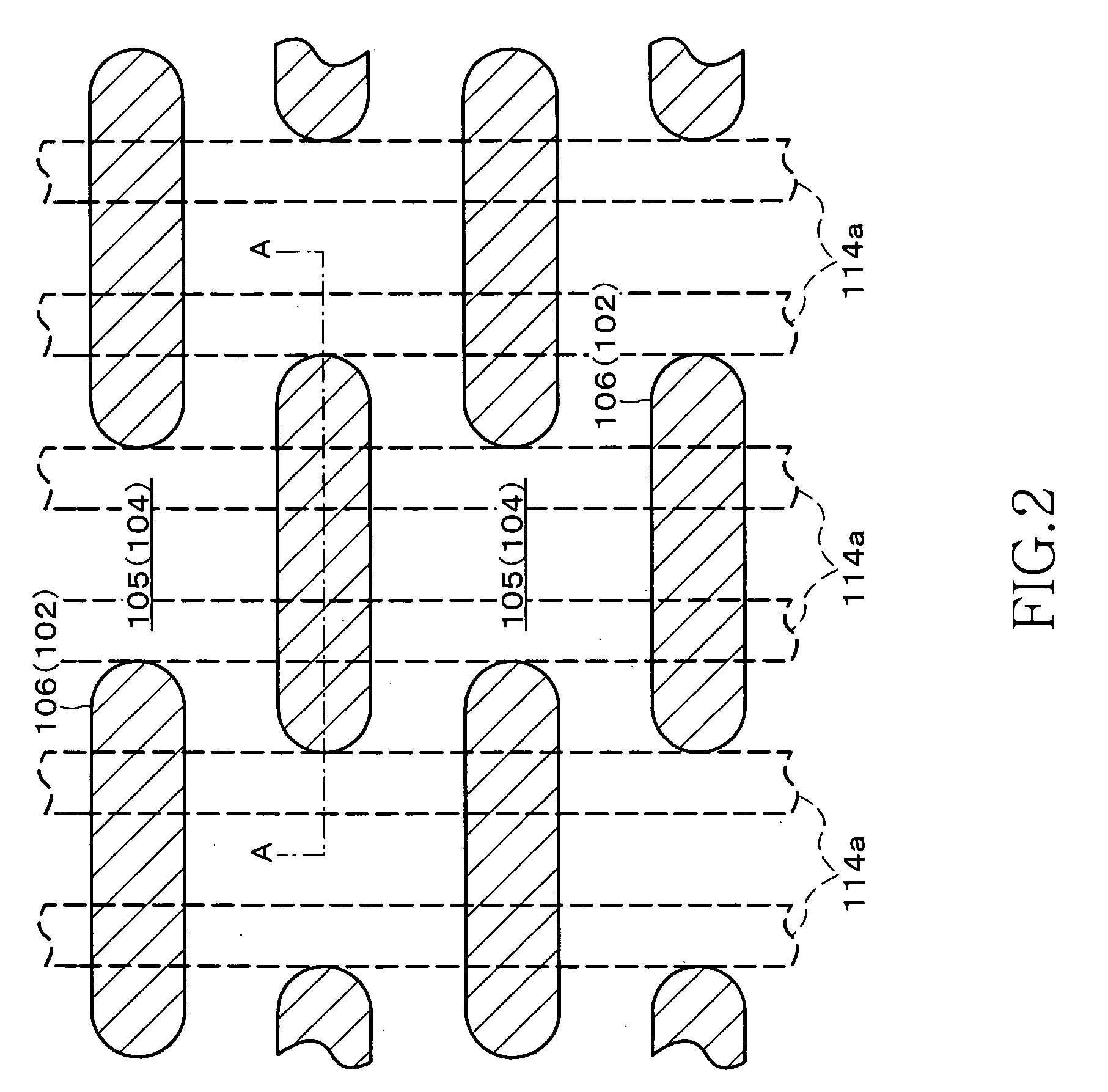

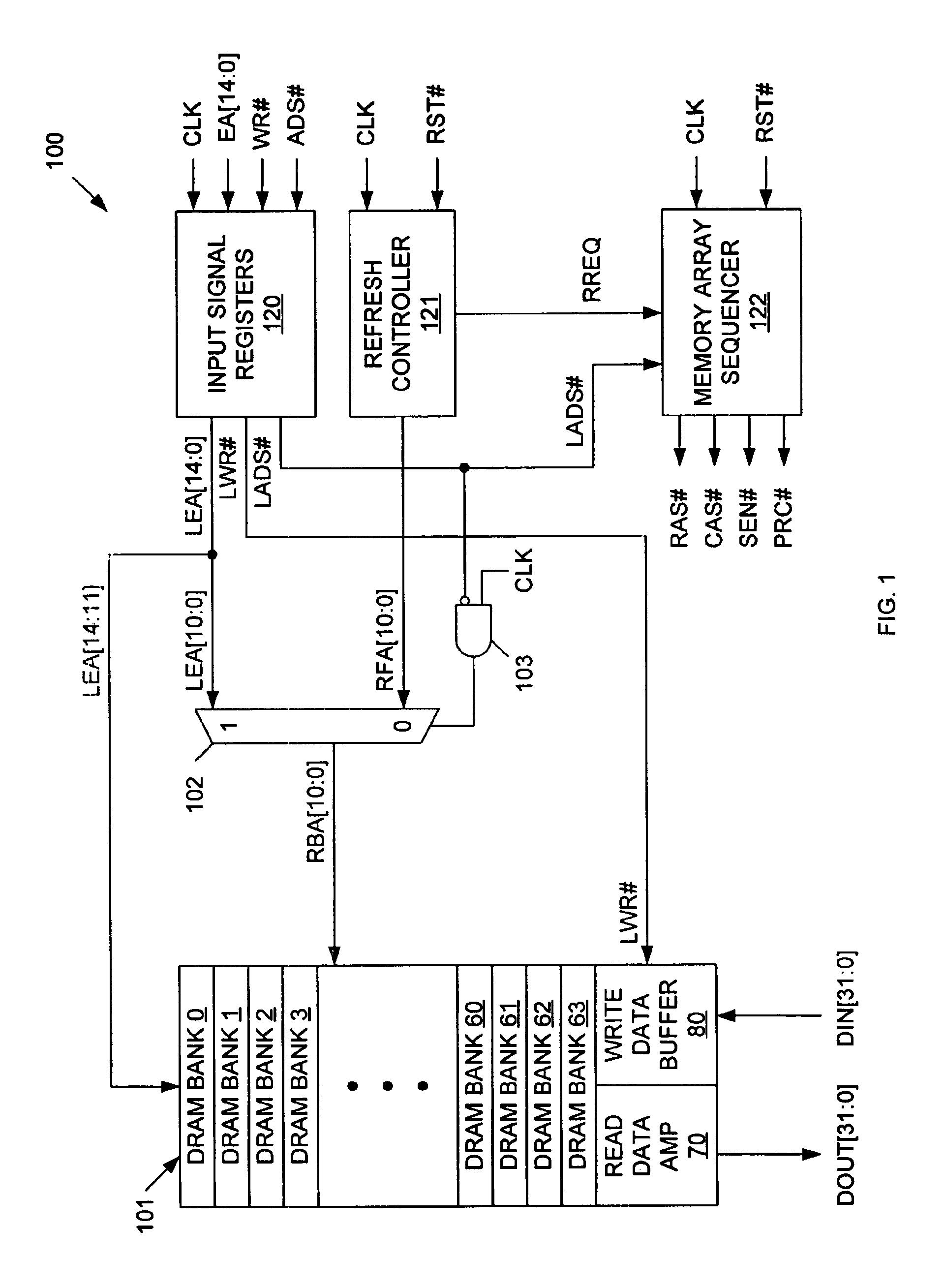

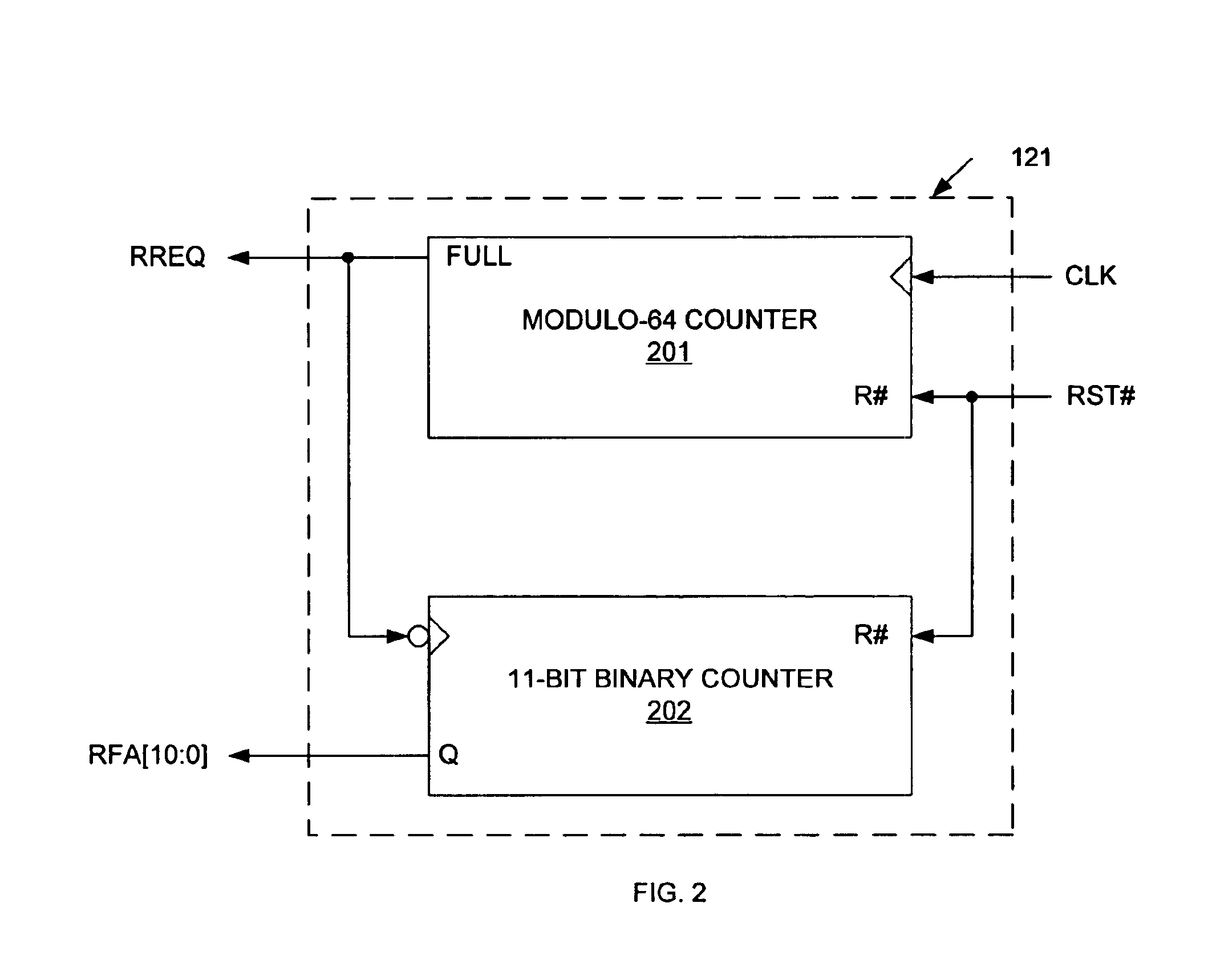

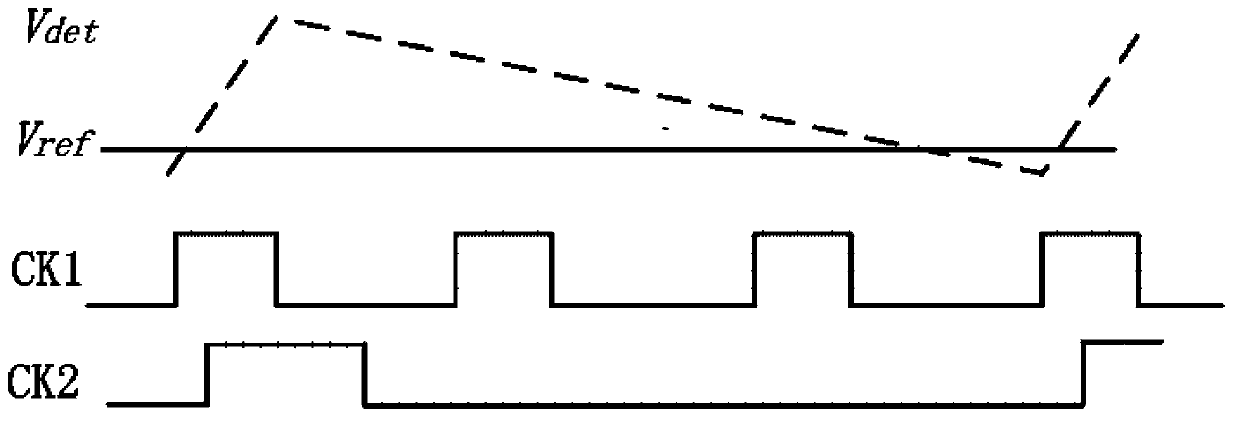

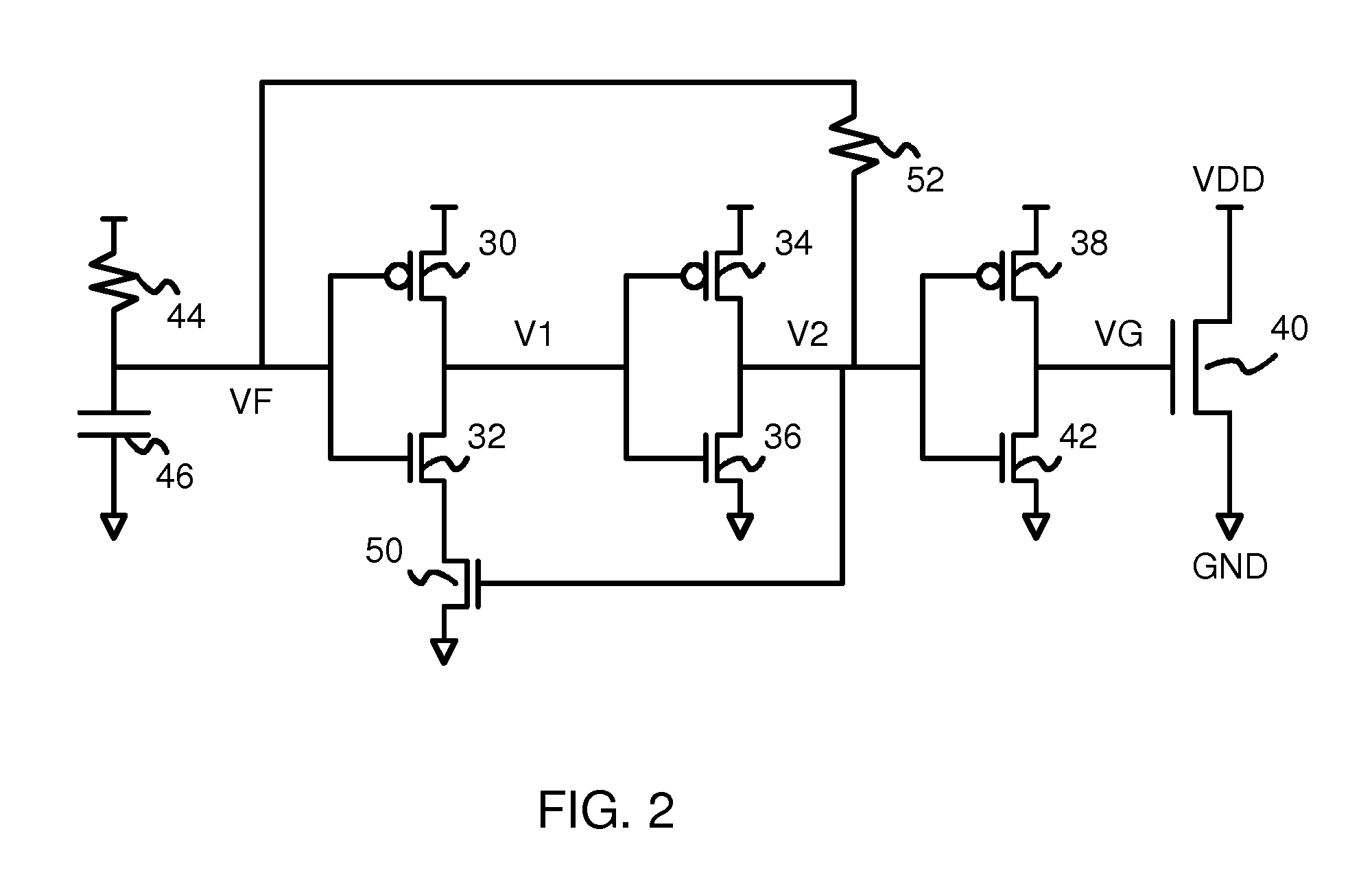

Method and apparatus for temperature adaptive refresh in 1T-SRAM compatible memory using the subthreshold characteristics of MOSFET transistors

A memory system is provided that includes an array of memory cells that require periodic refresh, and a temperature-adaptive refresh controller. Data retention time of the memory cells decreases exponentially as temperature increases. The temperature-adaptive refresh controller selects the refresh period of the memory cells in response to the subthreshold current of a reference transistor. The subthreshold current of the reference transistor increases exponentially as temperature increases As a result, the refresh period is empirically tied to the data retention time. Consequently, the power required for refresh operations decreases as temperature decreases. Power is therefore conserved in applications that operate predominantly at room temperature.

Owner:INVENSAS CORP

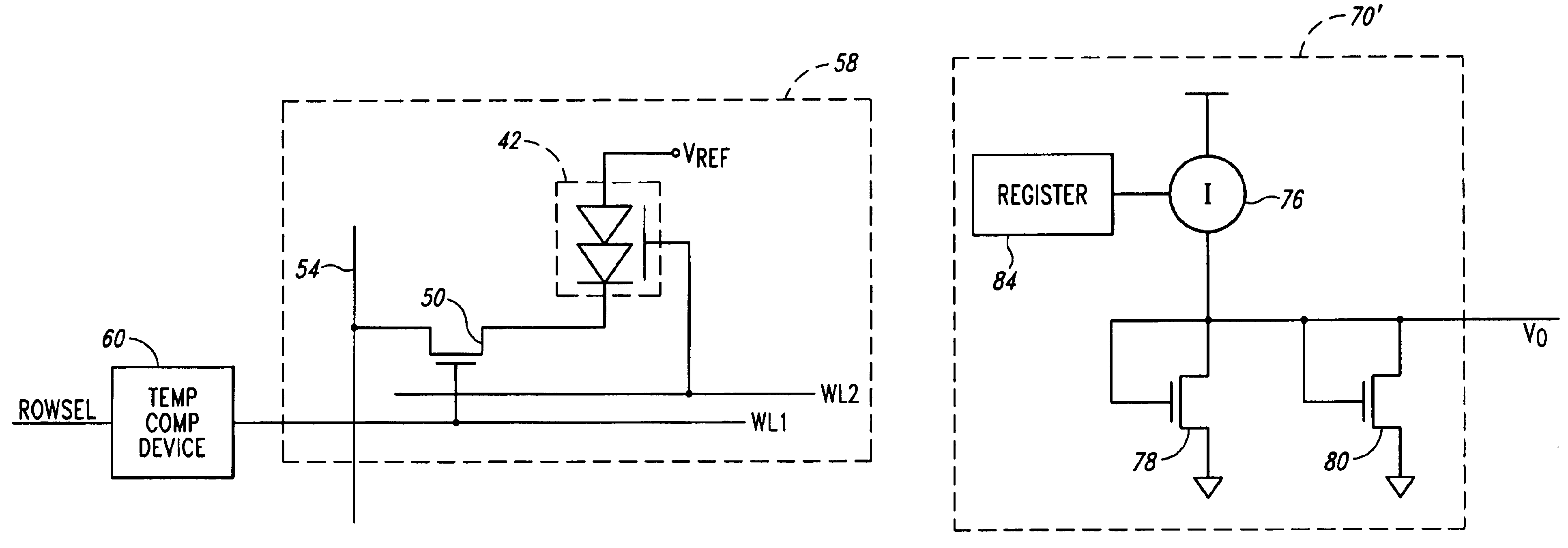

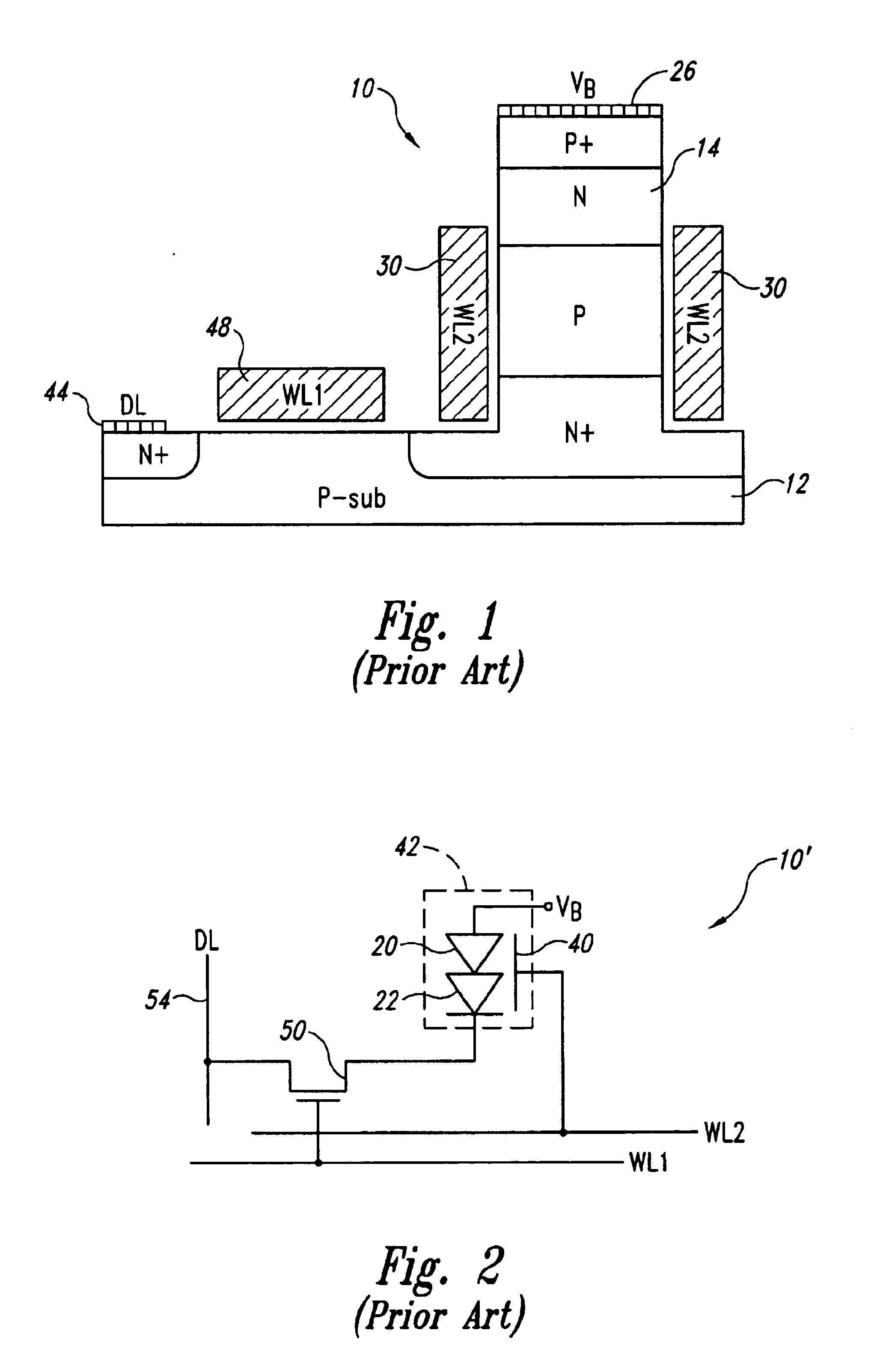

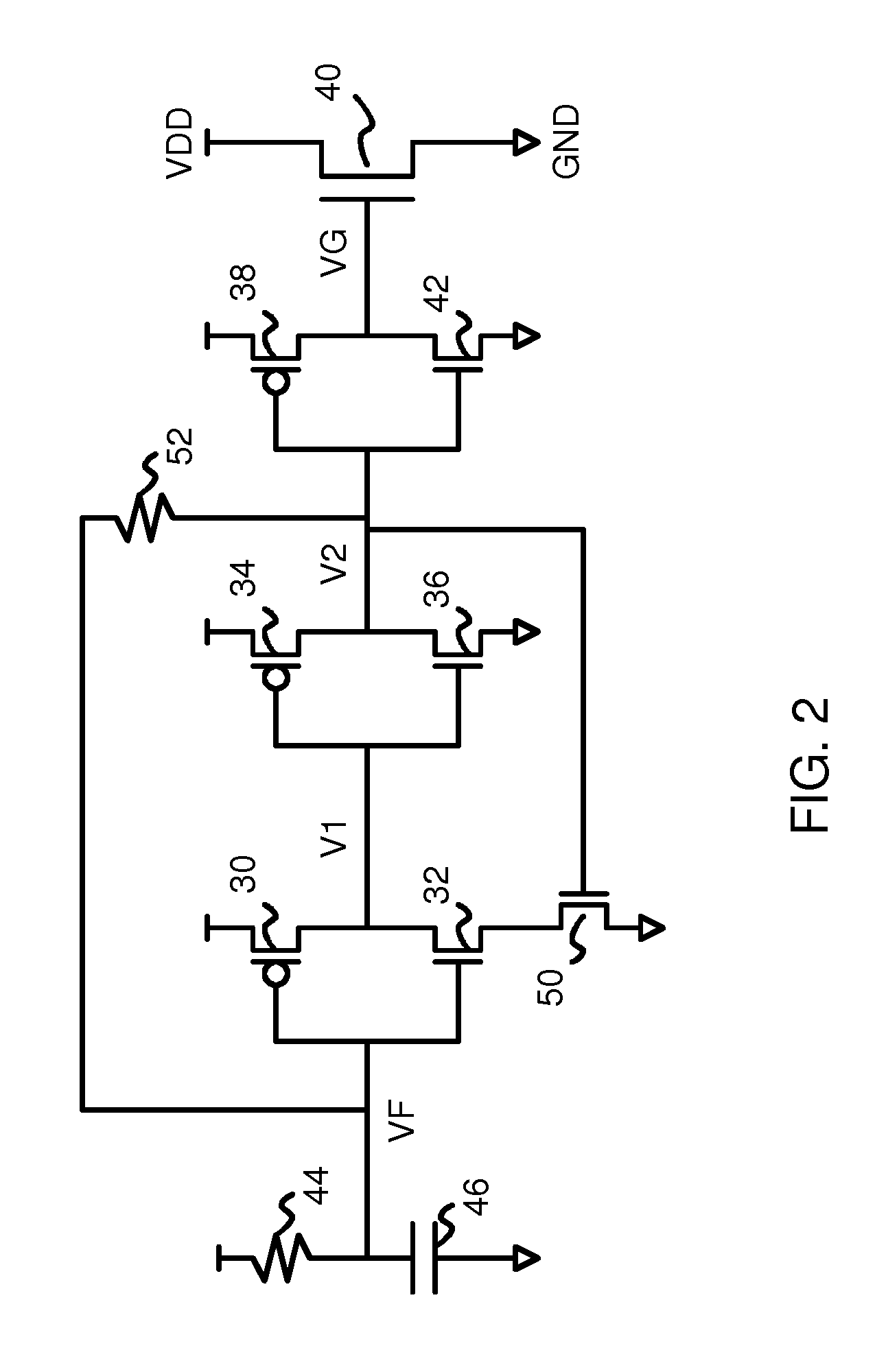

Temperature compensated T-RAM memory device and method

A T-RAM memory cell includes a temperature compensation device to adjust the gate-to-source voltage of an access transistor for the memory cell as a function of temperature so that the sub-threshold current of the transistor is insensitive to temperature variations. As a result, the sub-threshold current can be maintained slightly above the holding current of a thyristor used in the memory cell despite substantial temperature variations. In one embodiment, the temperature compensation device includes a current source directing a fixed current through a diode-connected transistor of the type used as the memory cell access transistor. Temperature induced changes in a reference voltage generated at the junction between the current source and the transistor therefore match the temperature induced changed in the sub-threshold current of the access transistor. As a result, the sub-threshold current of the access transistor can be made insensitive to temperature variations by applying the reference voltage to the gate or source of the access transistor.

Owner:MICRON TECH INC

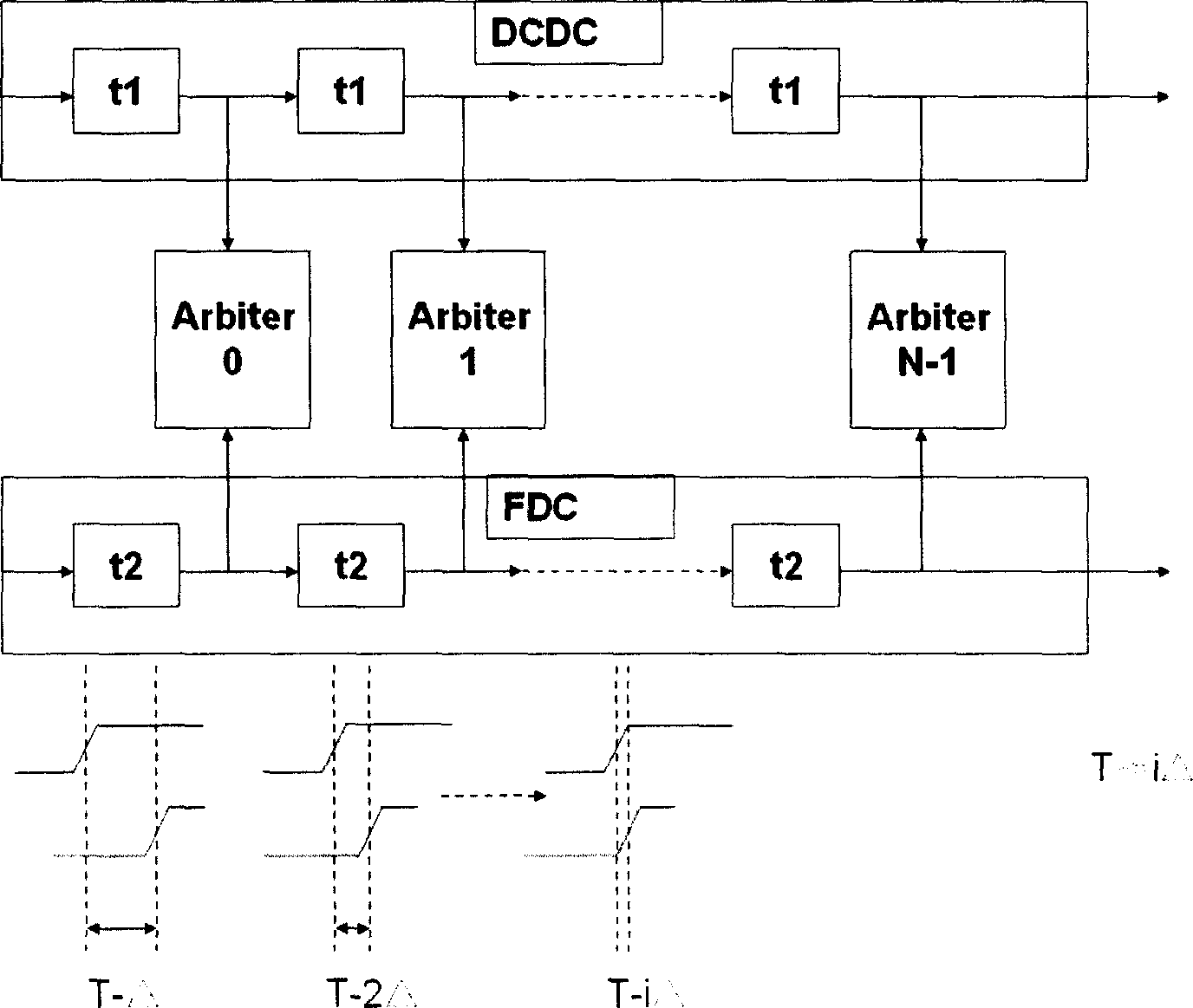

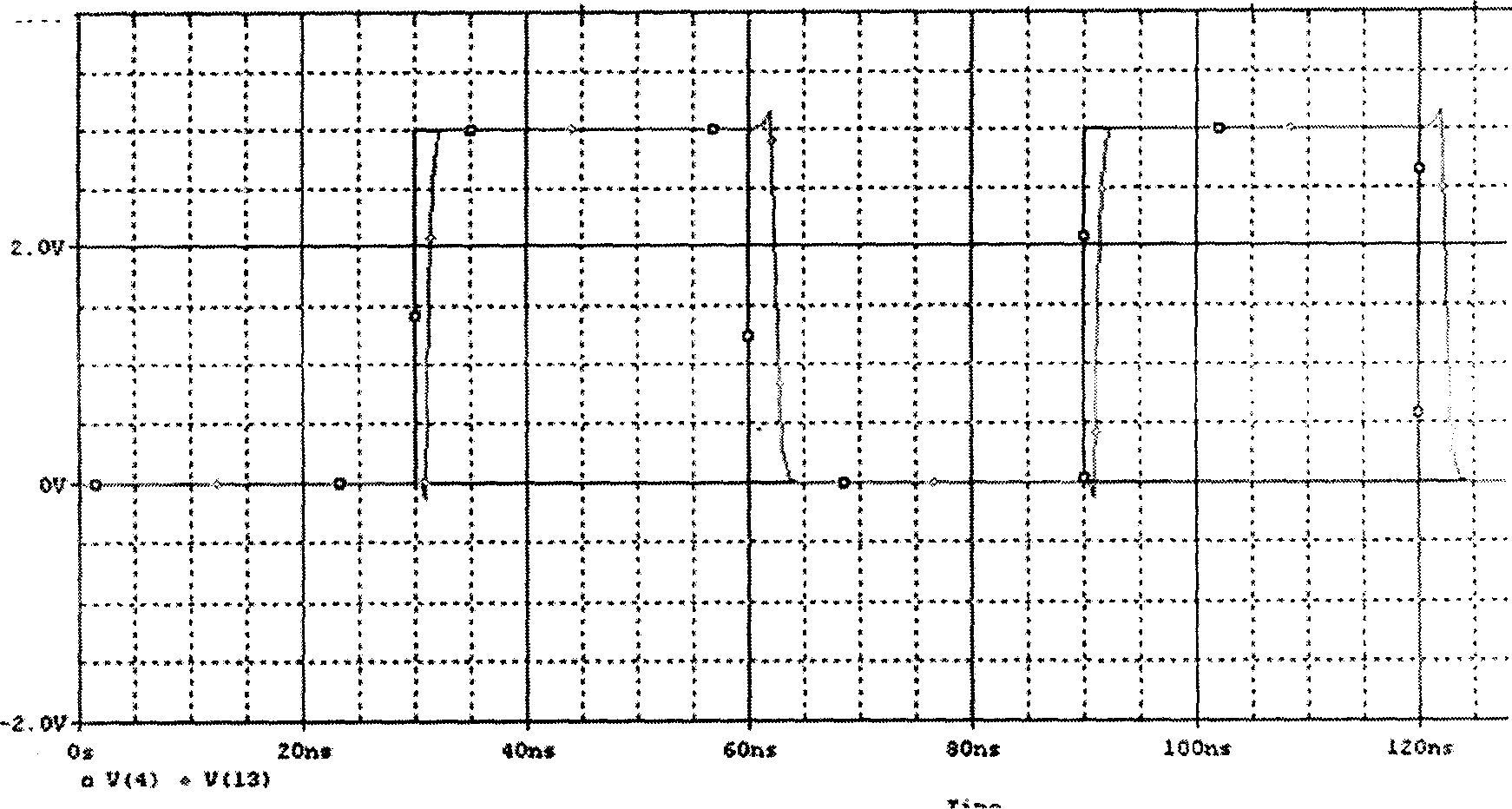

System for testing clock signal dither and method thereof

InactiveCN1862273AMeets extremely demanding test specificationsMeet the extremely high requirements of test specifications (such as time resolutionPulse automatic controlElectronic circuit testingTime delaysEngineering

The present invention relates to an on-chip system for testing clock signal flutter and its method, in particular, it relates to test of phase-locked loop flutter. The high time analyticity, low amplitude and differential signal are not influenced by element changeability. It includes subthreshold current control one-sided delay line with N time-delay units, reference delay line and test clock delay line. Besides, it also includes a arbiter and a calibrator. Said invention also provides the concrete steps of its test method.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

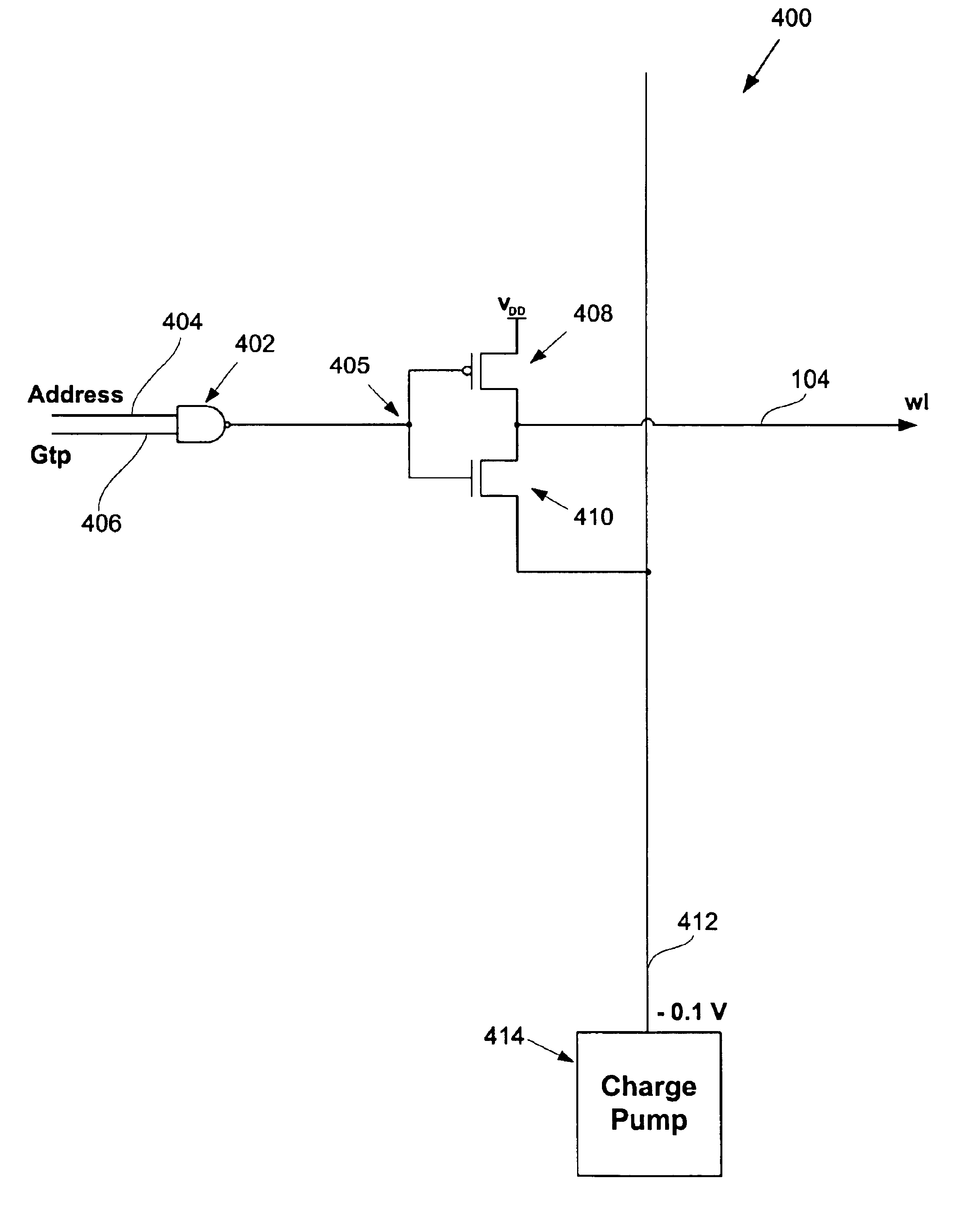

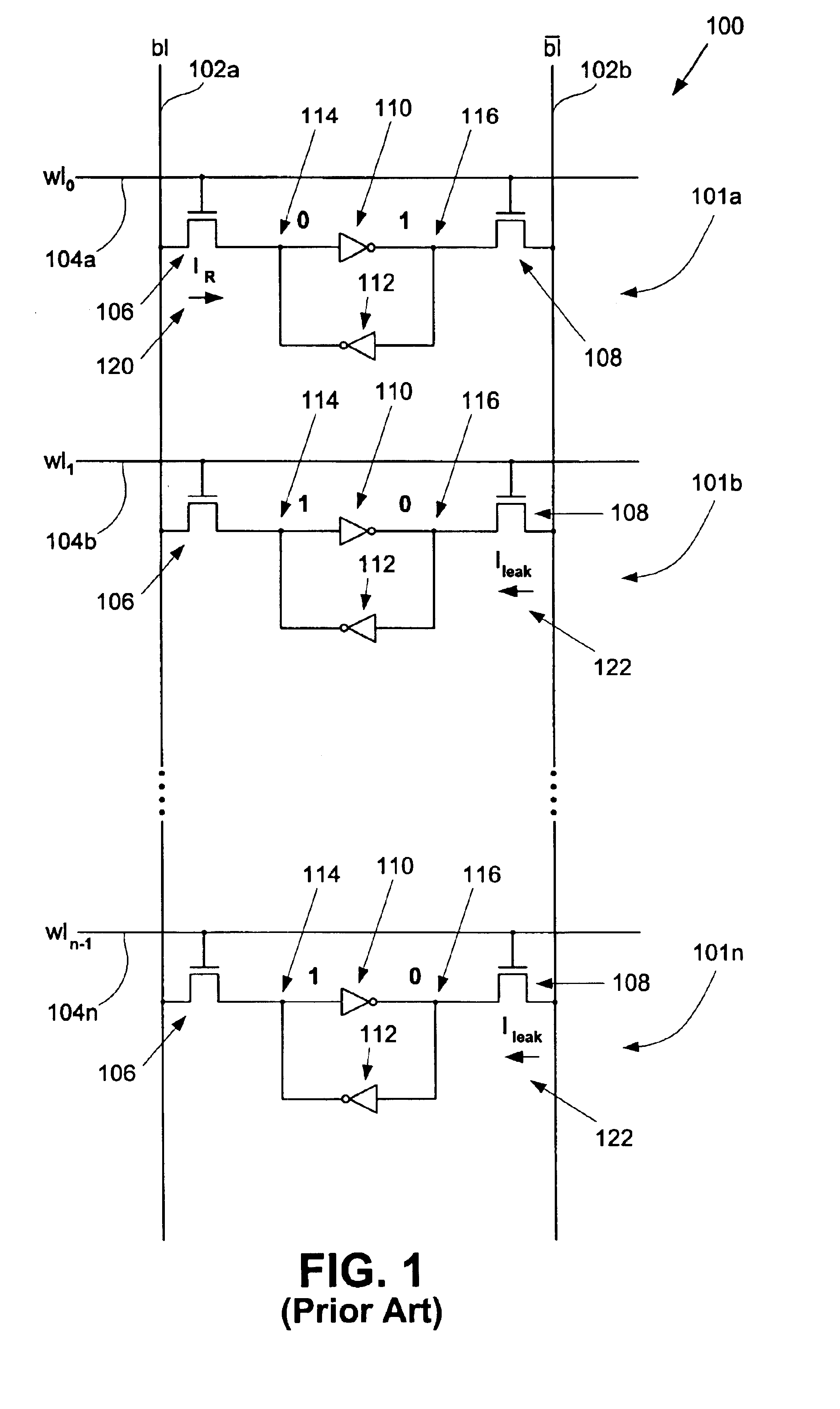

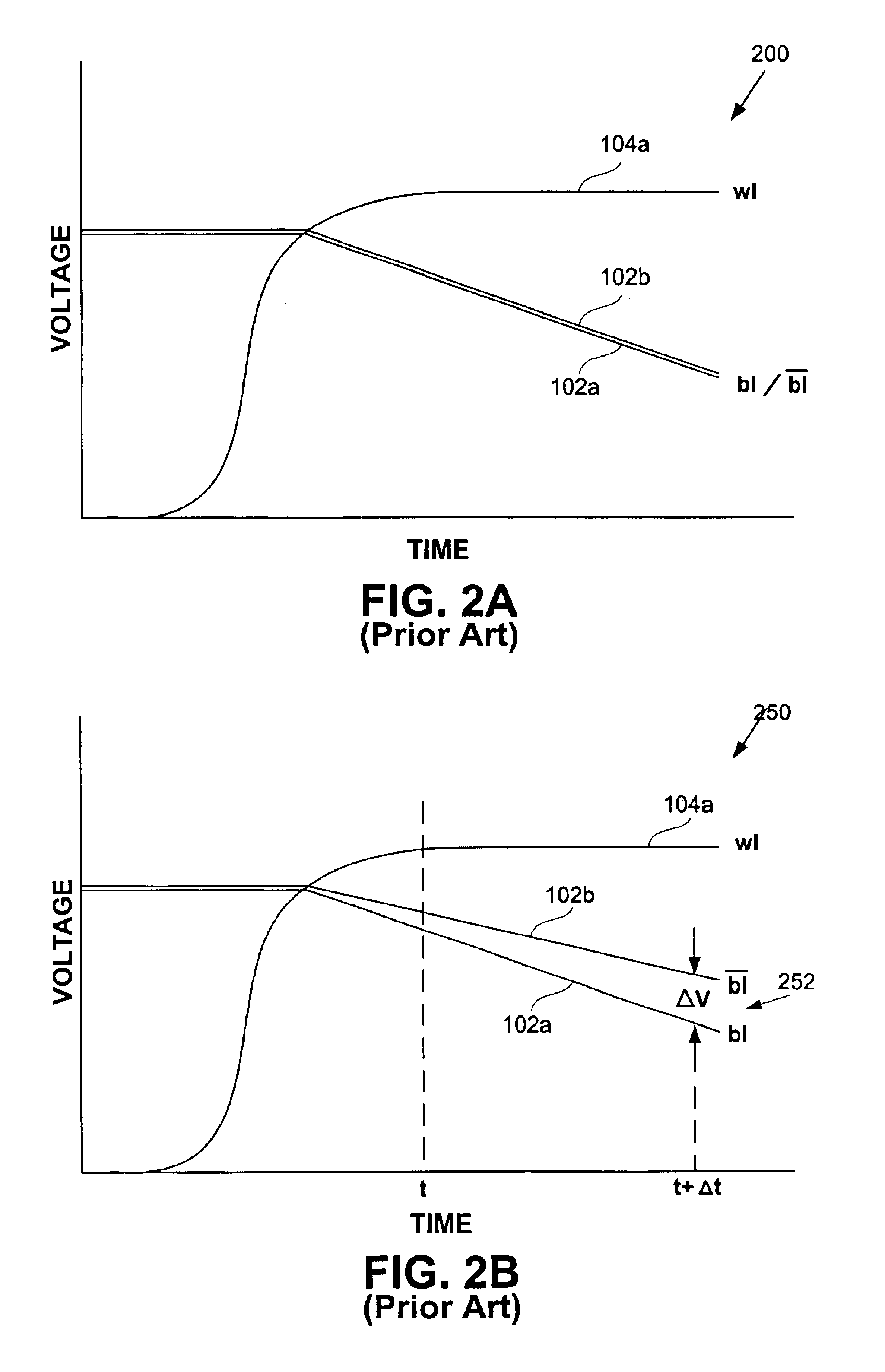

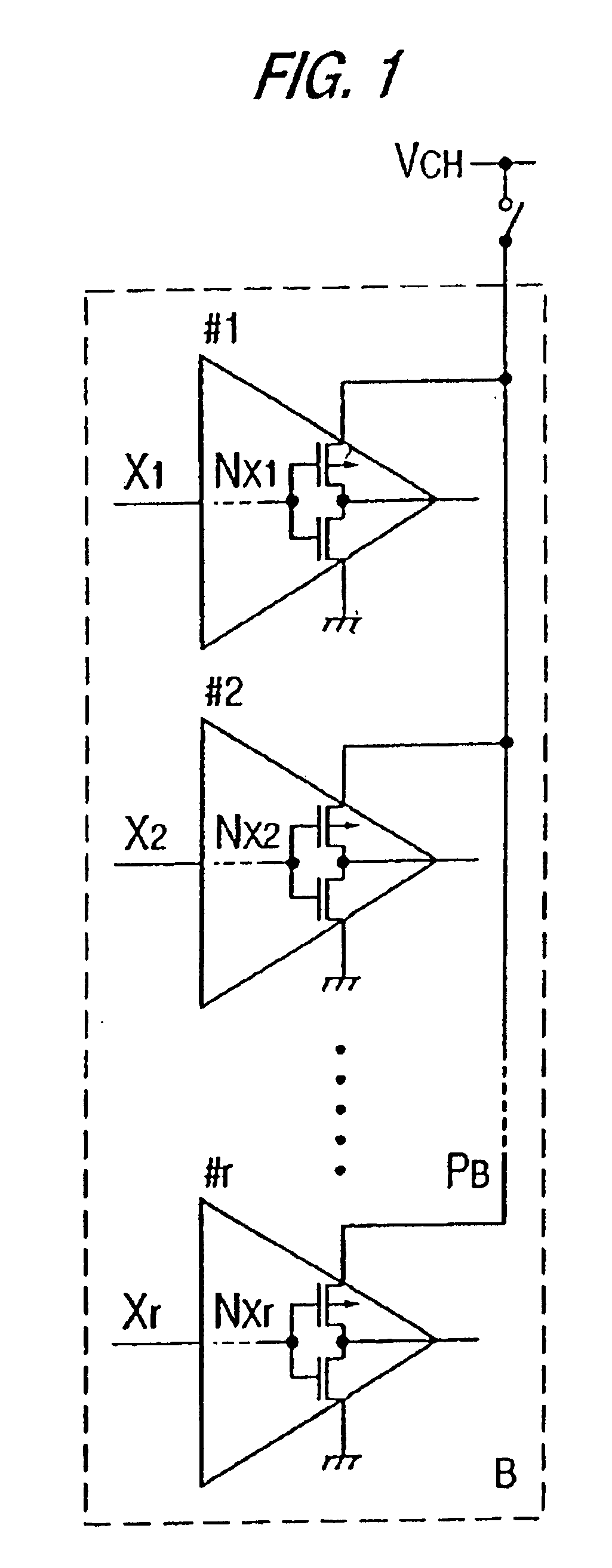

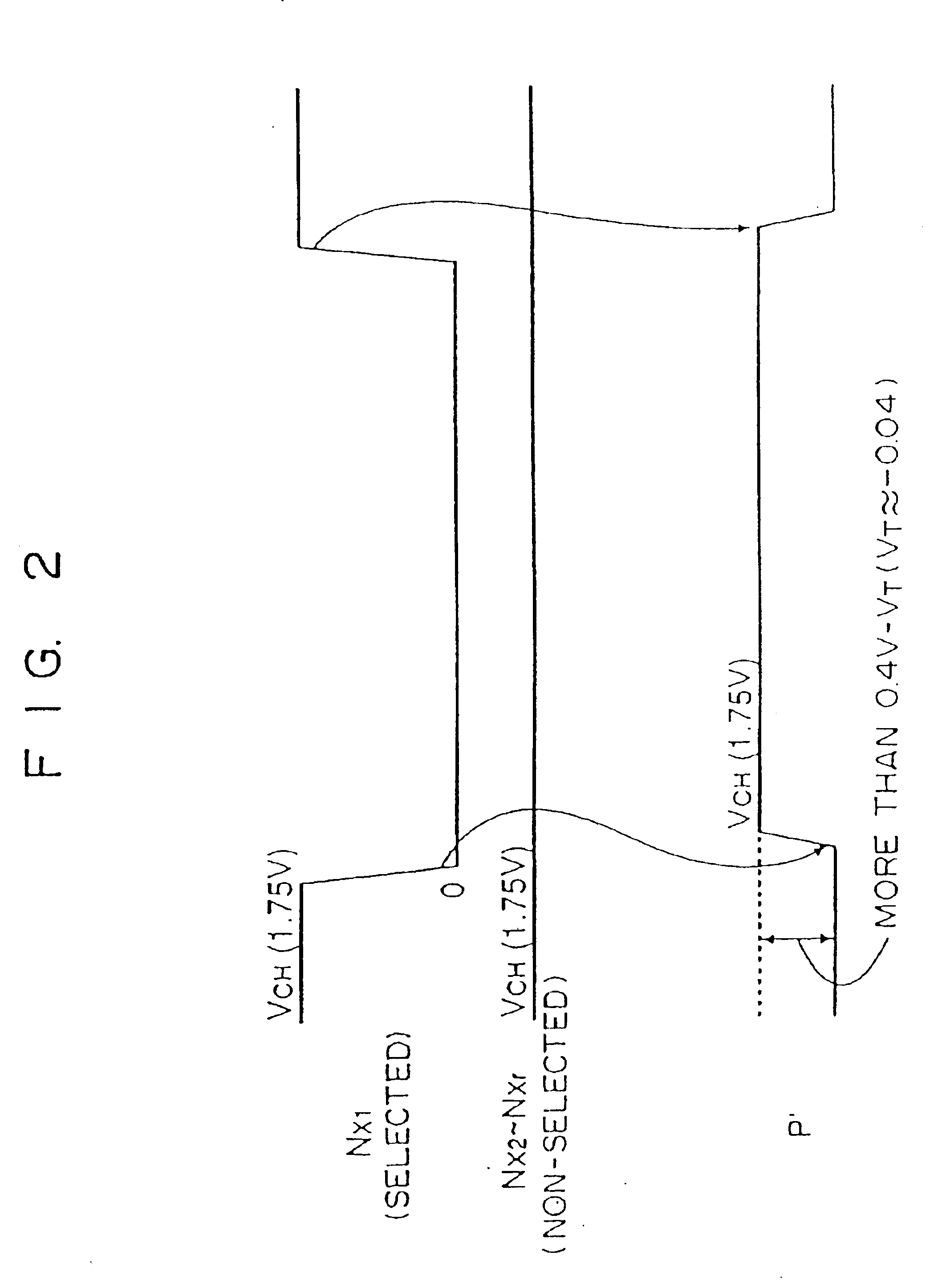

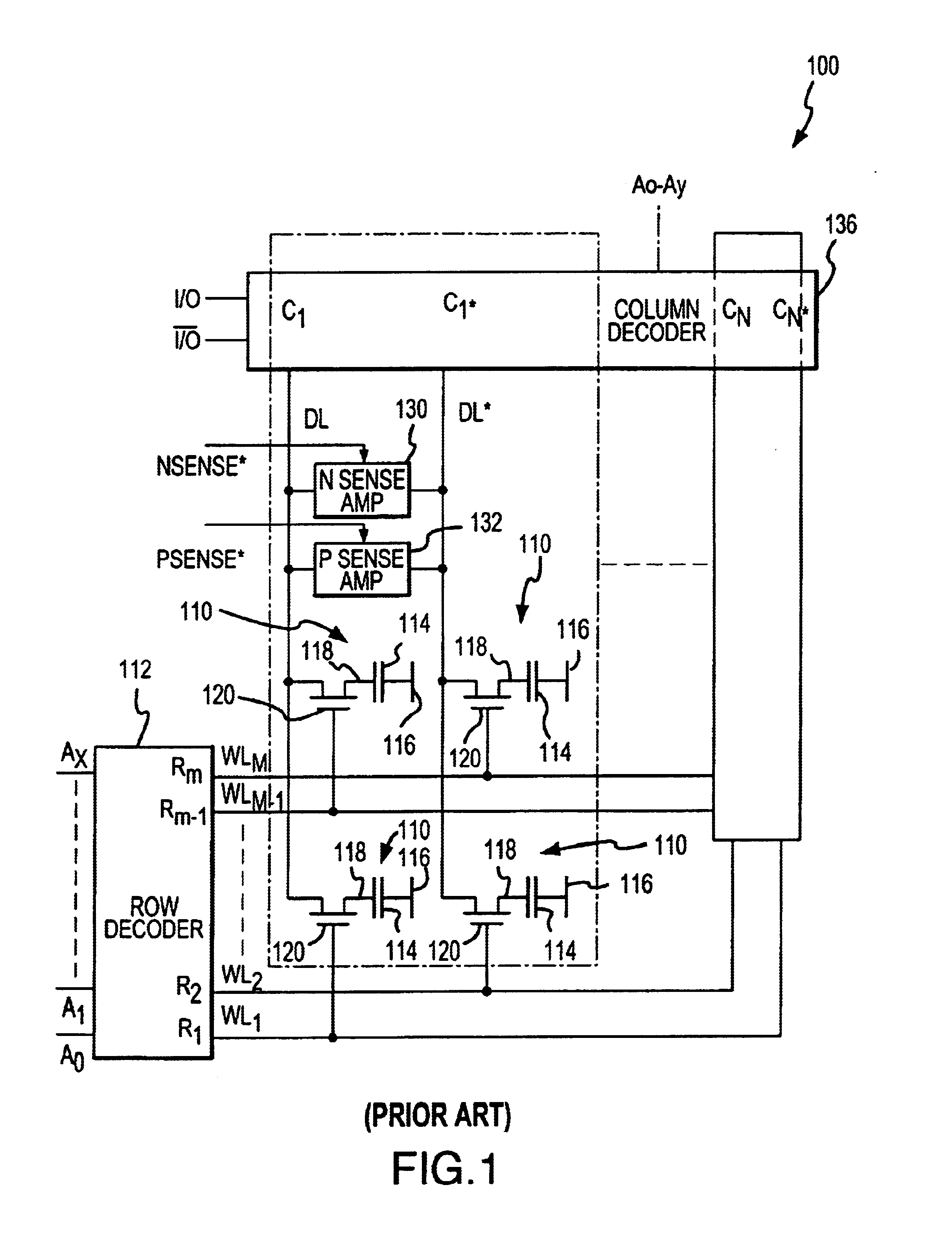

Negatively charged wordline for reduced subthreshold current

InactiveUS6865119B2Reduce leakage currentAvoid degradationDigital storageParallel computingSubthreshold conduction

An invention is provided for reducing subthreshold current in memory core cells. A memory array having a plurality of memory core cells is provided. Each memory core cell in the memory array is selectable using a word line. A selected word line addressing a particular memory core cell is charged to a positive voltage. In addition, unselected wordlines of the memory array are charged to a negative voltage. In this manner, subthreshold current associated with unselected memory core cells is reduced.

Owner:ARM INC

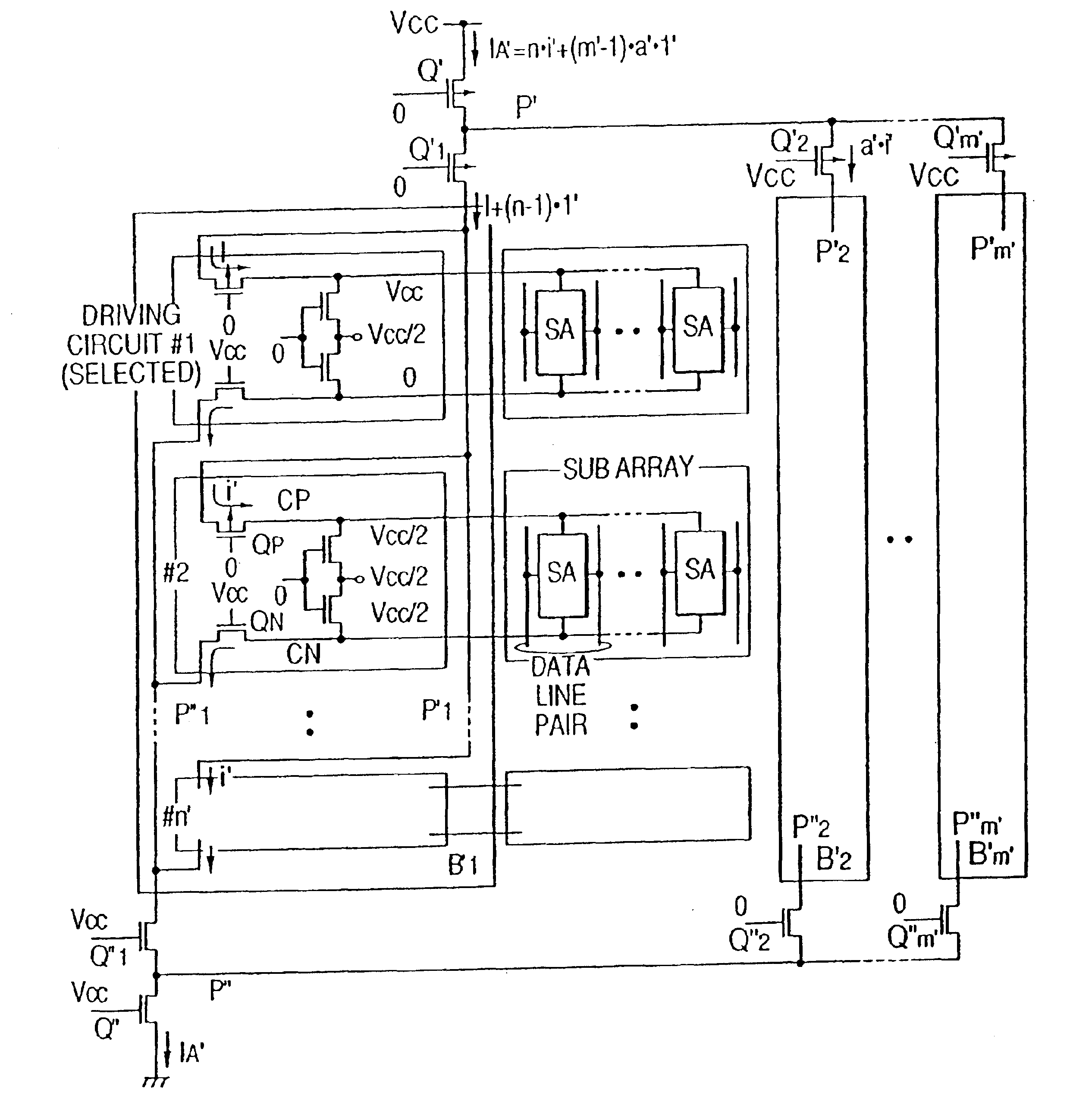

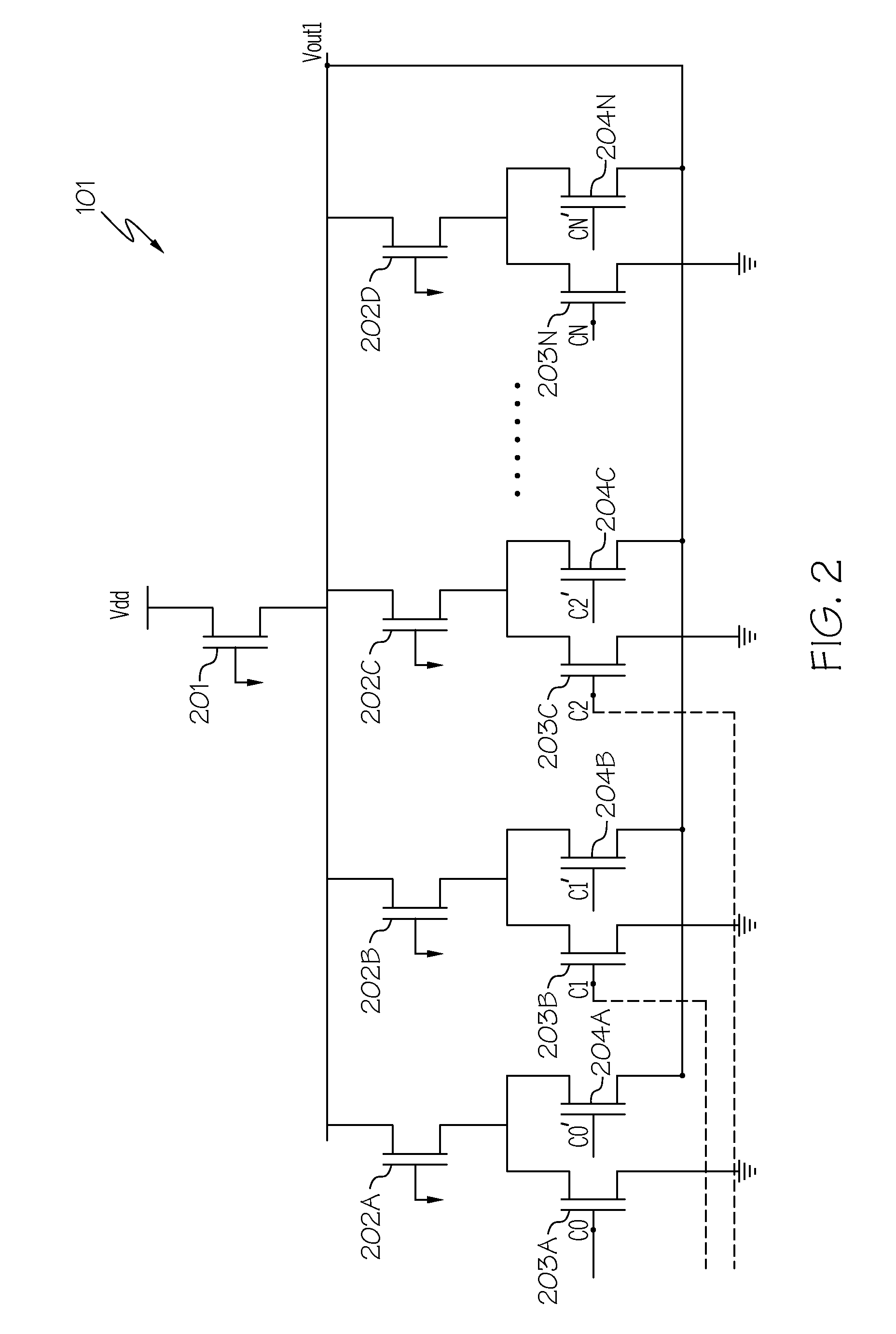

Semiconductor integrated circuits with power reduction mechanism

InactiveUS6838901B2Total current dropReduce leakage currentPower reduction by control/clock signalSemiconductor/solid-state device manufacturingEngineeringDrain current

Power dissipation of a semiconductor integrated circuit chip is reduced when it is operated at an operating voltage of 2.5 V or below. A switching element is provided in each circuit block within the chip. Constants of the switching element are set so that leakage current in each switching element in their off-state is smaller than the subthreshold current of MOS transistors within the corresponding circuit block. Active current is supplied to active circuit blocks, while switching elements of non-active circuit blocks are turned off. Thus, dissipation currents of non-active circuit blocks are limited to leakage current value of corresponding switching elements. Thus, the sum of dissipation currents of non-active circuit blocks is made smaller than the active current in the active circuit blocks. As a result, power dissipation in the semiconductor integrated circuit chip can be reduced even in the active state.

Owner:PS4 LUXCO SARL

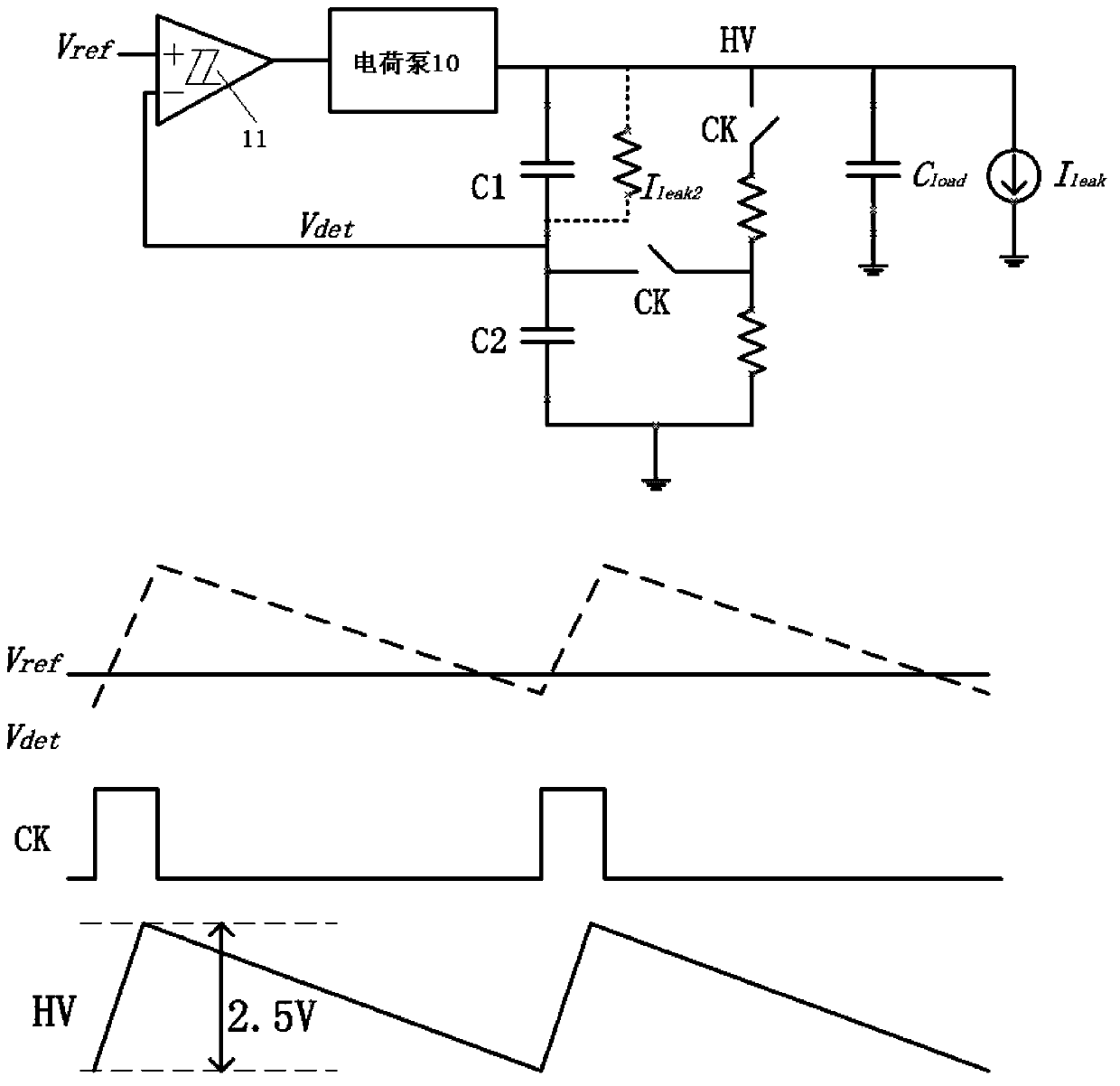

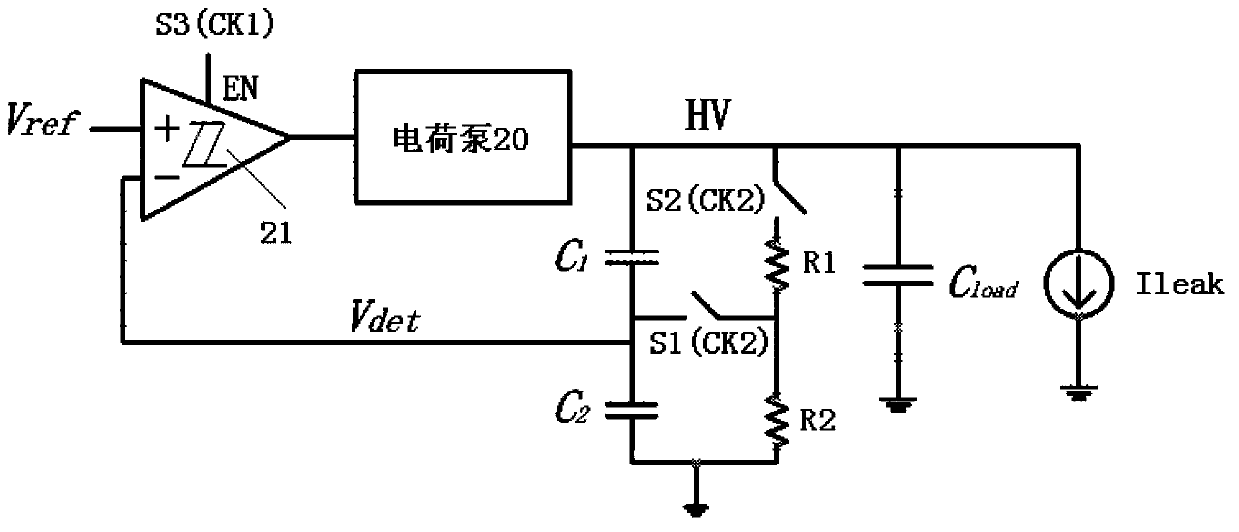

Low power consumption voltage regulator circuit

ActiveCN103389771AImprove efficiencyReduce power consumptionElectric variable regulationCapacitanceWork cycle

The invention discloses a low power consumption voltage regulator circuit, which comprises a charge pump, a comparator, a first capacitor, a second capacitor, a first resistor and a second resistor, wherein the comparator is connected with a third switch; the third switch is controlled by a first control signal generated by a subthreshold current oscillator to control the work cycle of the comparator; a resistor-capacitor network is connected with first and second switches; and the first and second switches are controlled by a second control signal generated by the subthreshold current oscillator to control the refresh cycle of a resistor voltage divider to a capacitor voltage divider. By the low power consumption voltage regulator circuit, a detection voltage error in the capacitor voltage divider caused by electric leakage can be avoided, so that the charge pump can normally work to meet the requirement on voltage; and moreover, the highest output voltage of the charge pump is limited to be 2.7V, so that a defect that high voltage resistant devices are required in the prior art is overcome, the high voltage output range is reduced, the efficiency of the charge pump is improved and the power consumption is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

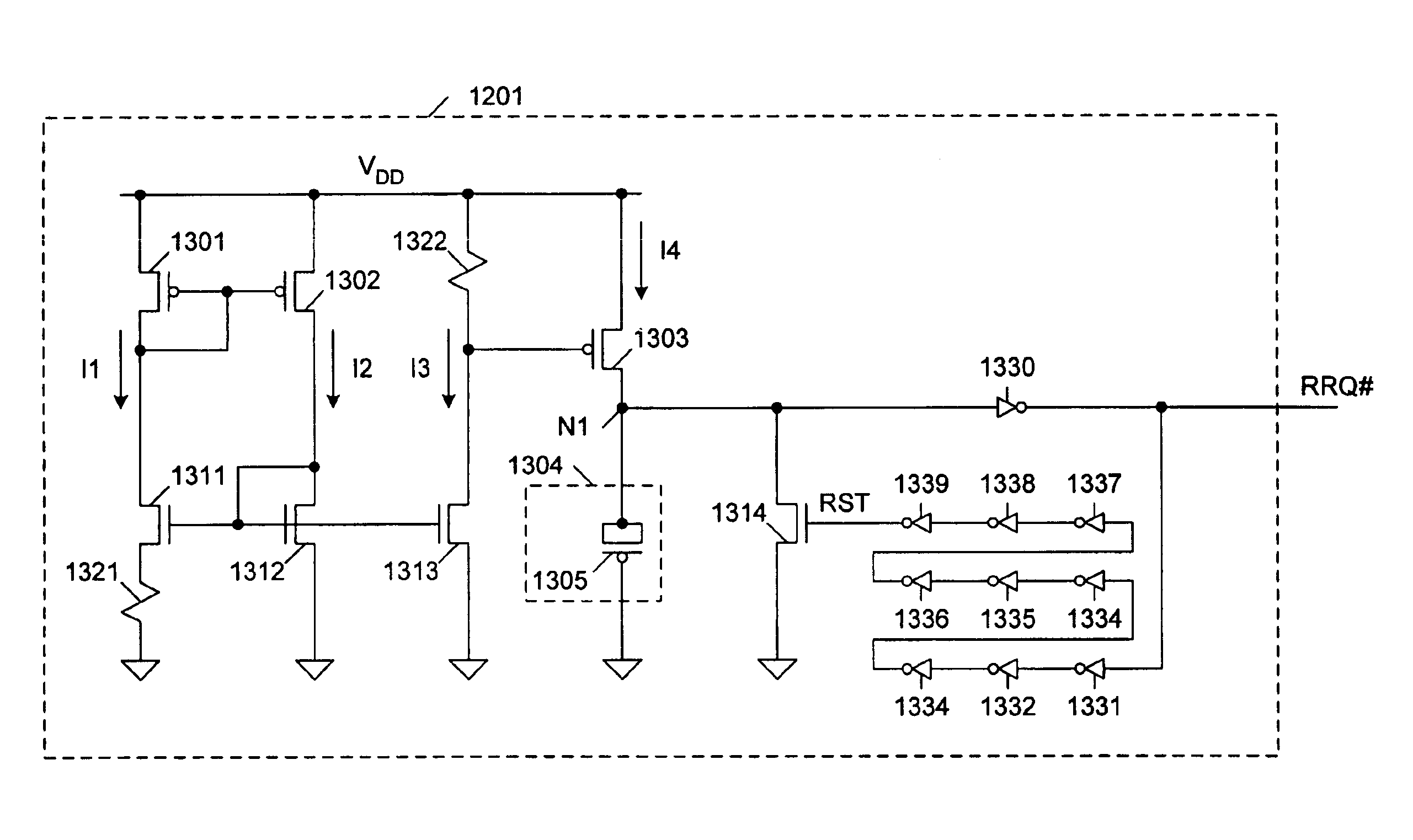

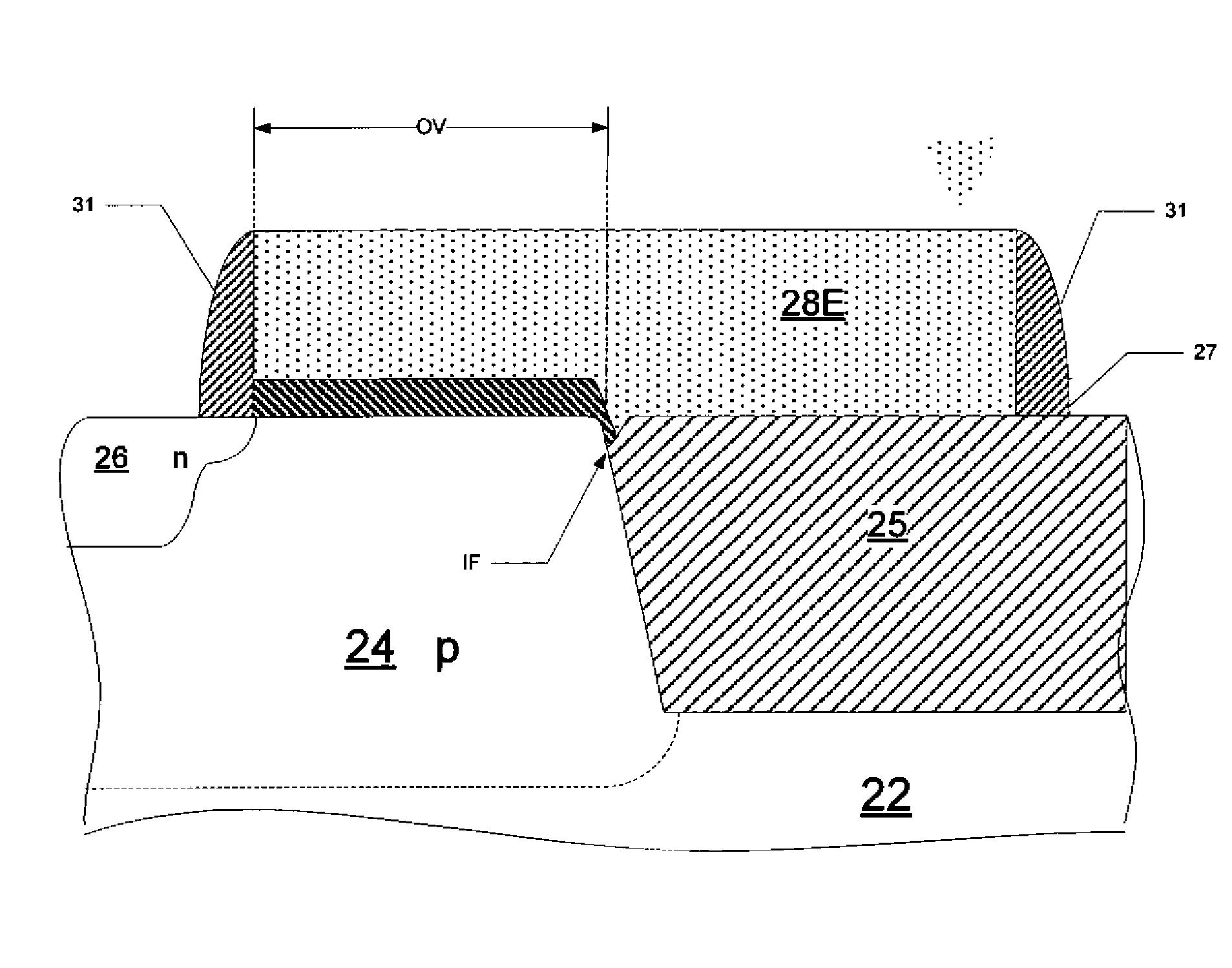

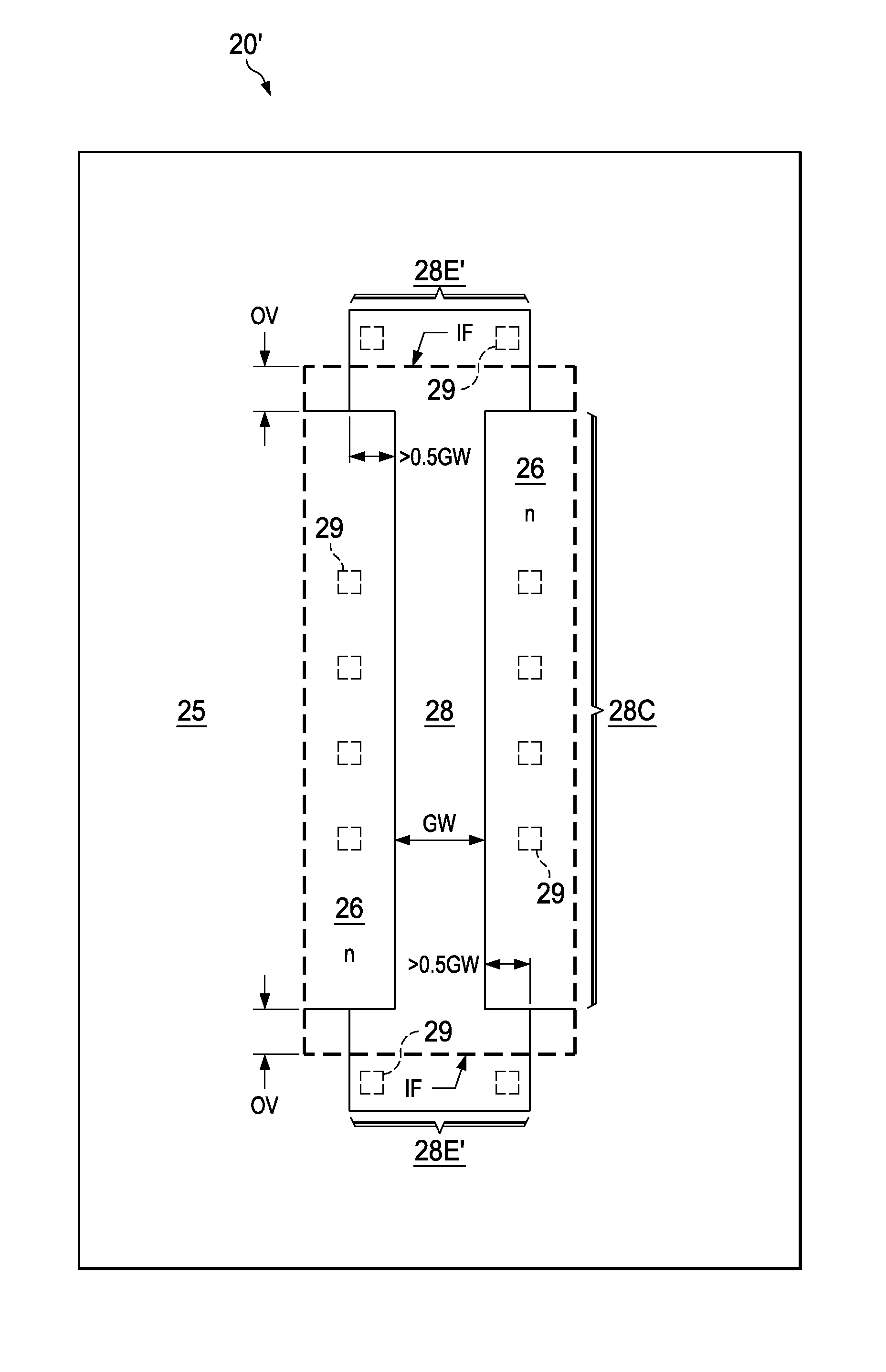

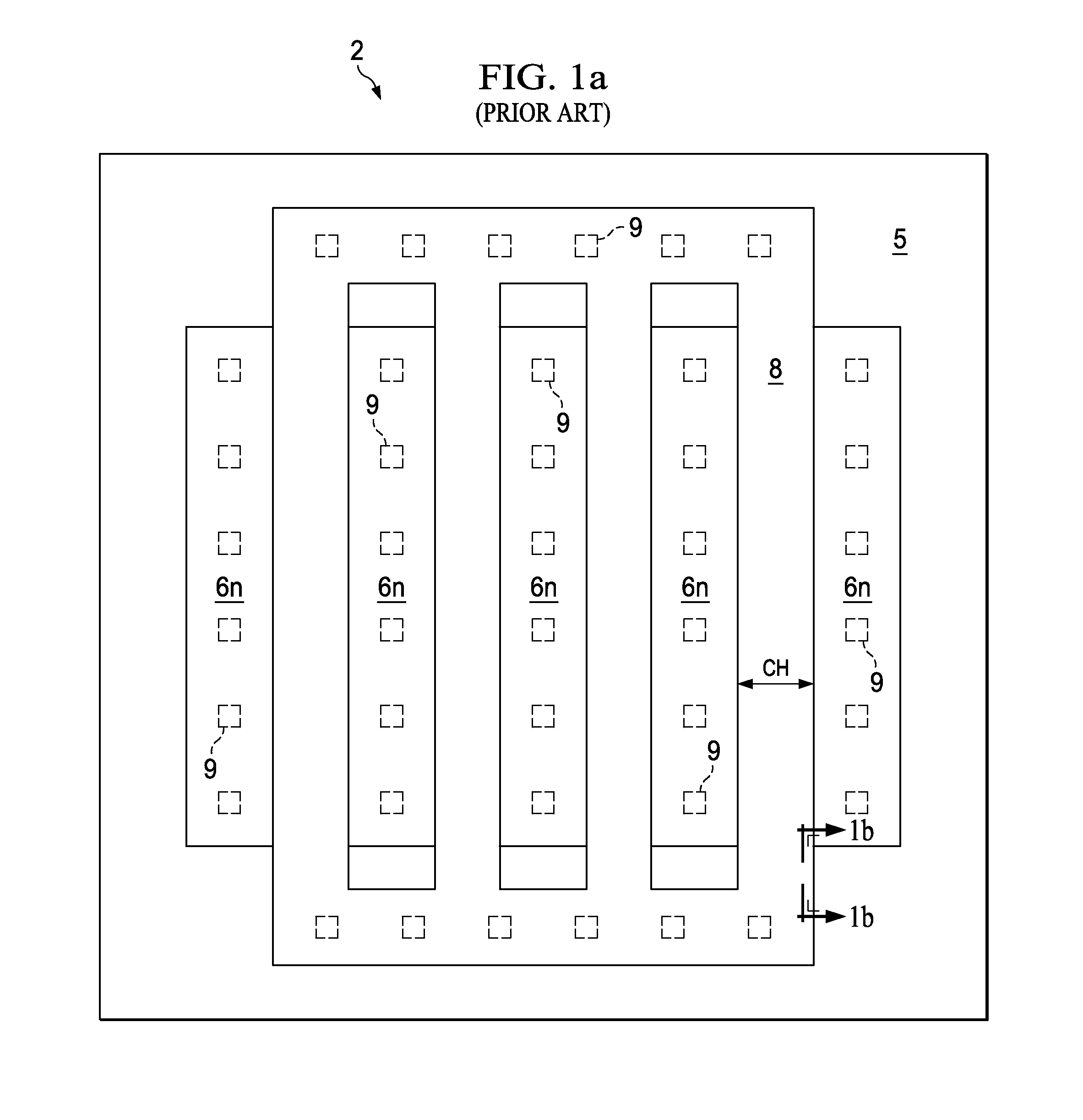

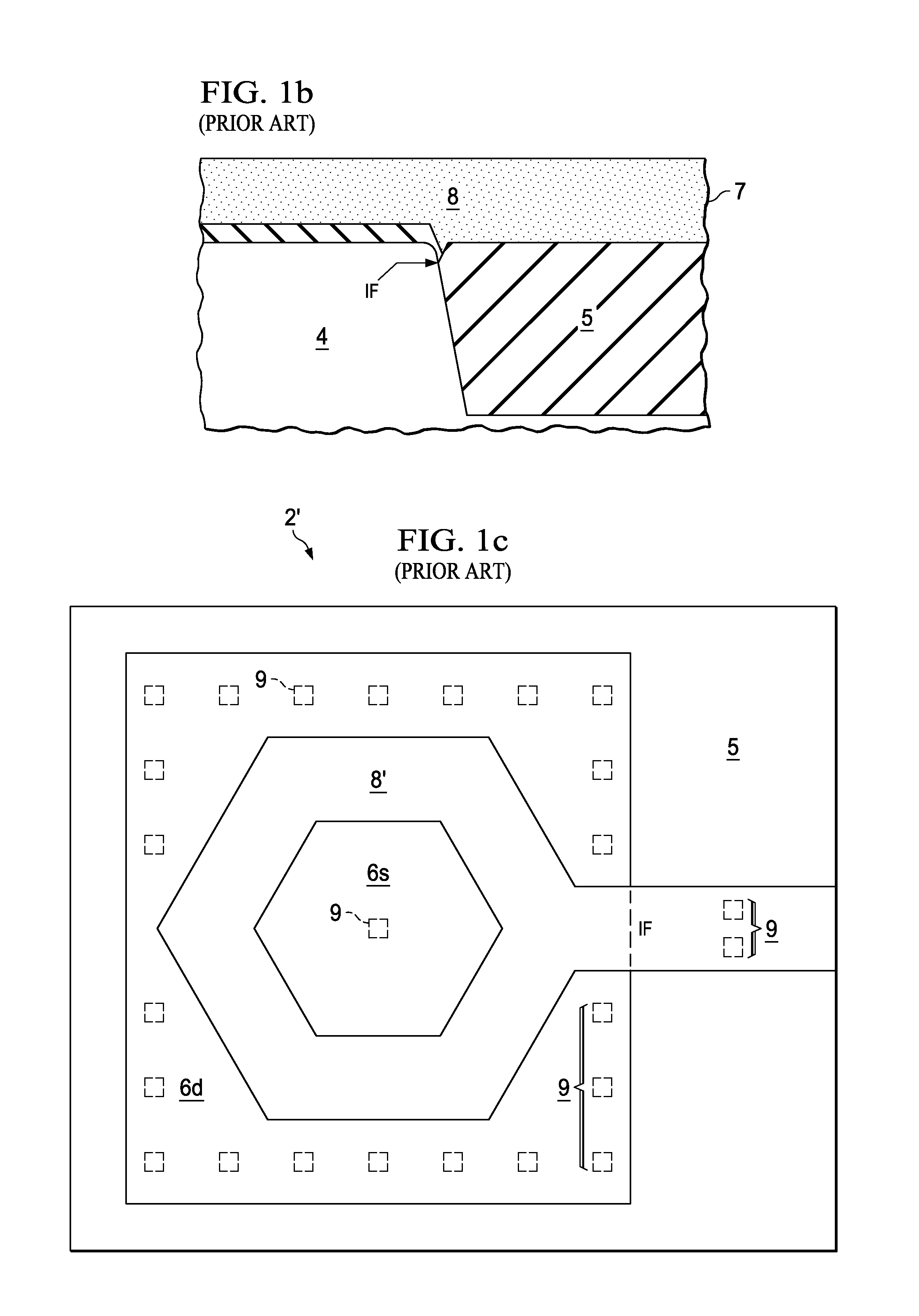

I-shaped gate electrode for improved sub-threshold mosfet performance

InactiveUS20140103440A1Reduce conductionReduce electrical conductivityTransistorSemiconductor/solid-state device manufacturingMOSFETSub threshold

Metal-oxide-semiconductor (MOS) transistors with reduced subthreshold conduction, and methods of fabricating the same. Transistor gate structures are fabricated in these transistors of a shape and dimension as to overlap onto the active region from the interface between isolation dielectric structures and the transistor active areas. Minimum channel length conduction is therefore not available at the isolation-to-active interface, but rather the channel length along that interface is substantially lengthened, reducing off-state conduction.

Owner:TEXAS INSTR INC

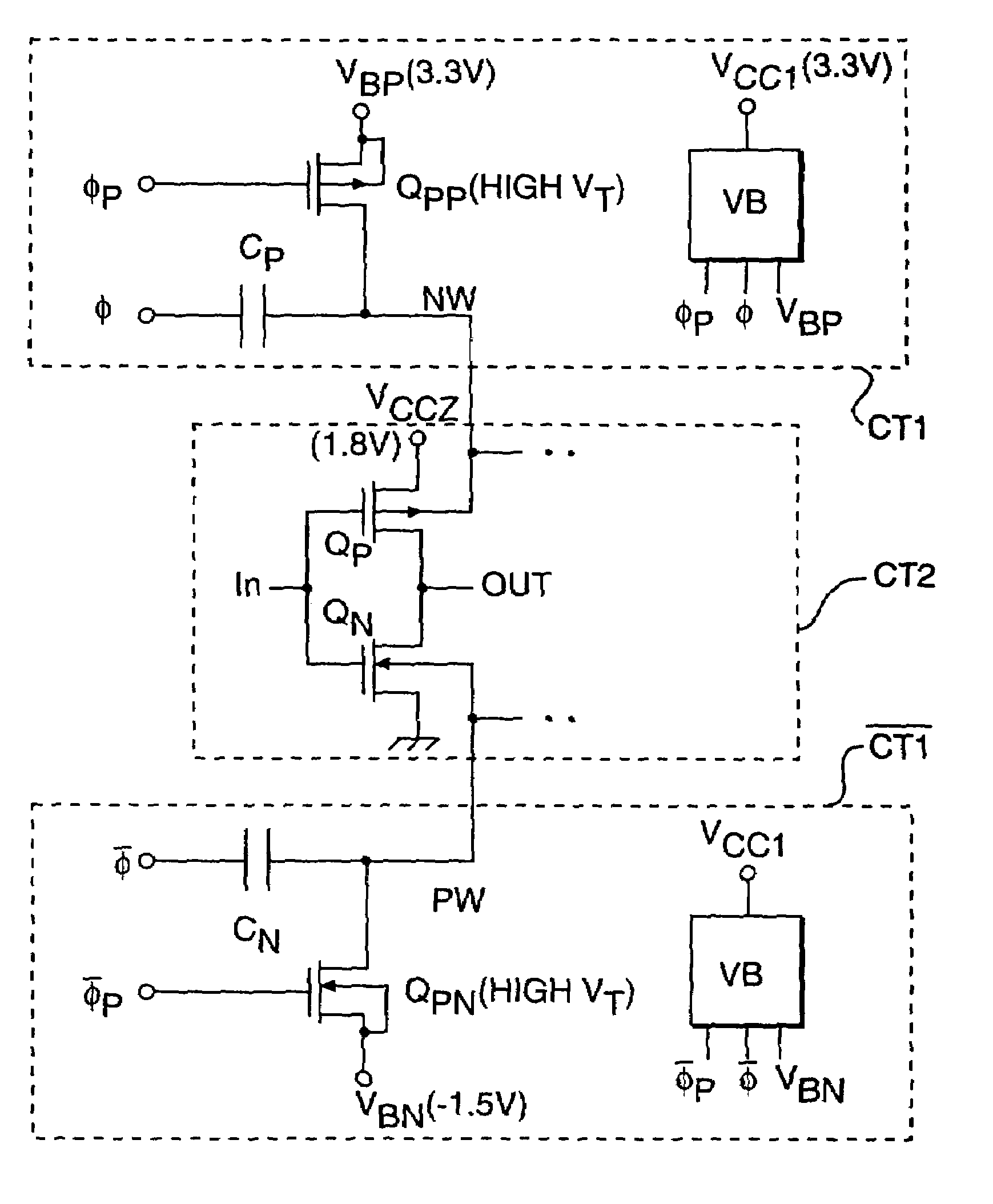

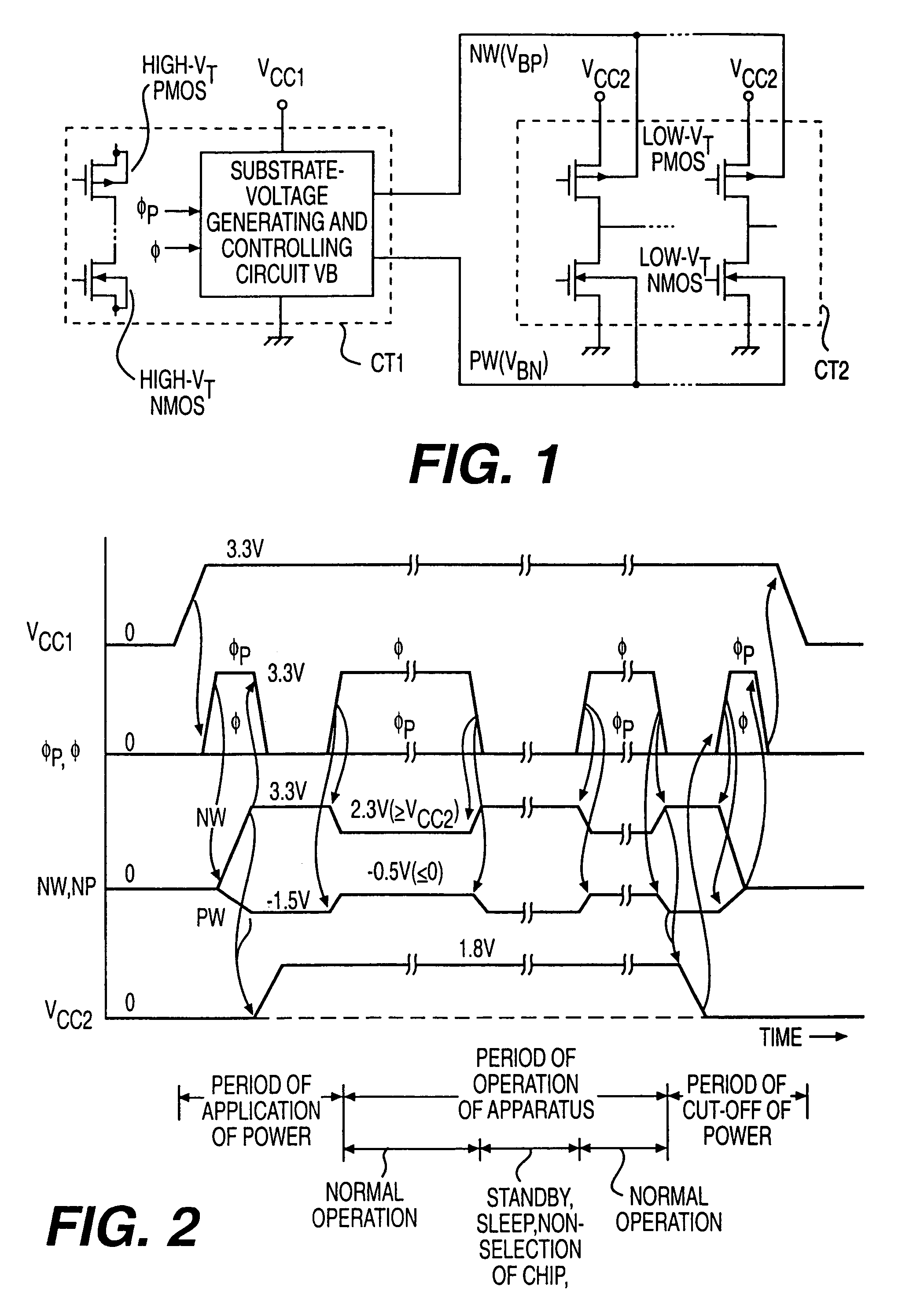

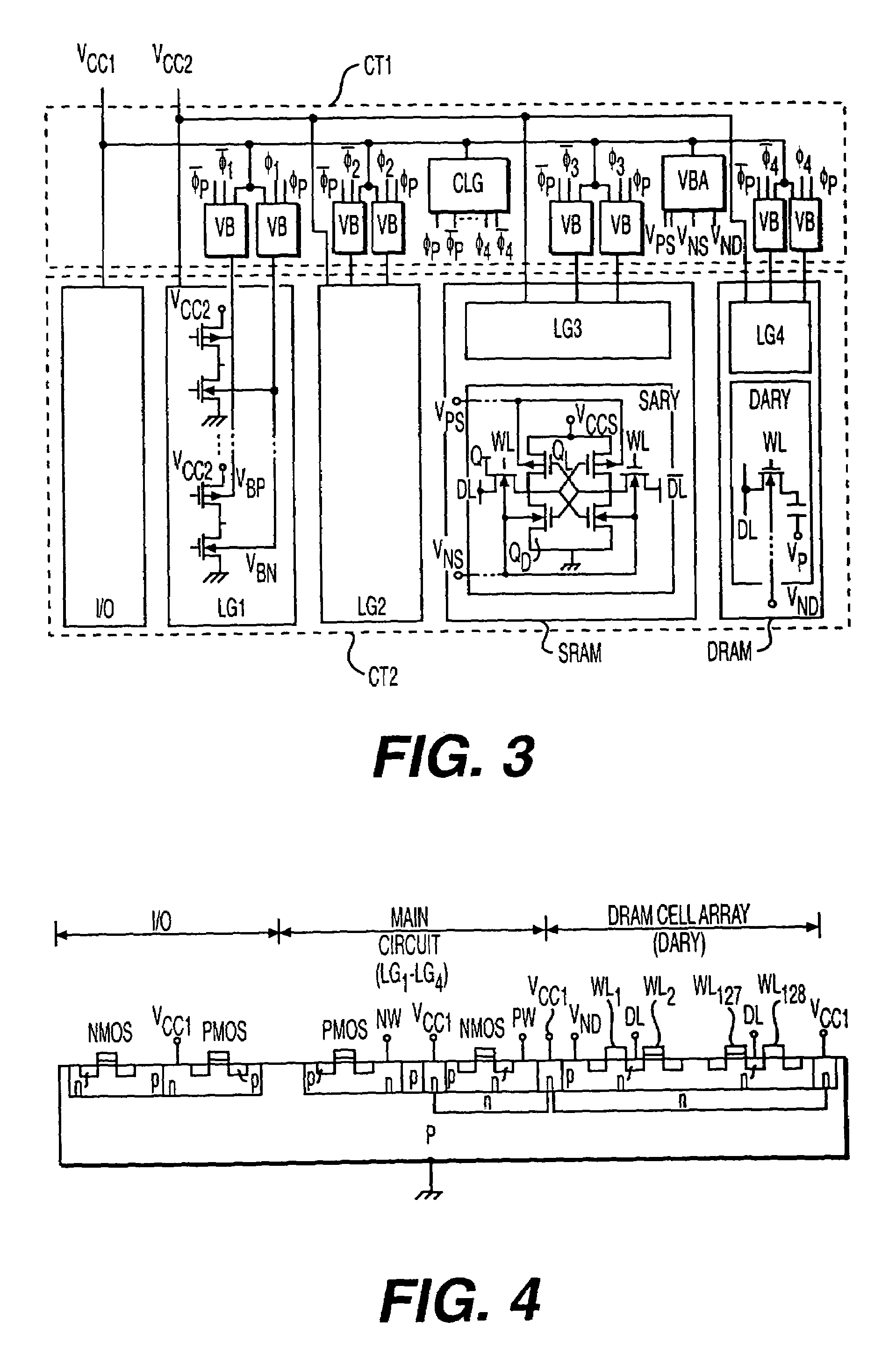

Semiconductor device

InactiveUS7176745B2Hinder latching-upPower reduction in field effect transistorsTransistorCMOSMOSFET

The well voltage of a CMOS circuit having low-threshold-voltage MOSFETs is controlled when the power supply is turned on, during normal operation, and when the supply voltage is cut off. The CMOS circuit can thus operate stably with lower power consumption, because latching-up is reduced when the supply voltage is applied to the CMOS circuit or when the supply voltage is cut off, and subthreshold current is decreased during normal operation.

Owner:RENESAS ELECTRONICS CORP

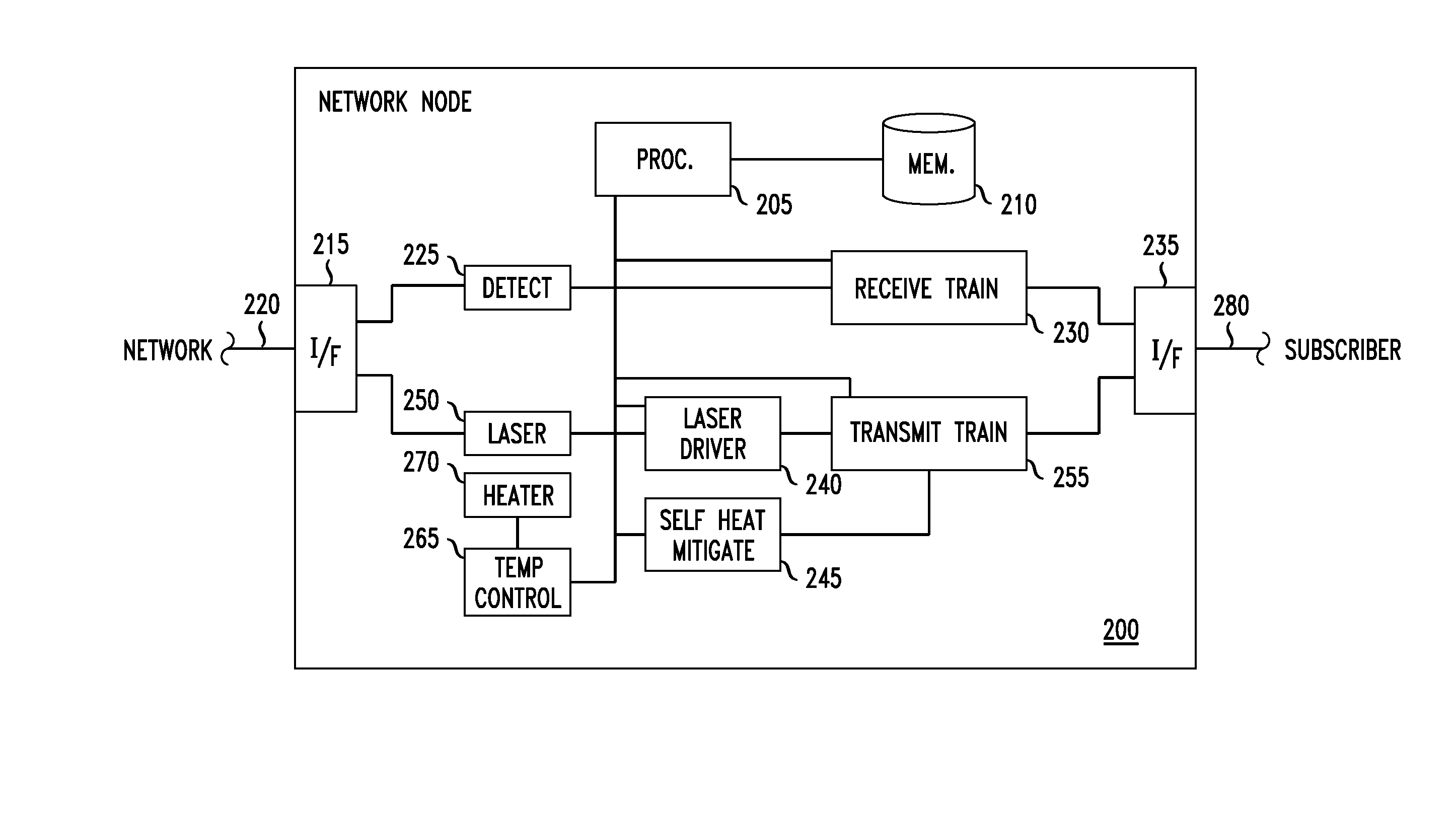

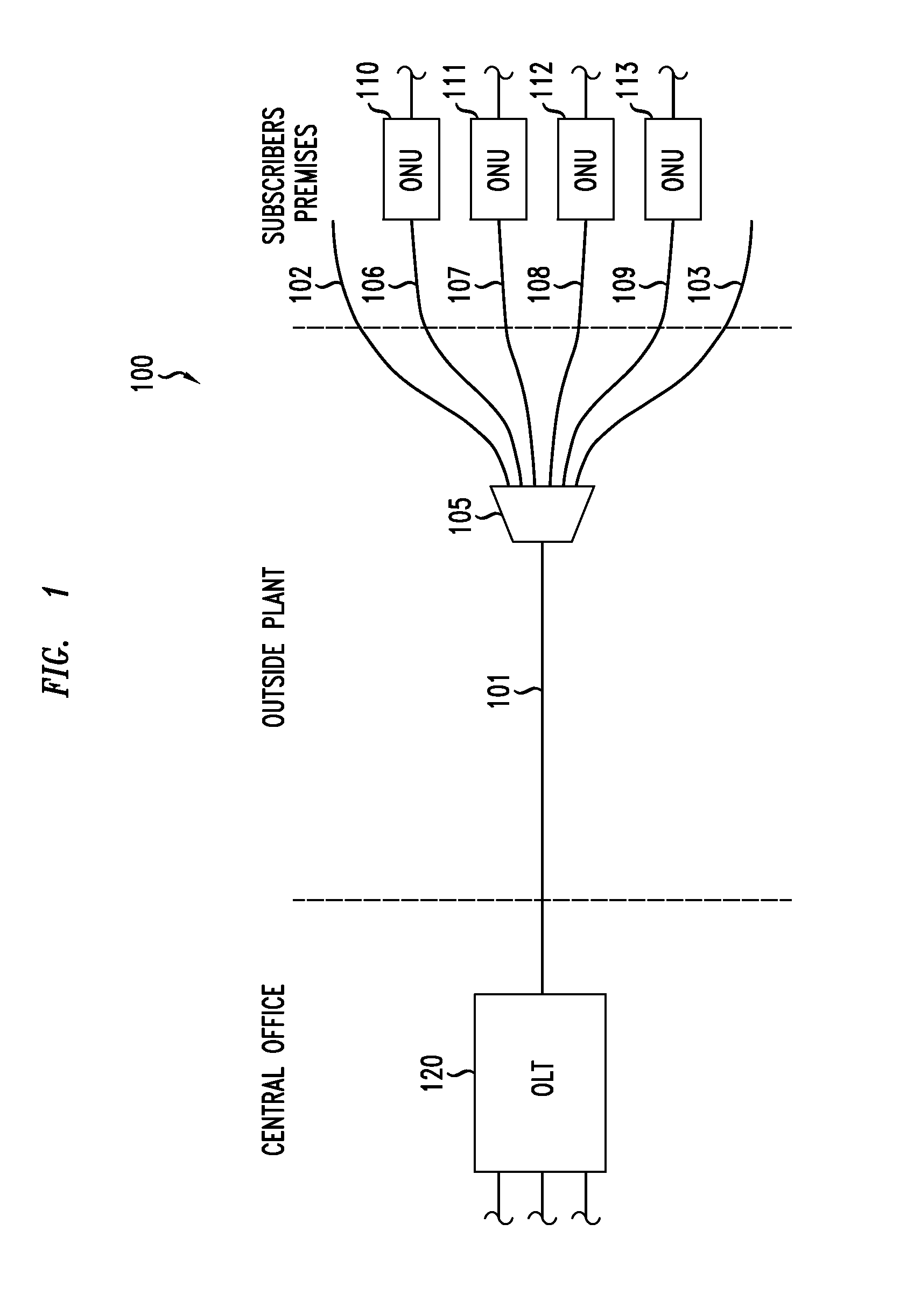

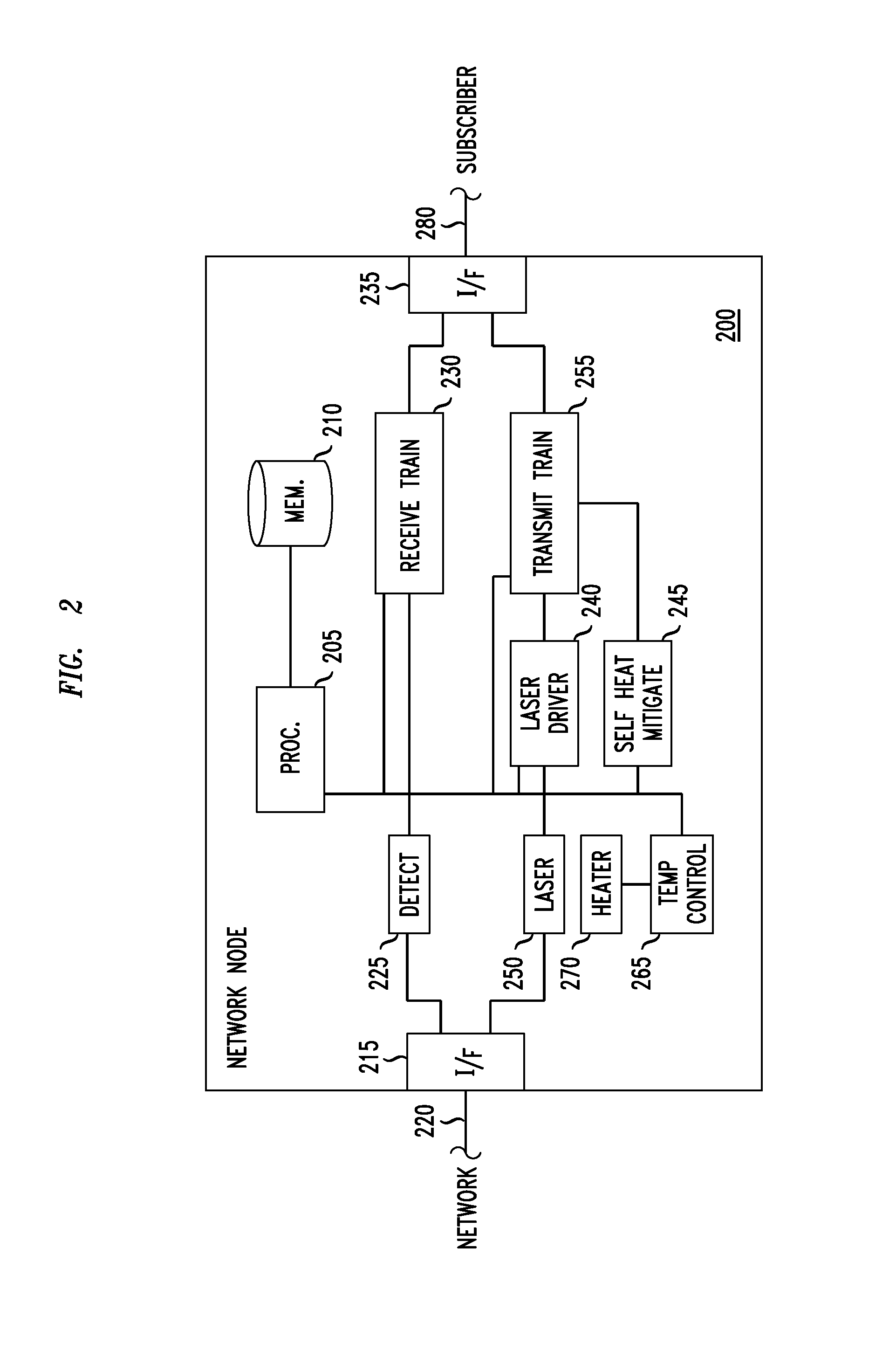

Method And Apparatus For Optical Transmission In A Communication Network

InactiveUS20140341593A1Reducing and alleviating detrimentalReducing and alleviating and undesirable effectElectromagnetic transmittersStar-type electromagnetic networksSub thresholdOptical data transmission

A manner of mitigating the self heating effect of a laser or other light source such as a laser in a network node of a communication network. A self-heating mitigation module is provided, the self-heating mitigation module includes one or both of a self-heating adjustment module to accelerate self heating at the beginning of a transmission and a sub-threshold lasing module that applies a sub-threshold current between transmissions. The self-heating adjustment module and the sub-threshold lasing module are preferable both used together and driven by a common signal, for example the burst_enable signal that facilitates transmission from the light source.

Owner:ALCATEL LUCENT SAS +1

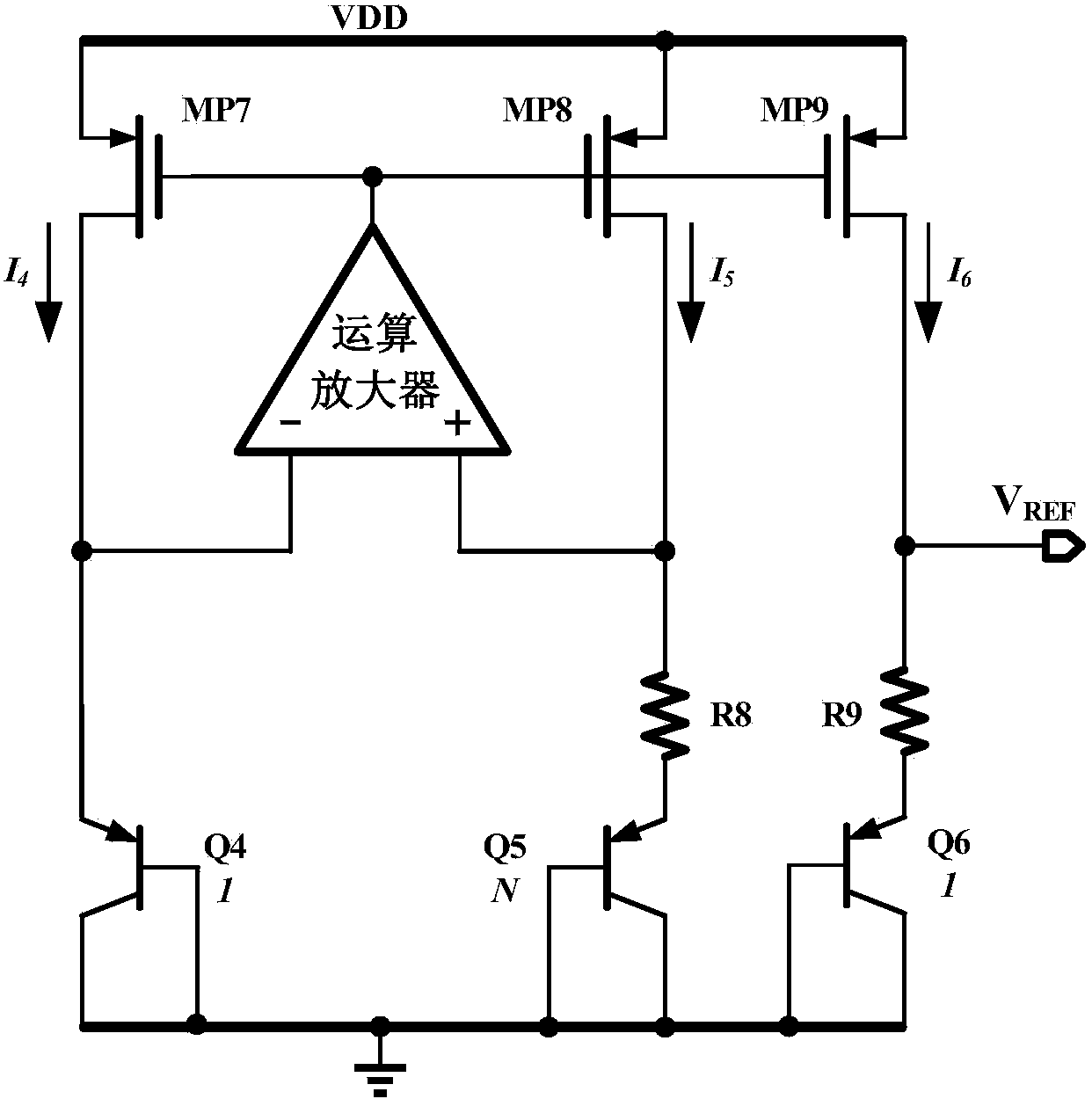

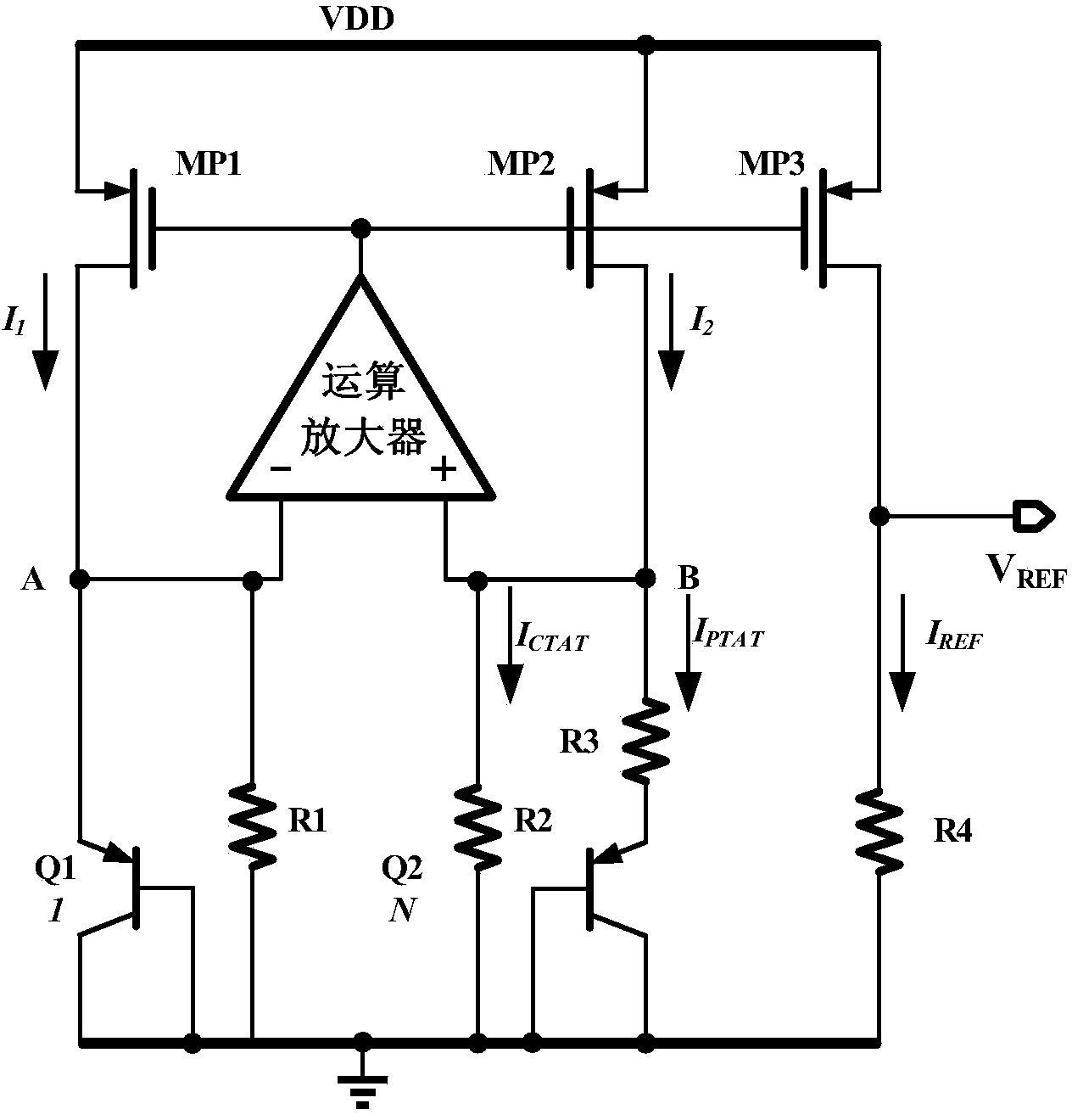

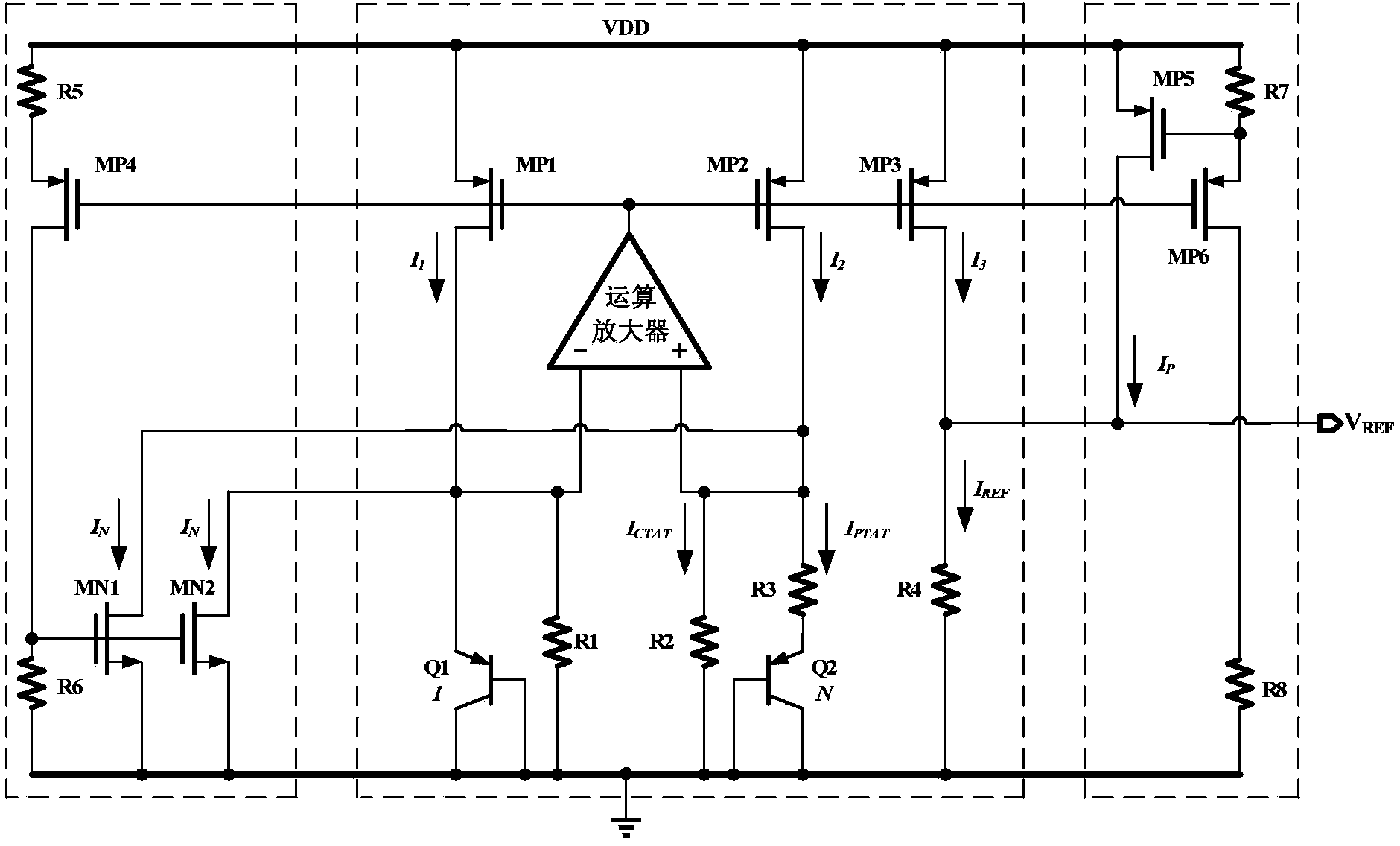

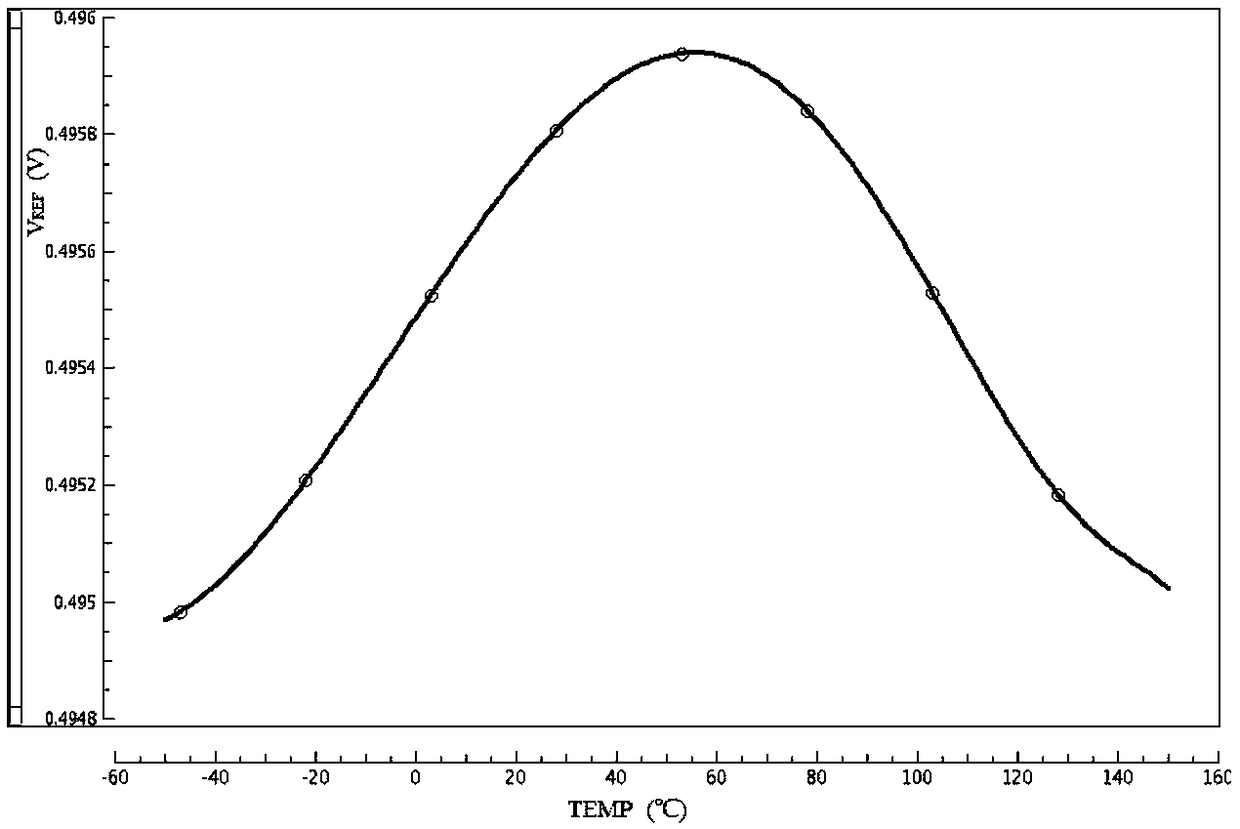

Current mode bandgap reference voltage source with subthreshold current compensation function

ActiveCN104035471ASimple structureFlexible designElectric variable regulationPower flowReference current

Disclosed is a current mode bandgap reference voltage source with a subthreshold current compensation function. On the basis of an existing bandgap reference core circuit, a first MOS (metal oxide semiconductor) transistor subthreshold current compensation circuit and a second MOS transistor subthreshold current compensation circuit are added, subthreshold current of an NMOS transistor and a PMOS transistor are compensated to reference current through the two subthreshold current compensation circuits, the index change relation of the subthreshold current is utilized to compensate nonlinearity of traditional reference current, output bandgap reference current is enabled to be compensated within a wide temperature range, output bandgap reference voltage and temperature variations slow down, and accordingly temperature coefficient of the reference voltage is lowered greatly.

Owner:SOUTHEAST UNIV

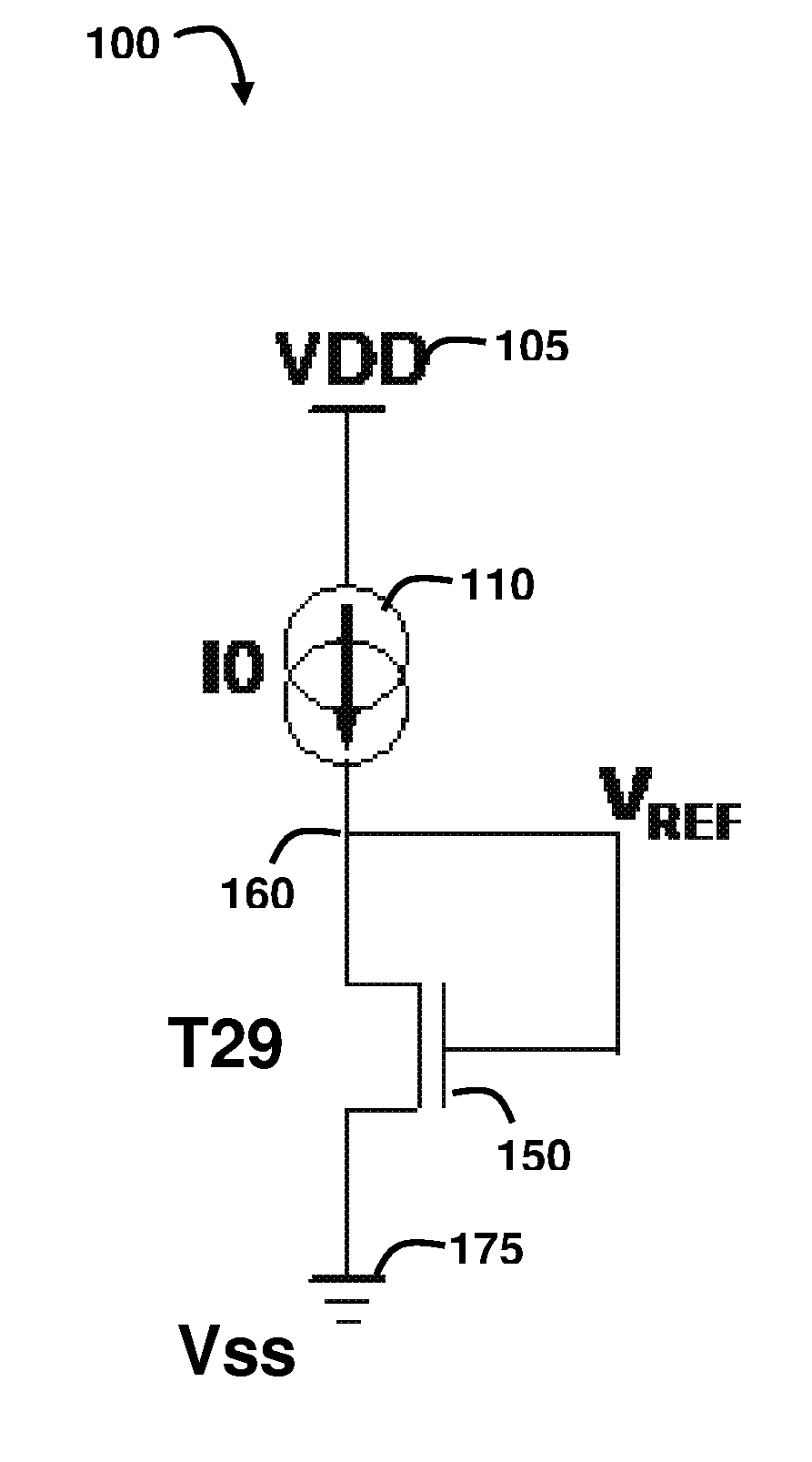

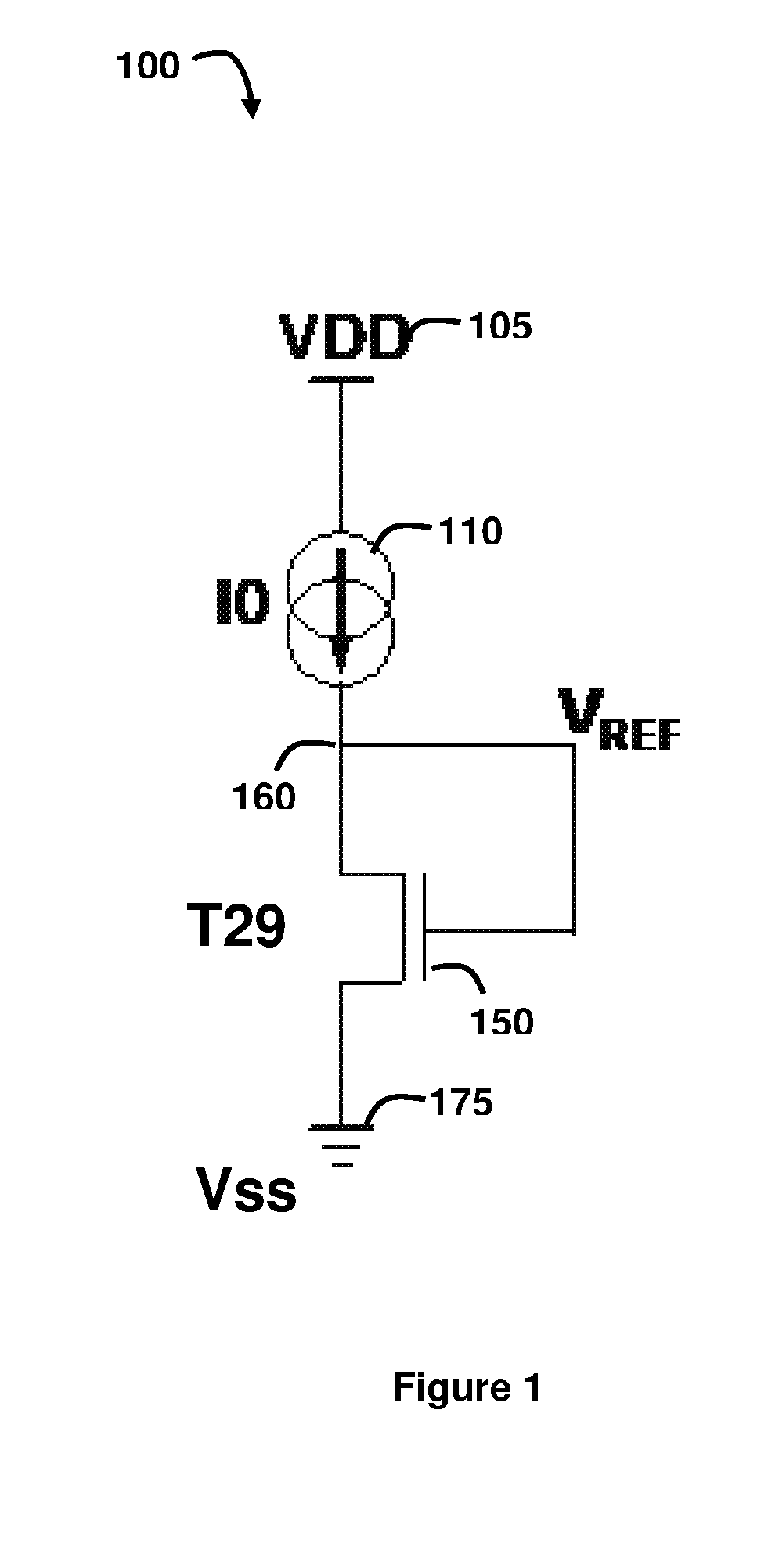

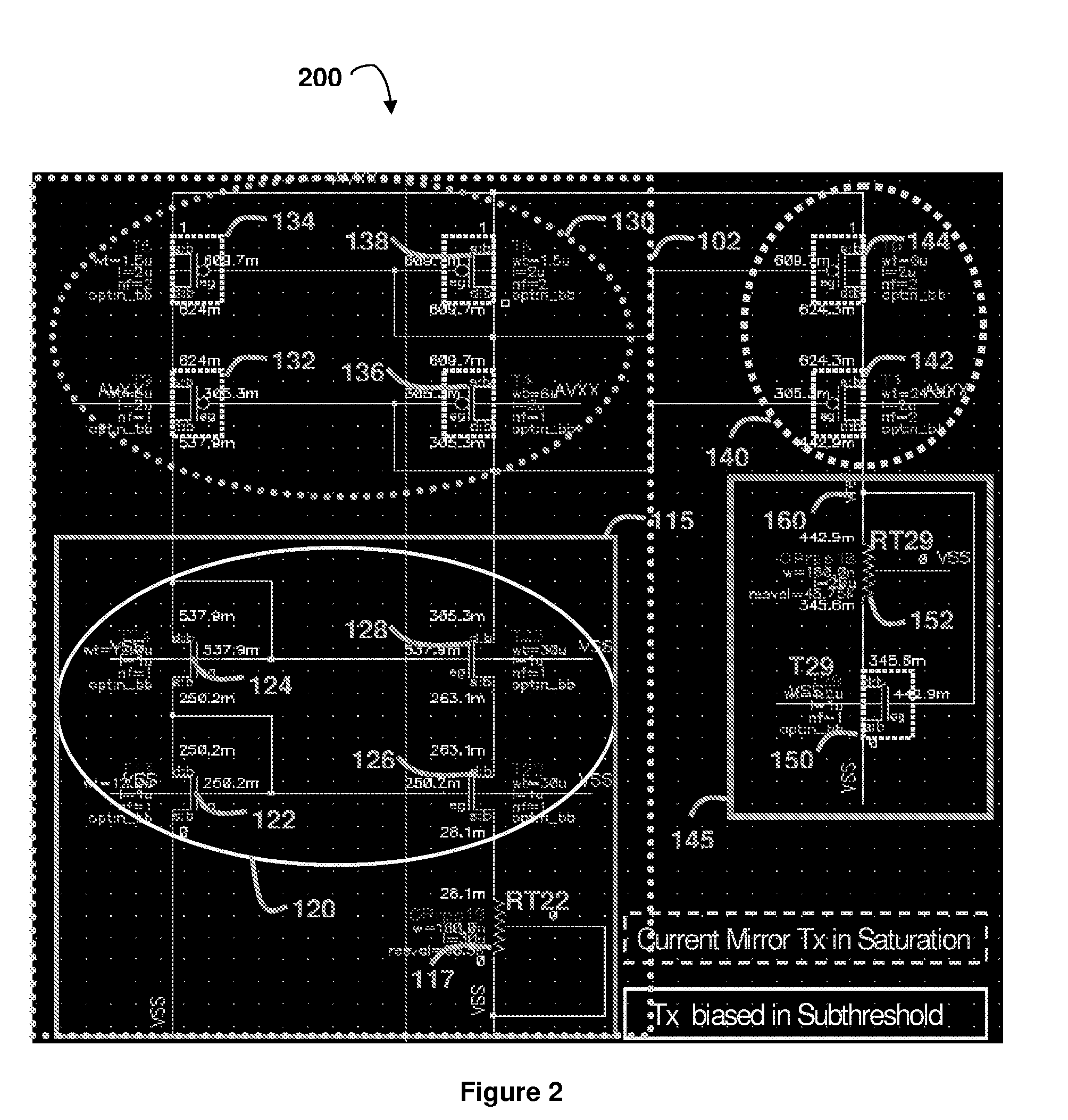

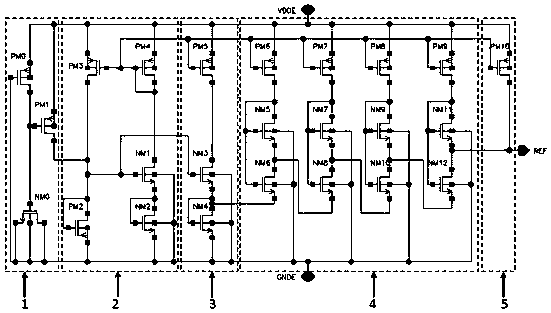

Low power CMOS voltage reference circuits

InactiveUS20080297229A1Electronic switchingPulse generation by opto-electronic devicesMOSFETLow voltage

A CMOS voltage reference circuit for a low voltage (1v), low power supply application is described. The circuit achieves a temperature coefficient of 31 ppm for a relatively large temperature range of −40 C to 125 C. A combination of subthreshold current characteristics and moderate inversion operation of MOSFET's are utilized in conjunction to achieve a fairly stable temperature independent output voltage reference (VREF) from the circuit.

Owner:IBM CORP

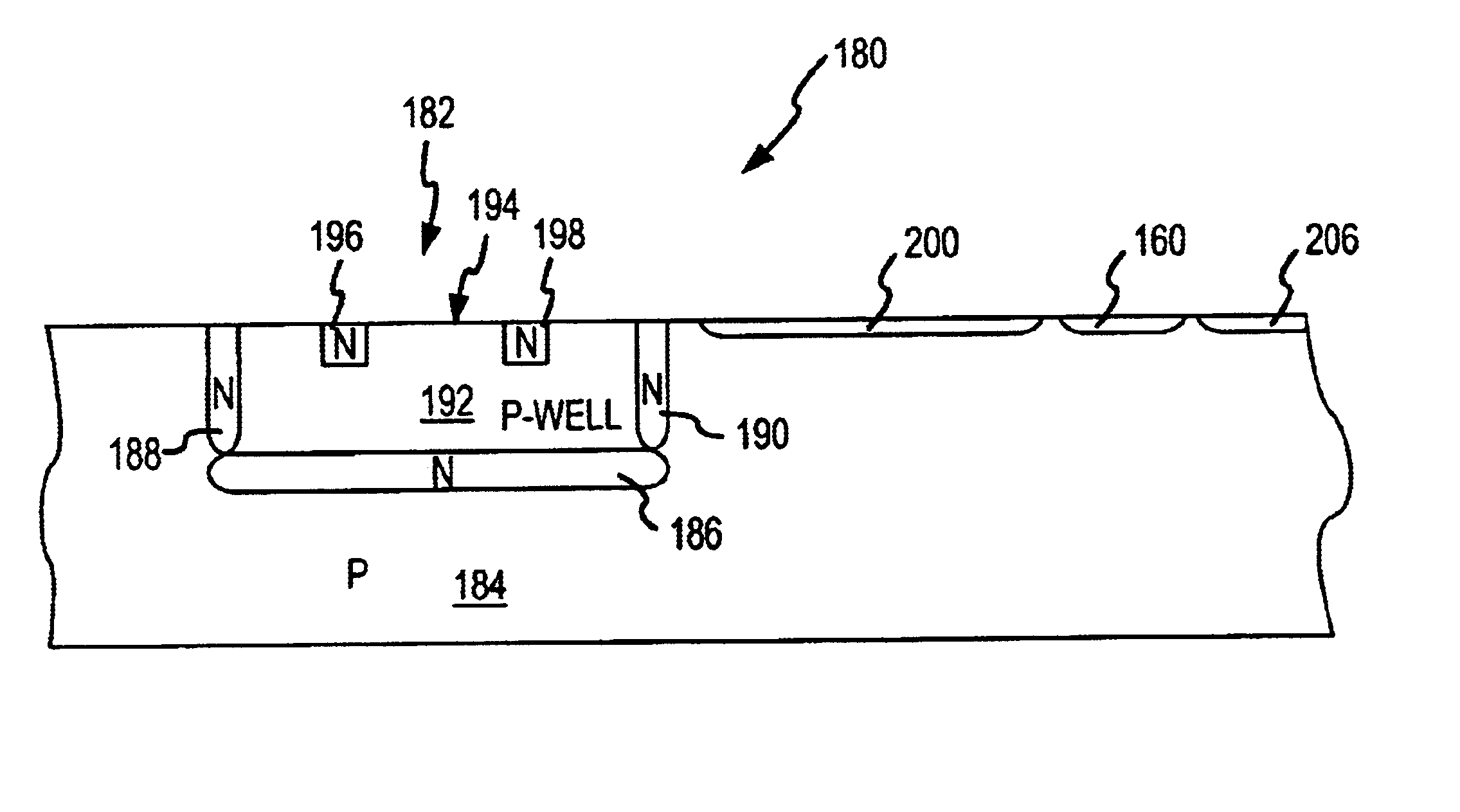

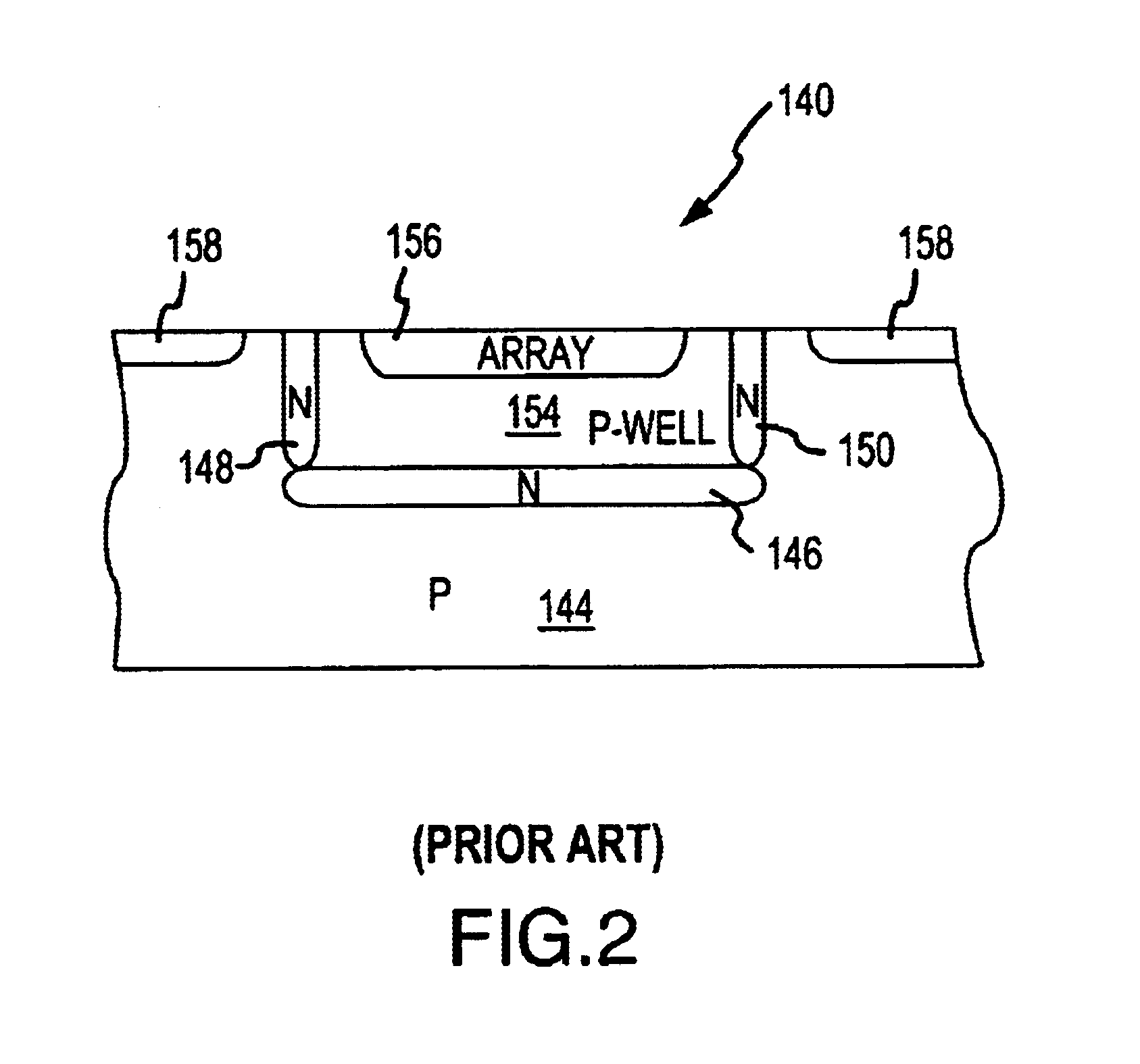

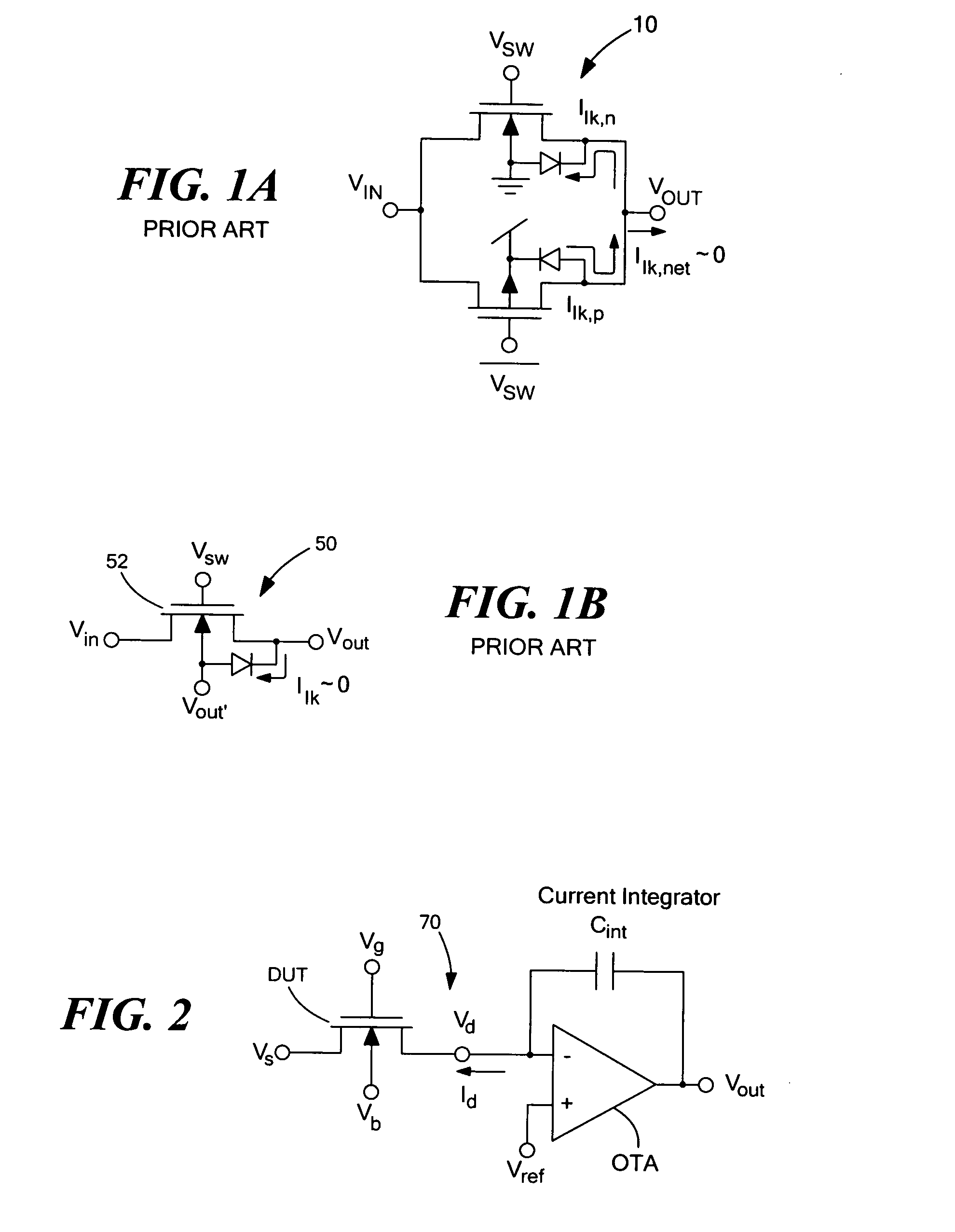

Method and circuit for reducing DRAM refresh power by reducing access transistor sub threshold leakage

InactiveUS6888769B2Lower refresh rateEasily able to provide good regulation of the positive voltageDigital storageElectricitySub threshold

The required refresh rate of a DRAM is reduced by biasing active digit lines to a slight positive voltage to reduce the sub threshold current leakage of access transistors in memory cells that are not being accessed. The slight positive voltage is provided by a voltage regulator circuit using one or more bipolar transistors fabricated in a well that electrically isolates the bipolar transistors from the remainder of the substrate. The voltage provided by the voltage regulator is preferably coupled to the access transistors by powering each of the n-sense amplifiers in the DRAM with the voltage from the voltage regulator.

Owner:NAN YA TECH

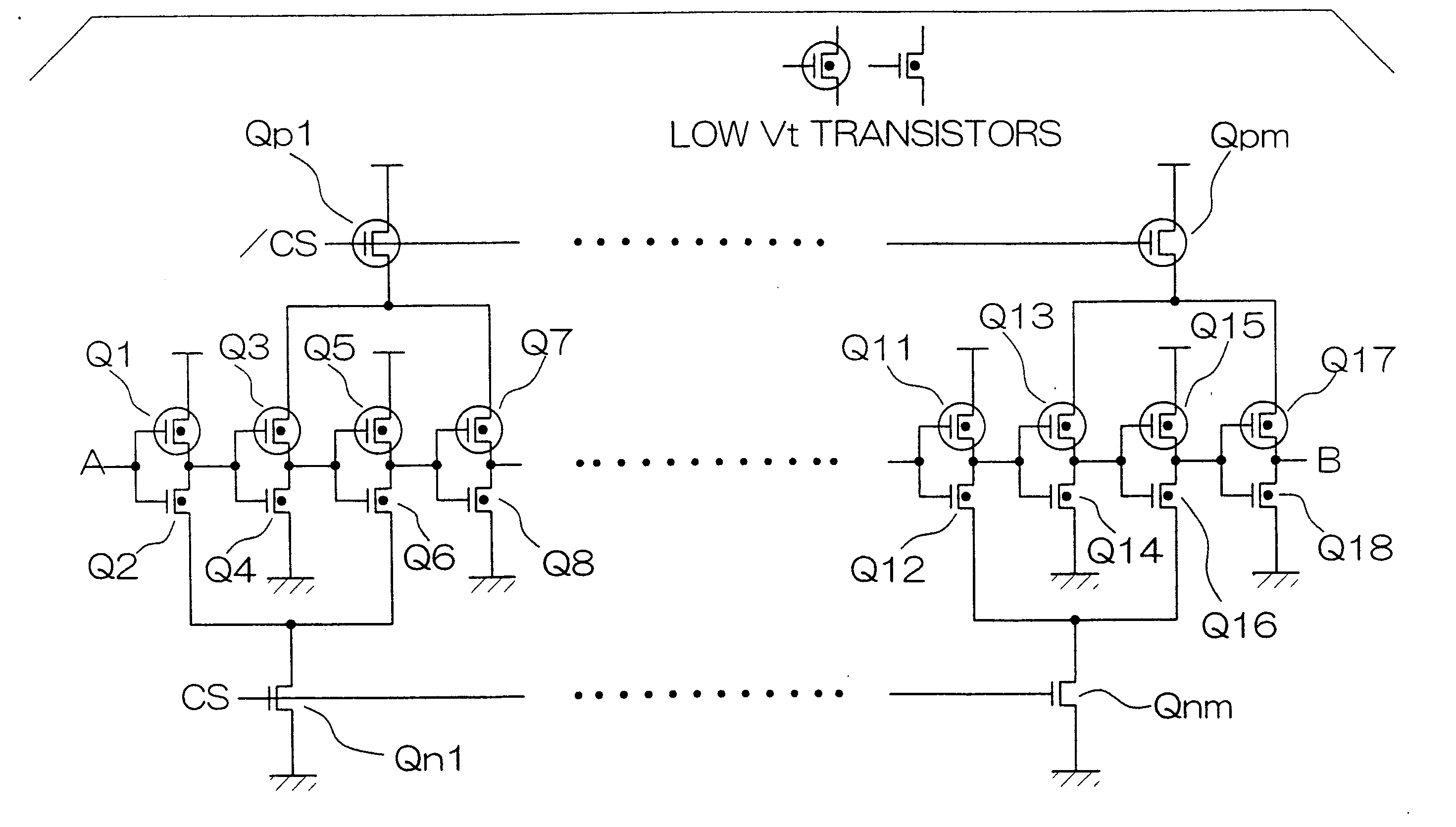

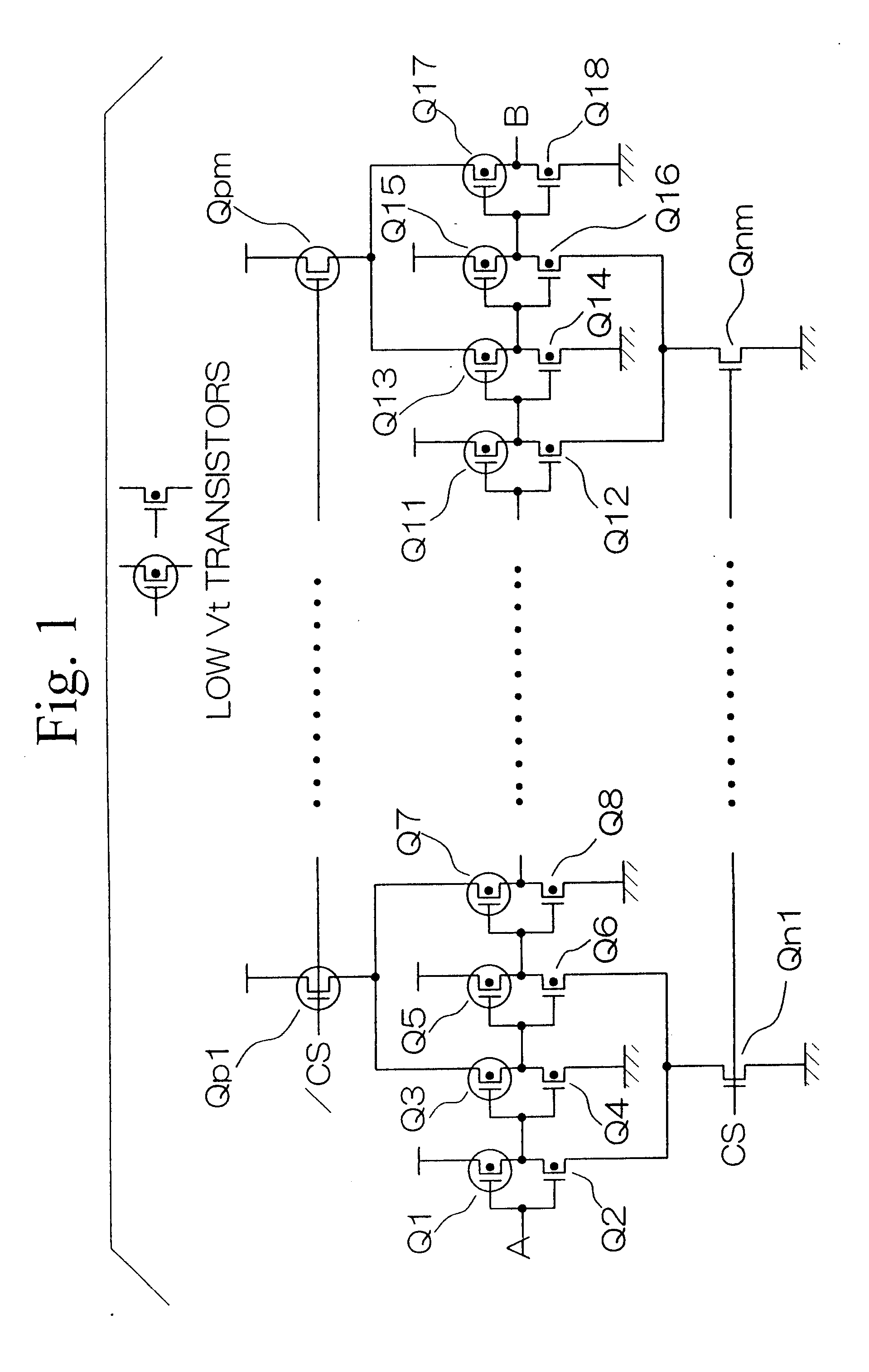

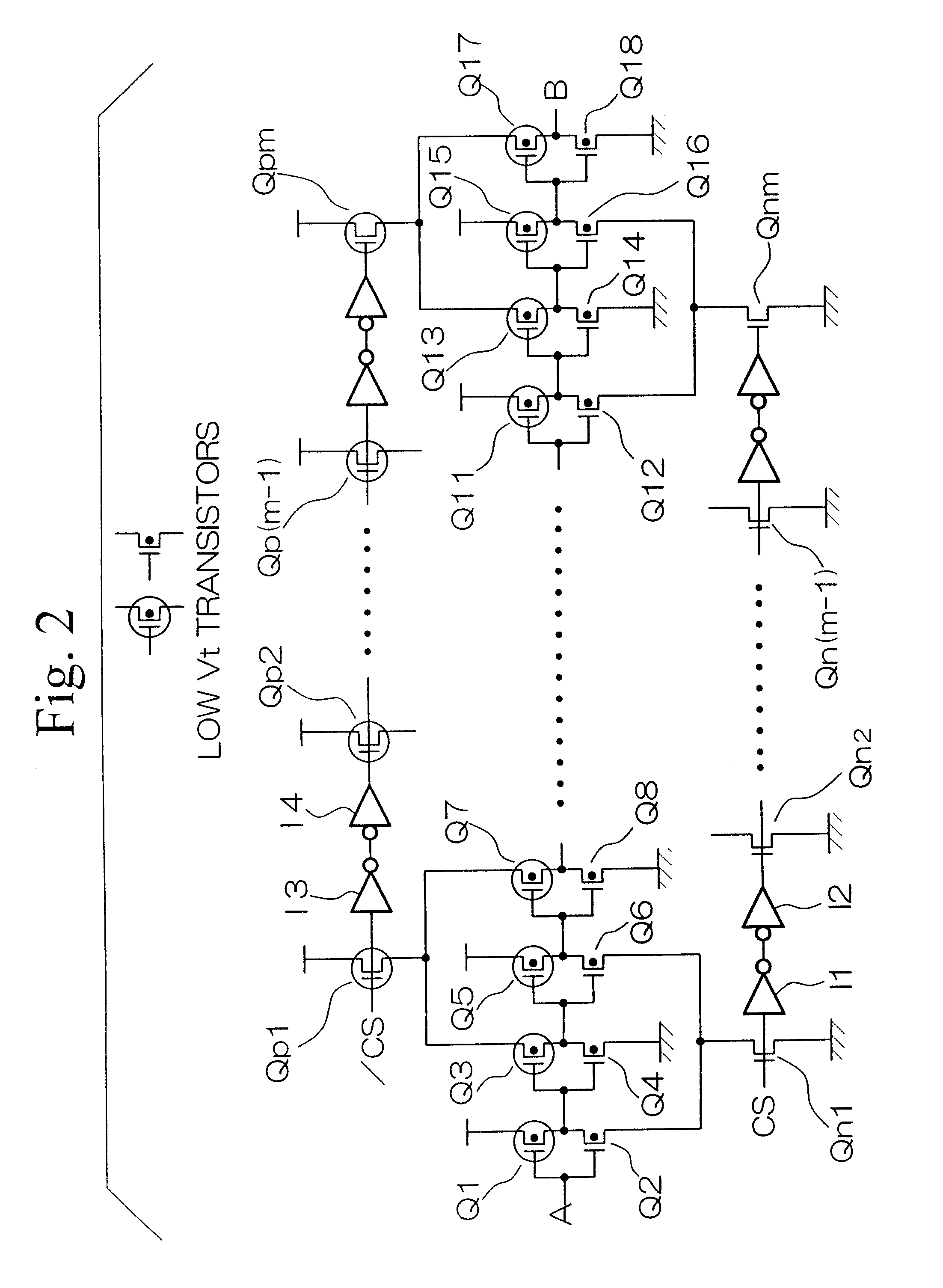

Semiconductor device with power cutting transistors

A semiconductor device that operates at high speed using a low voltage power source, in which the output of each gate in the standby state is stable, and which has a delay time that is not affected by the frequency of the input signal.TrQ1 to TrQ8, which form multiple stages of the inverters are designed to have a low threshold voltage in order to accomplish low voltage operation. When input node A is at "L" in the standby state, TrQ2, Q3, Q6, and Q8 which cut-off are connected to high threshold voltage TrQn1 and Qp1. In the standby state, power cutting TrQn1 and Qp1 cut off in accordance with chip selecting signals CS, / CS, thereby blocking the flow of sub-threshold current to TrQ1~Q8. Since TrQ1, Q4, Q5 and Q8 are not cut off at this time, the output potential of each inverter is stable. The number of transistors assigned to each power cutting transistor is determined based on the frequency of the input signal, so that only one transistor from among the transistors connected to TrQn1 and Qp1 will be ON at any given time.

Owner:RENESAS ELECTRONICS CORP

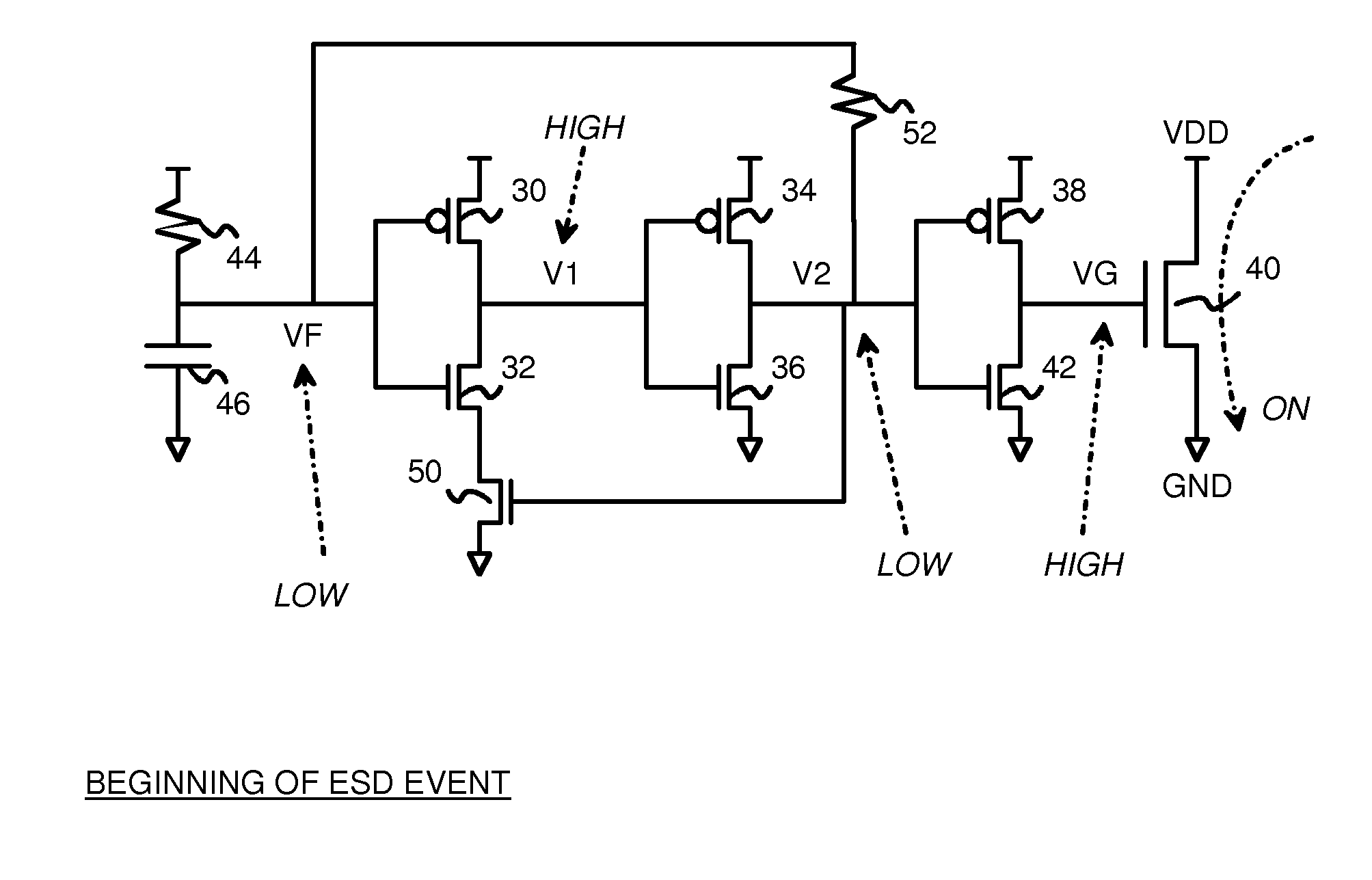

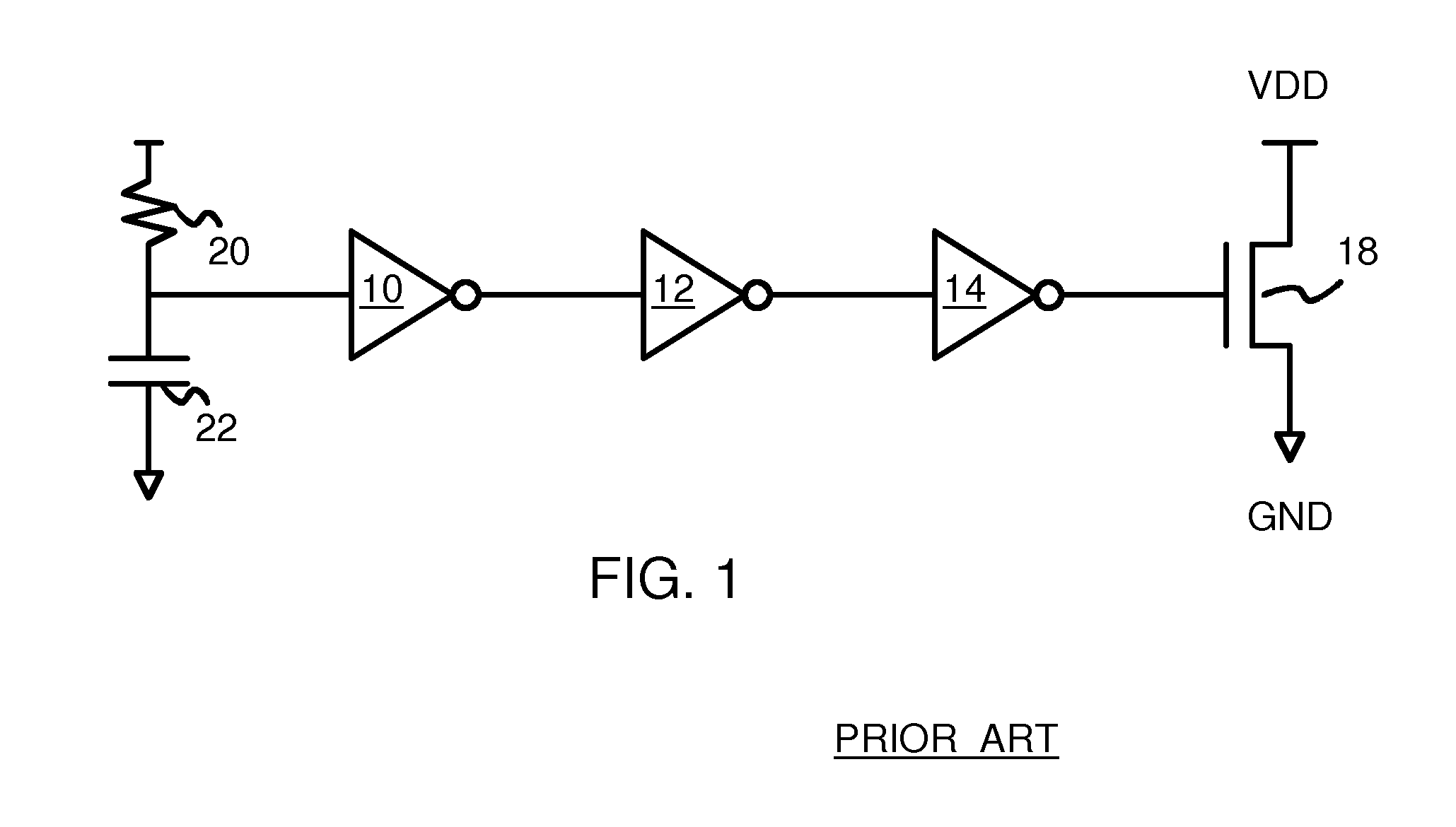

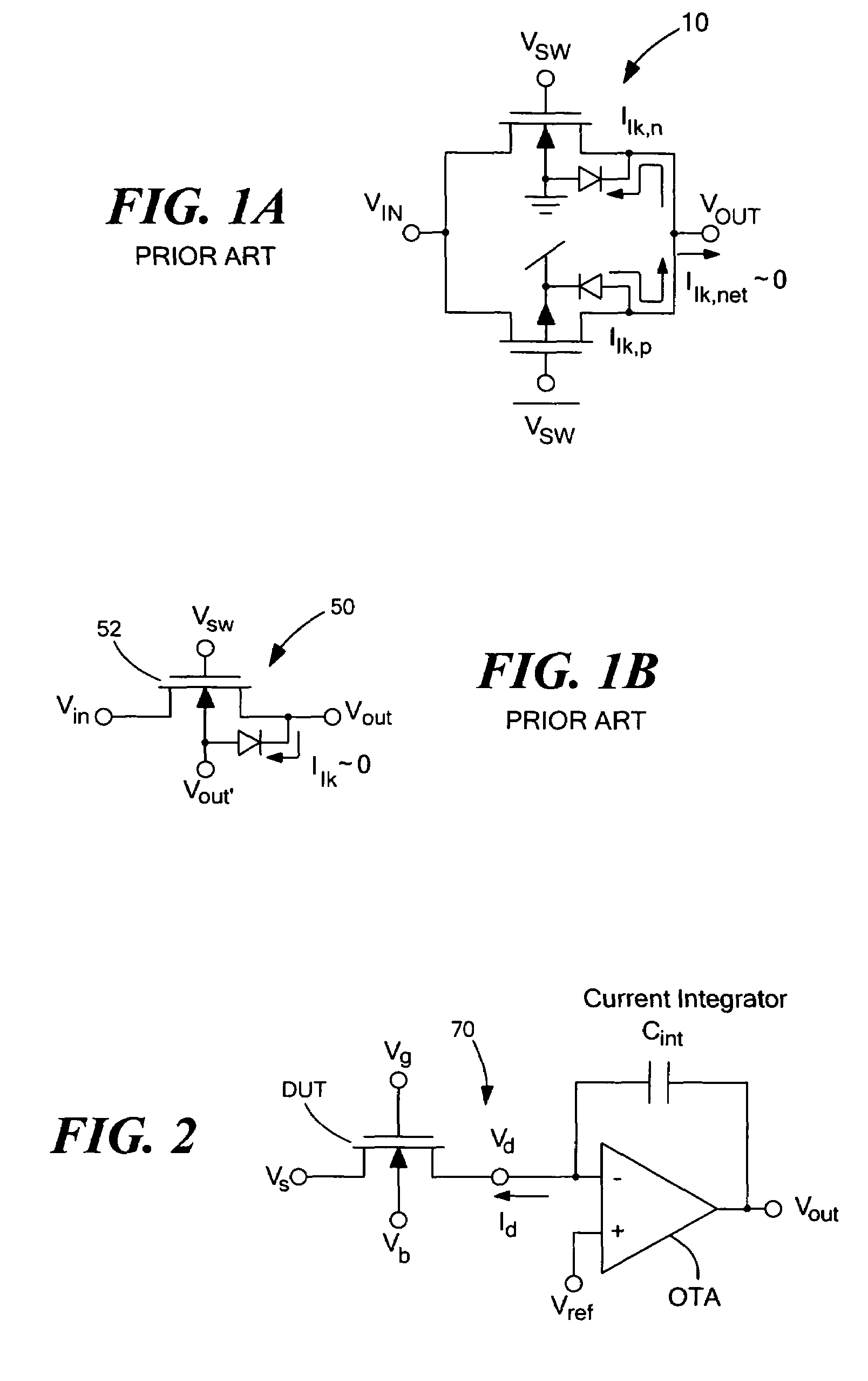

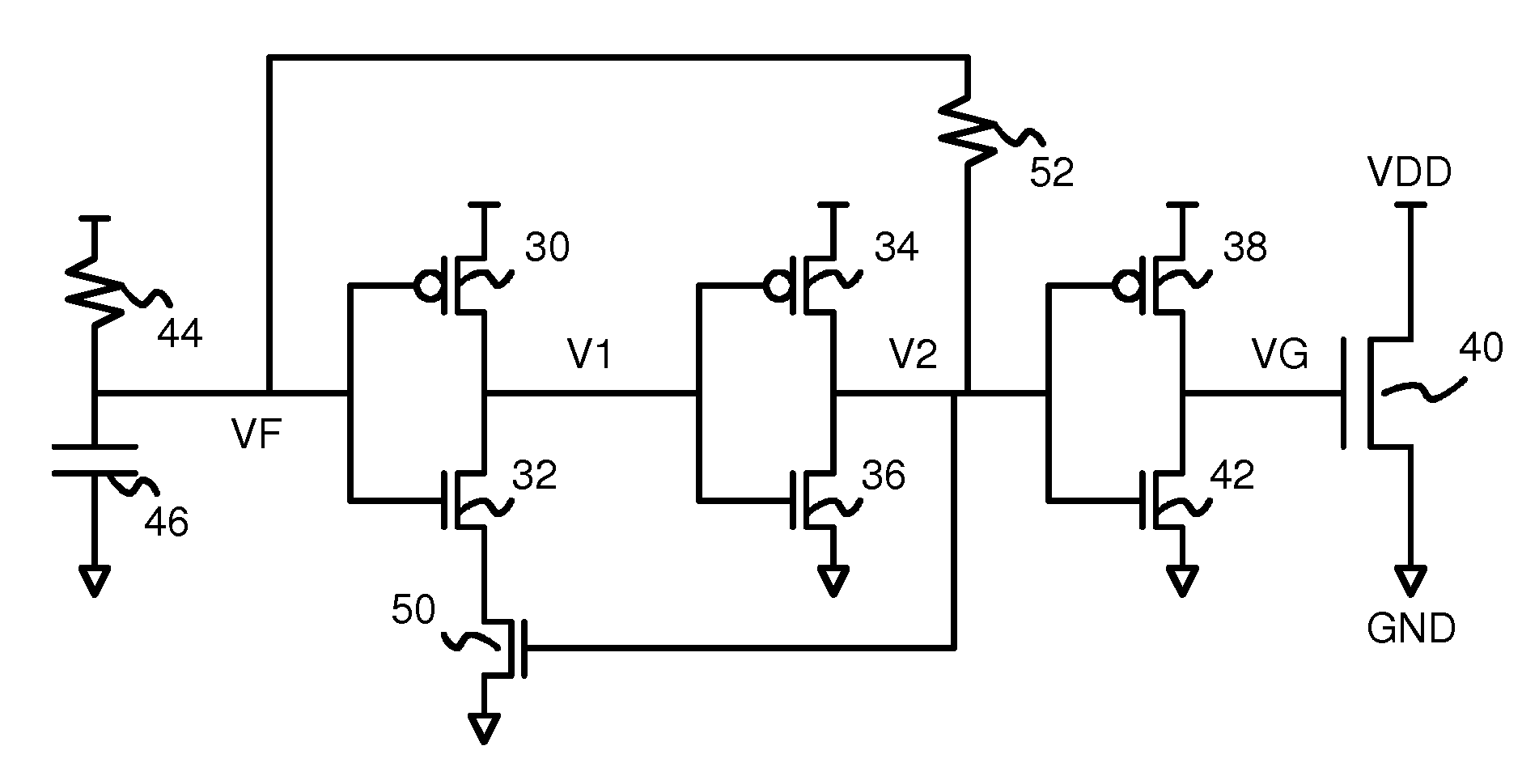

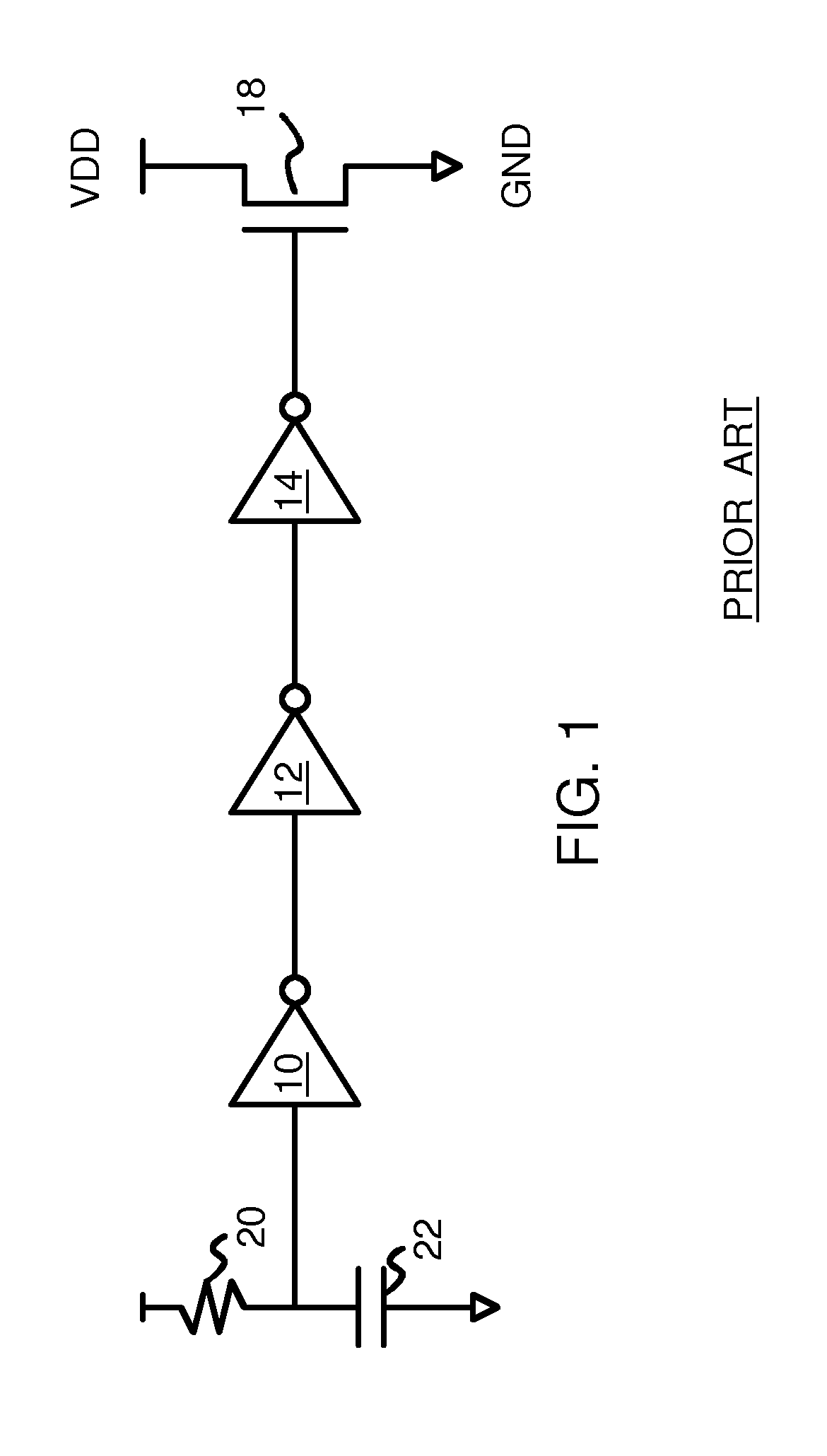

NMOS-Based Feedback Power-Clamp for On-Chip ESD Protection

ActiveUS20110299202A1Emergency protective arrangements for limiting excess voltage/currentArrangements responsive to excess voltageHigh resistanceSub threshold

A power-to-ground clamp transistor provides electrostatic discharge (ESD) protection. A filter capacitor and resistor generate a filter voltage that is buffered by three stages to drive the gate of the clamp transistor. The filter capacitor is about twenty times smaller than in a conventional clamp circuit. Feedback in the circuit keeps the clamp transistor turned on after the R-C time constant of the capacitor and resistor in the filer has elapsed, allowing for a smaller capacitor to turn on the clamp transistor longer. A sub-threshold-conducting transistor in the first stage conducts only a small sub-threshold current, which extends the discharge time of the first stage. The gate of the sub-threshold-conducting transistor is driven by feedback from the second stage. A feed-forward resistor has a high resistance value to slowly raise the voltage of the second stage from the filter voltage, and thus slowly raise the gate of the sub-threshold-conducting transistor.

Owner:HONG KONG APPLIED SCI & TECH RES INST

I-shaped gate electrode for improved sub-threshold mosfet performance

ActiveUS20150380551A1Reduce electrical conductivityEasy compatibilityTransistorSemiconductor/solid-state device manufacturingMOSFETSub threshold

Metal-oxide-semiconductor (MOS) transistors with reduced subthreshold conduction, and methods of fabricating the same. Transistor gate structures are fabricated in these transistors of a shape and dimension as to overlap onto the active region from the interface between isolation dielectric structures and the transistor active areas. Minimum channel length conduction is therefore not available at the isolation-to-active interface, but rather the channel length along that interface is substantially lengthened, reducing off-state conduction.

Owner:TEXAS INSTR INC

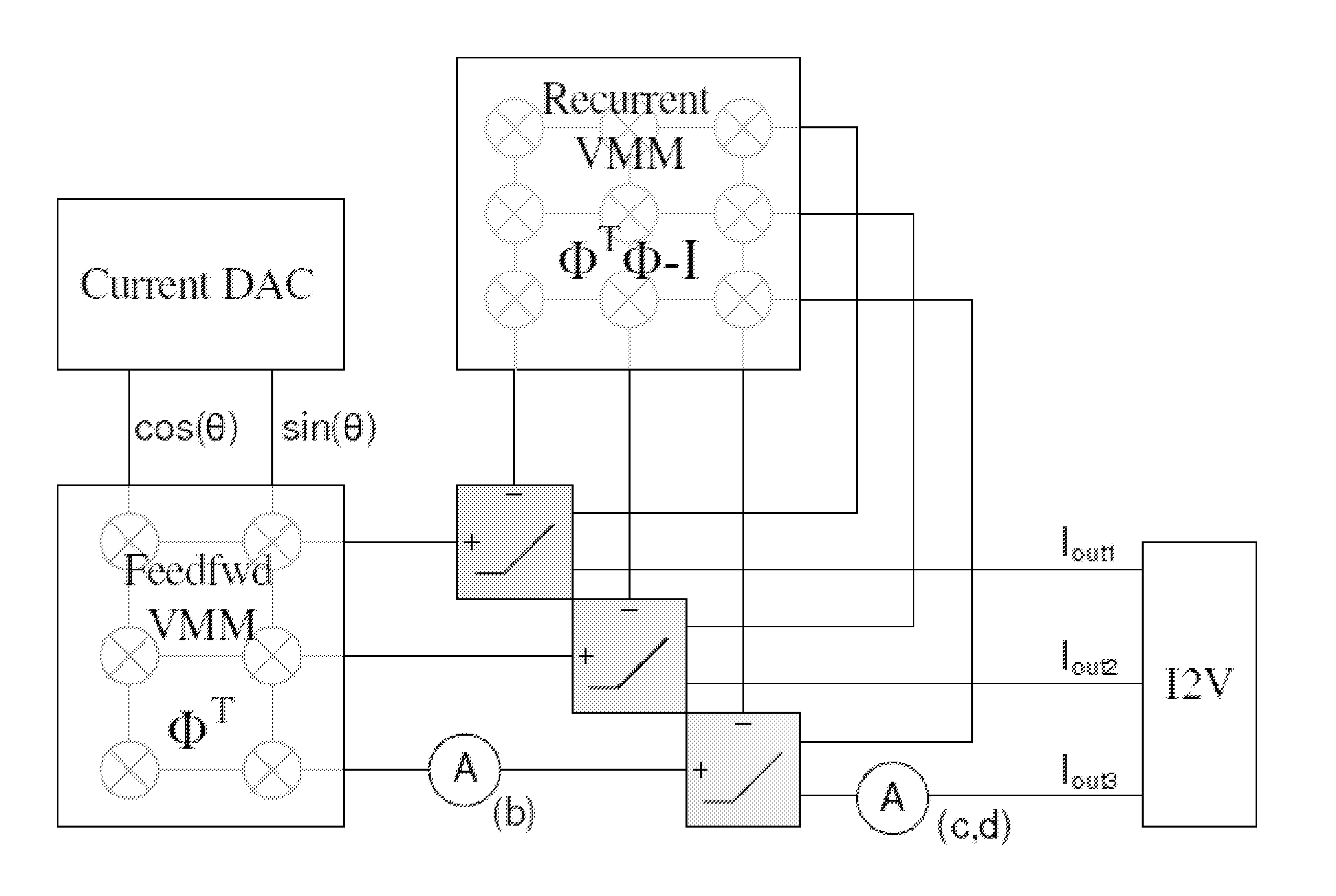

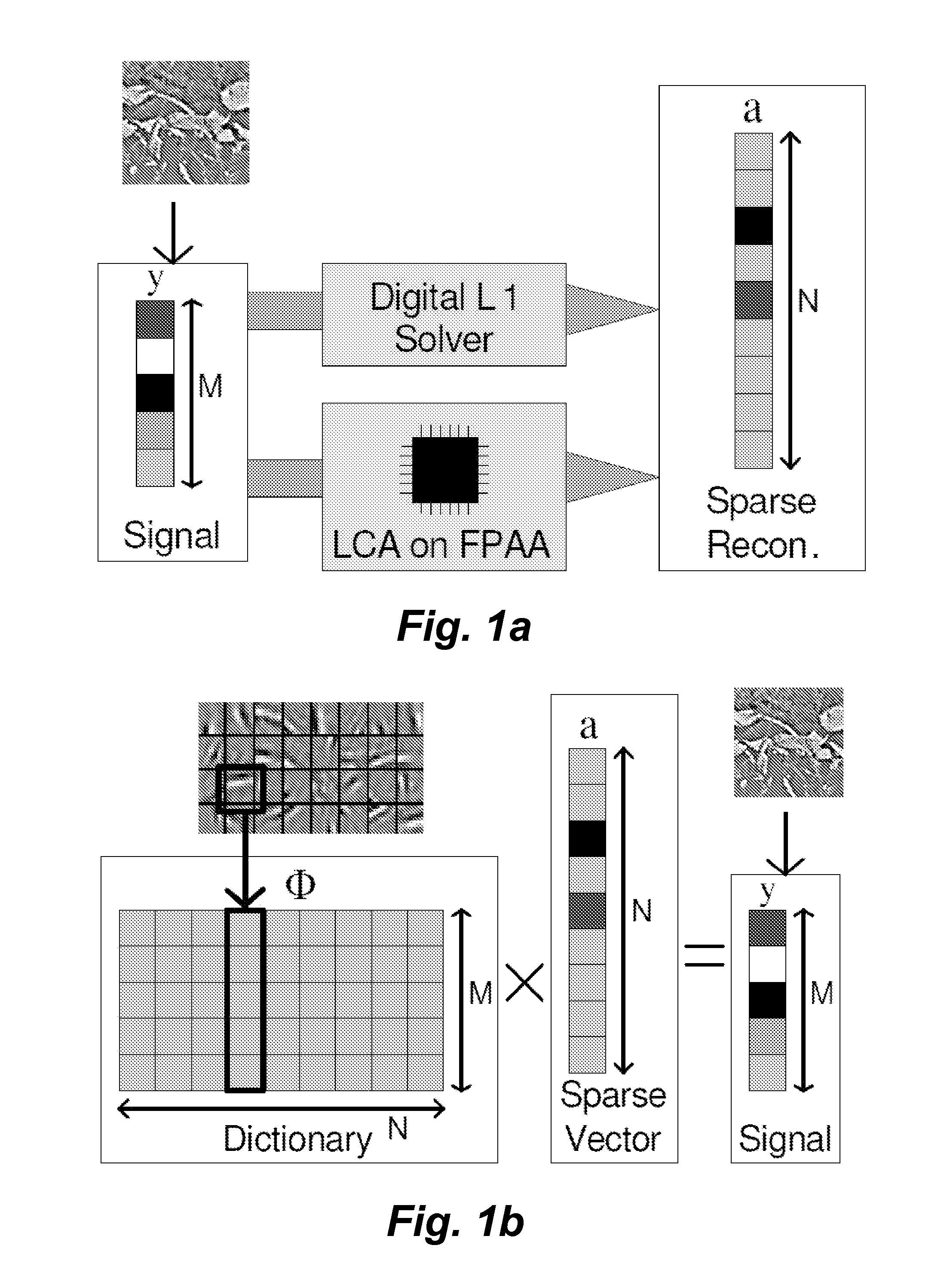

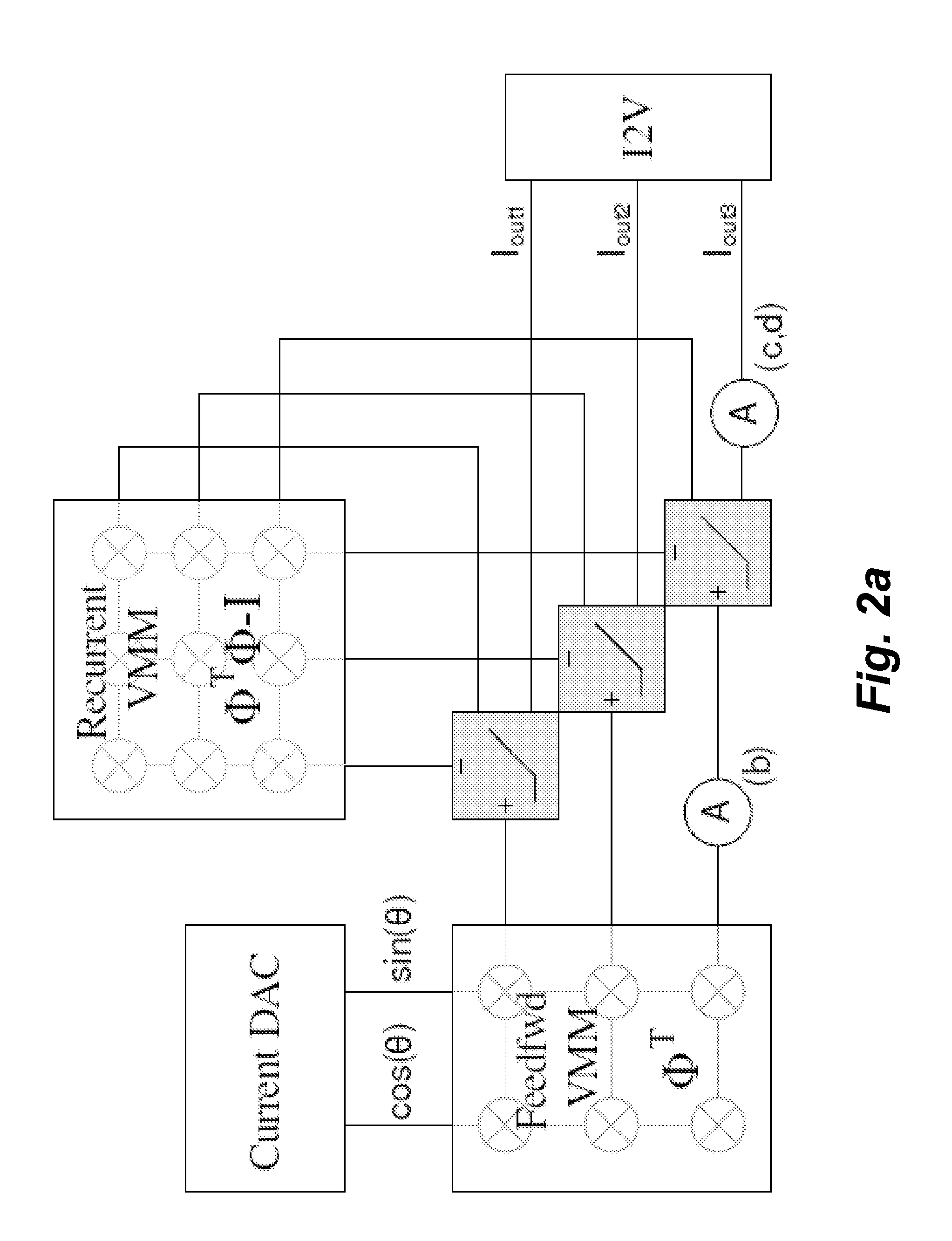

Analog programmable sparse approximation system

InactiveUS20130318020A1Reduce energy consumptionLower computational expenseDigital computer detailsDigital dataSub thresholdAnalog chip

A system and device for solving sparse algorithms using hardware solutions is described. The hardware solution can comprise one or more analog devices for providing fast, energy efficient solutions to small, medium, and large sparse approximation problems. The system can comprise sub-threshold current mode circuits on a Field Programmable Analog Array (FPAA) or on a custom analog chip. The system can comprise a plurality of floating gates for solving linear portions of a sparse signal. The system can also comprise one or more analog devices for solving non-linear portions of sparse signal.

Owner:GEORGIA TECH RES CORP

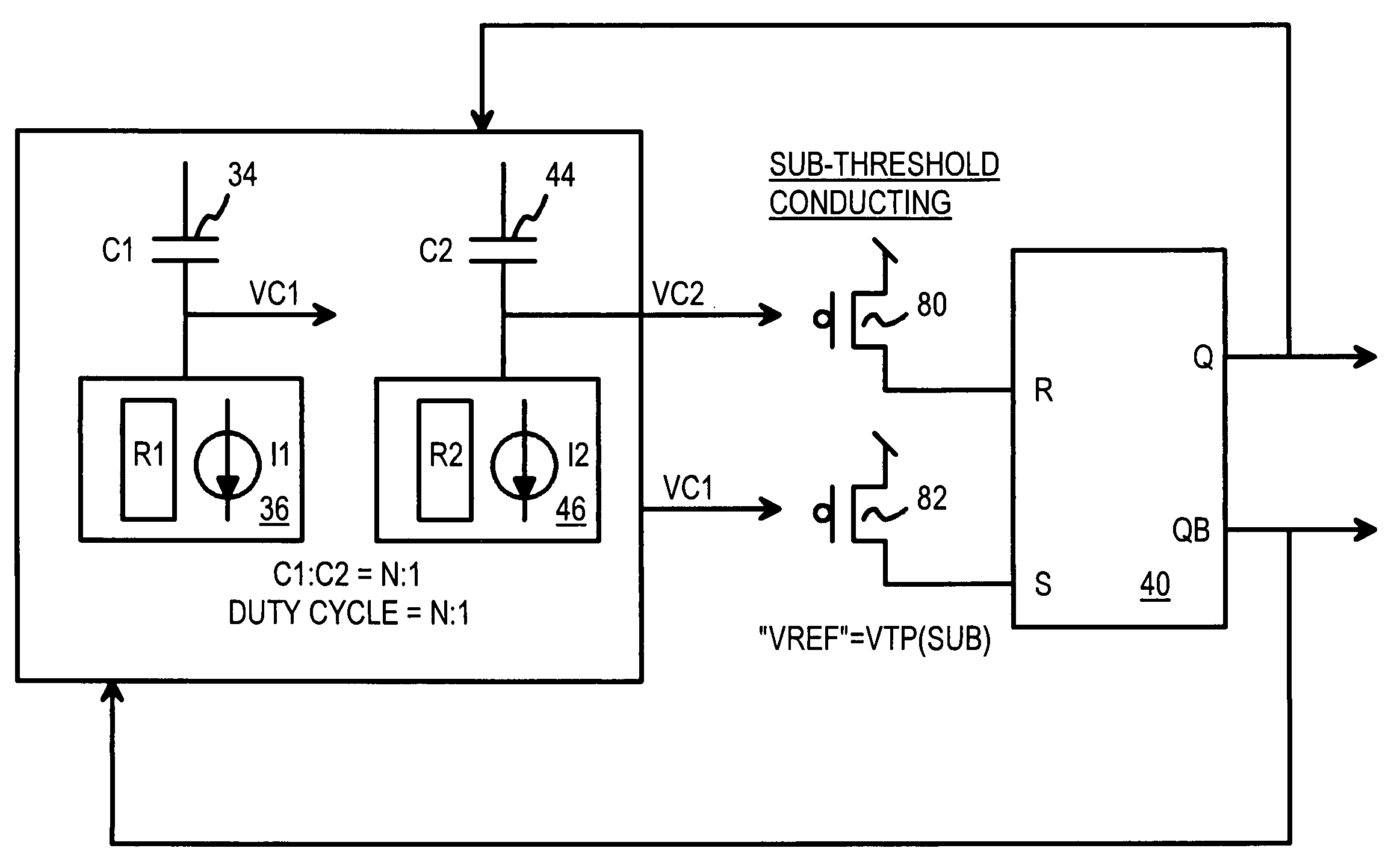

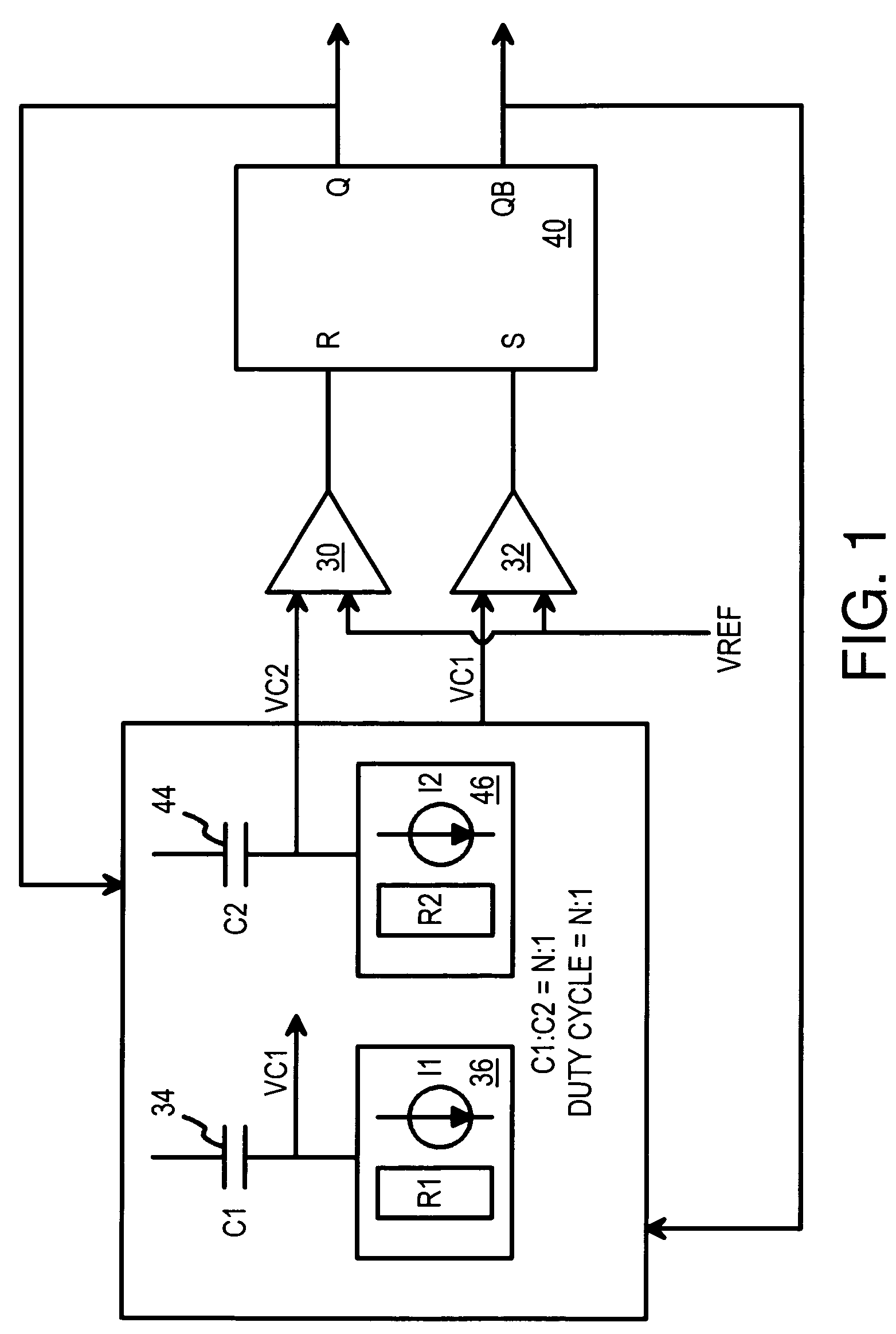

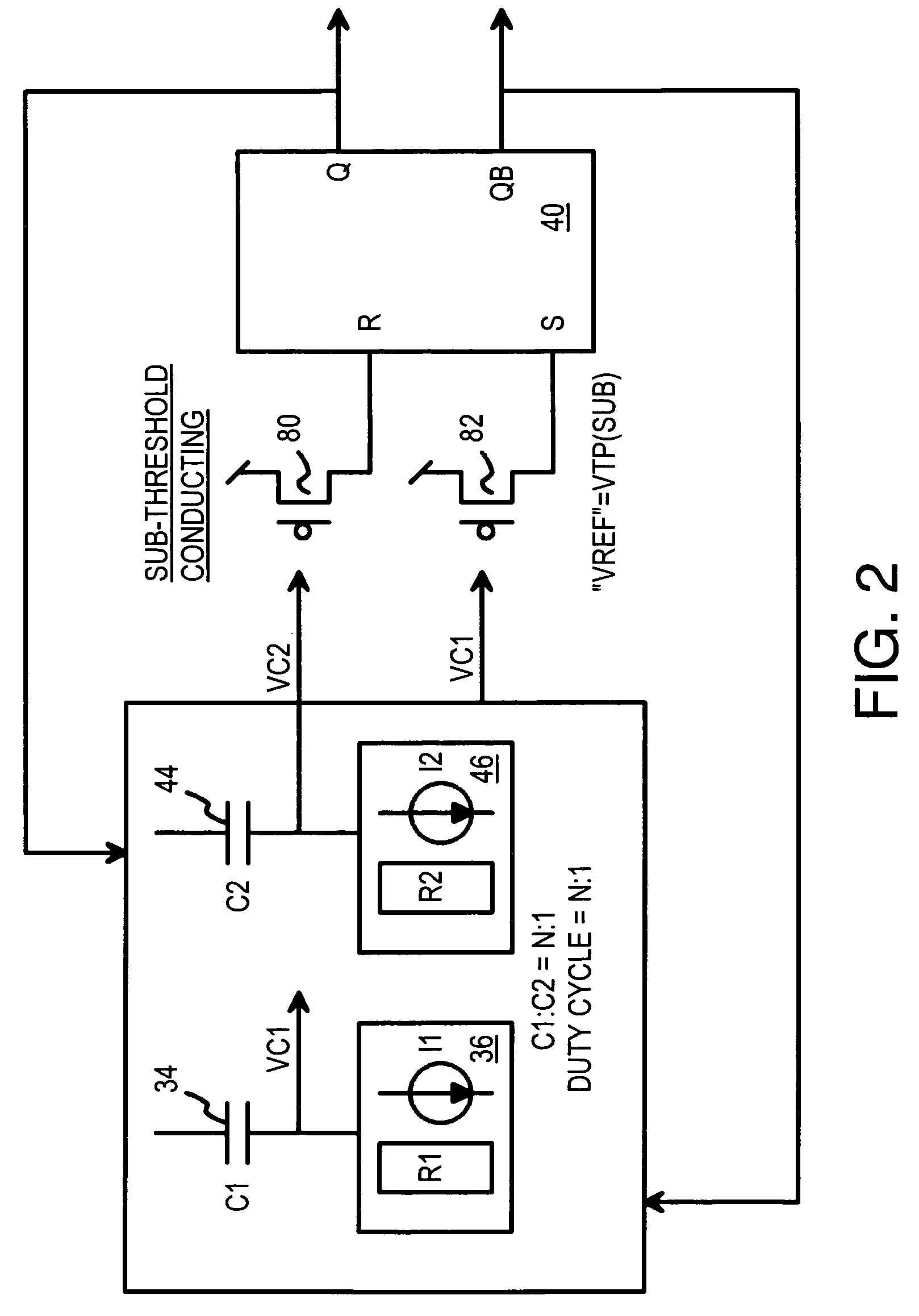

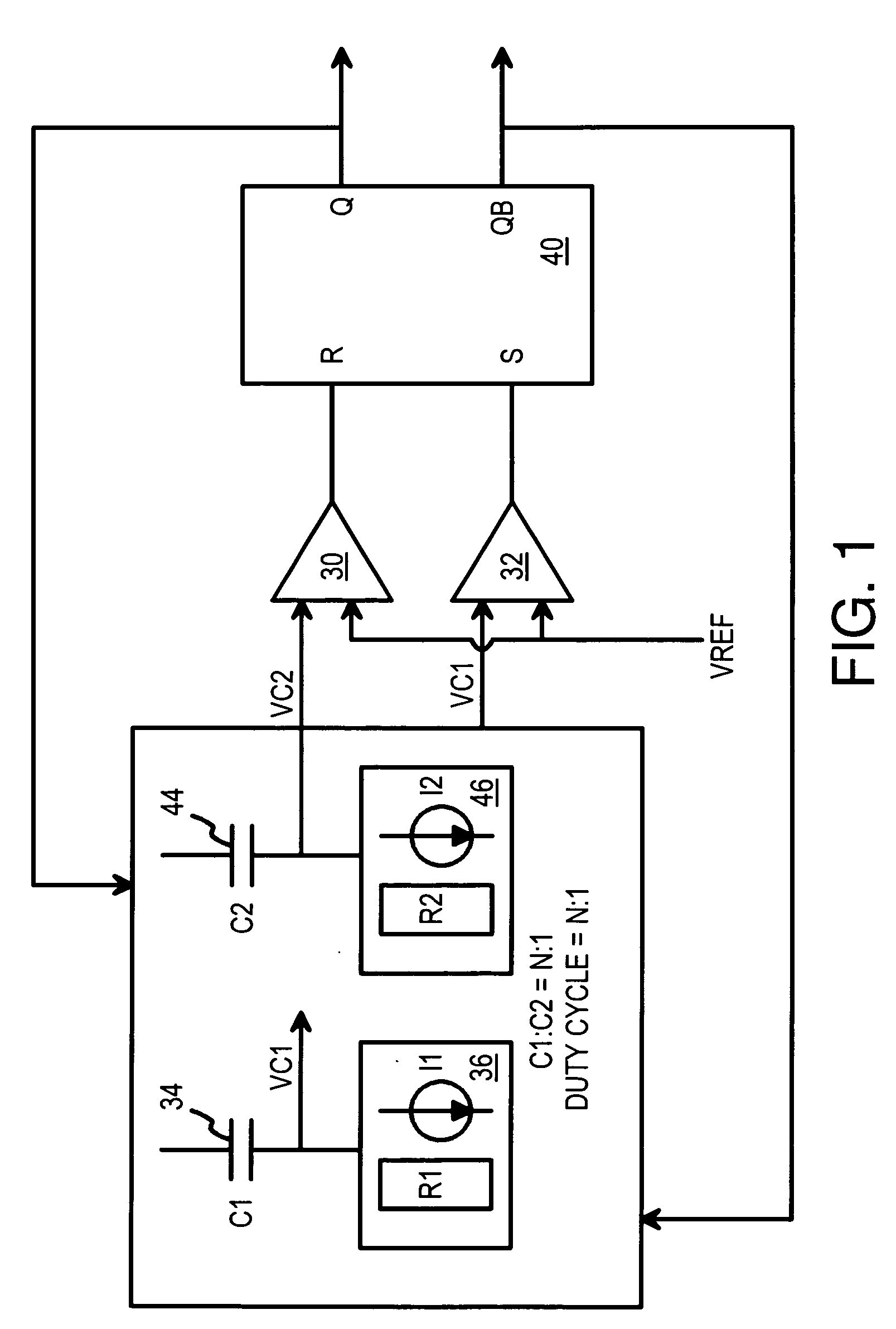

Low-voltage oscillator with capacitor-ratio selectable duty cycle

InactiveUS7705685B2Pulse generation by bipolar transistorsPulse automatic controlCapacitanceSub threshold

An oscillator operates at a very low voltage yet has a duty cycle that is set by a ratio of capacitors that are charged and discharged. Sub-threshold p-channel transistors conduct sub-threshold currents below the normal threshold voltage, and drive set and reset inputs of a set-reset S-R latch. The S-R latch drives the oscillator outputs. The oscillator outputs feed back to charging p-channel transistors that charge one plate of the capacitors. During half of the cycle, the charging p-channel transistor is off, allowing one plate of the capacitors to discharge through an n-channel discharge transistor. After a period of discharge determined by the capacitance of the capacitor, the gate of a sub-threshold p-channel transistor falls enough for sub-threshold current to flow, triggering the set or reset input of the S-R latch. Since sub-threshold currents are needed to toggle the S-R latch, the oscillator begins to oscillate below the threshold voltage.

Owner:HONG KONG APPLIED SCI & TECH RES INST

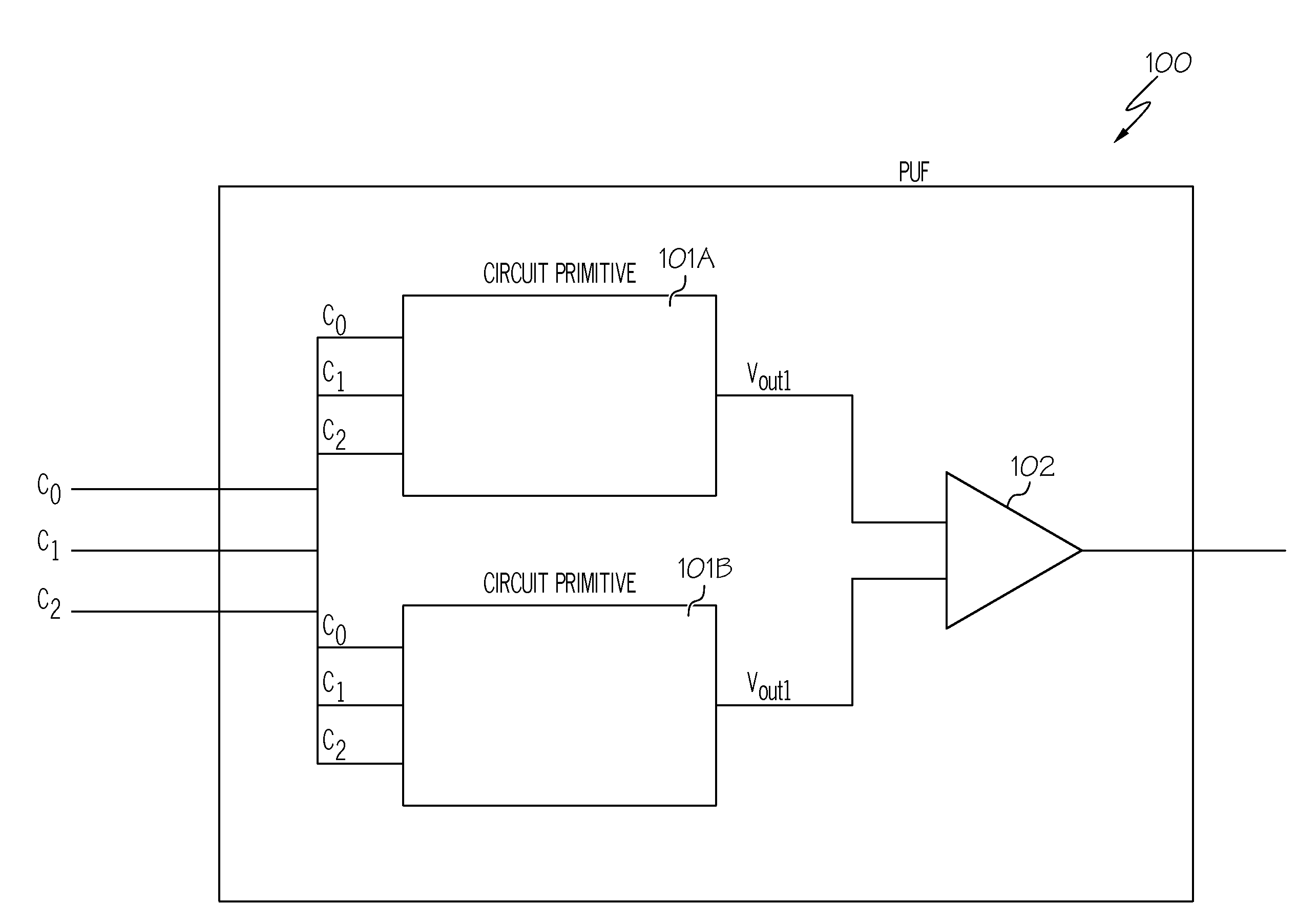

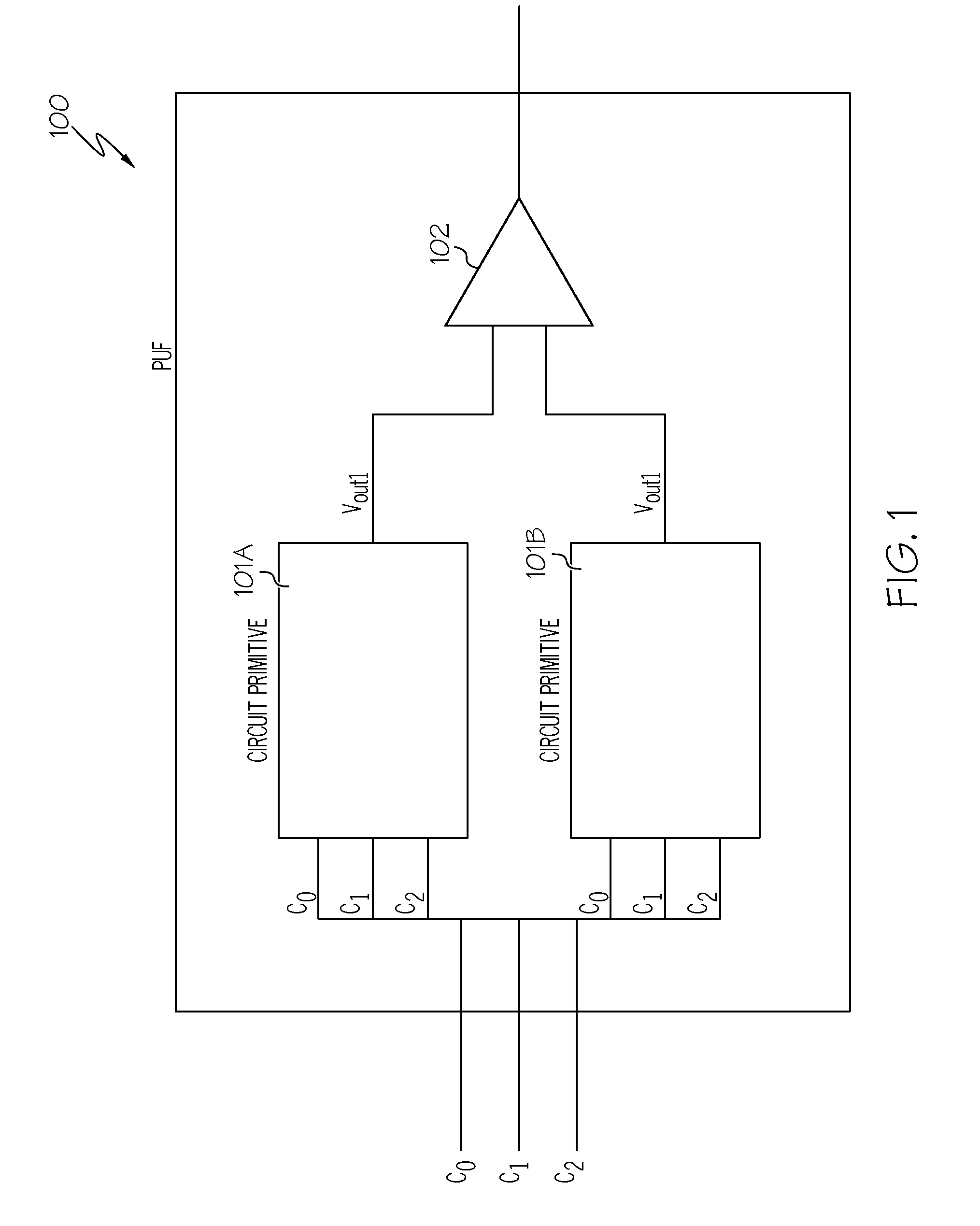

Physically unclonable functions based on non-linearity of sub-threshold operation

InactiveUS8938069B2Key distribution for secure communicationEncryption apparatus with shift registers/memoriesSub thresholdPhysical unclonable function

An electronic circuit for implementing a physically unclonable function. The electronic circuit includes duplicate circuits, referred to as “circuit primitives,” that generate a first and a second output voltage based on the received input, referred to as a “challenge.” The electronic circuit further includes a comparator coupled to the circuit primitives and generates an output based on the difference between the first and second output voltages. While the circuit primitives contain duplicate circuitry, the circuit primitives may generate a different output voltage due to a particular set of transistors in the circuit primitives operating in the sub-threshold region whose gates are tied to ground and whose sub-threshold current, the magnitude of which is random based on the threshold voltage variation of the set of transistors, is used to affect the value of the output voltage.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

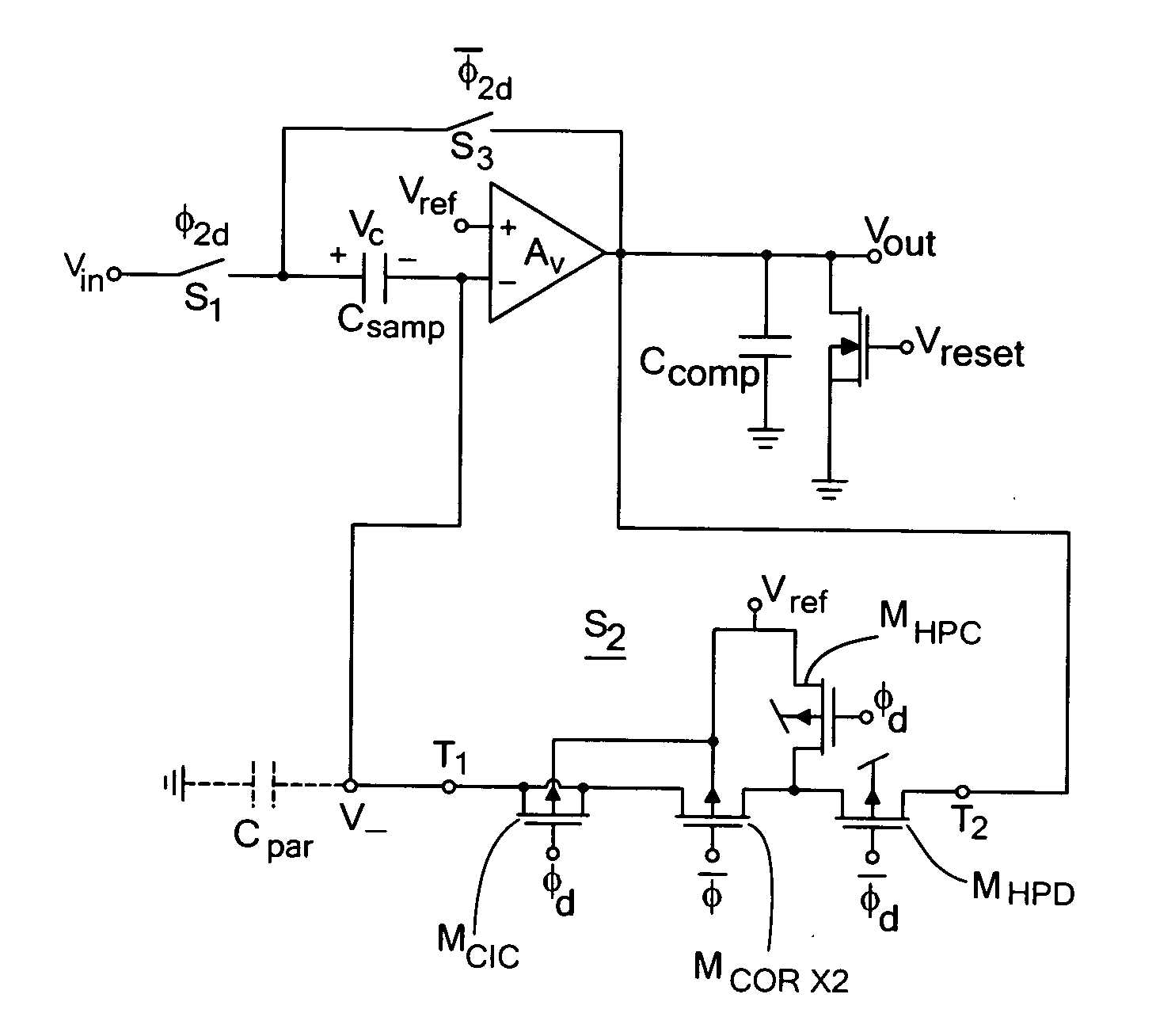

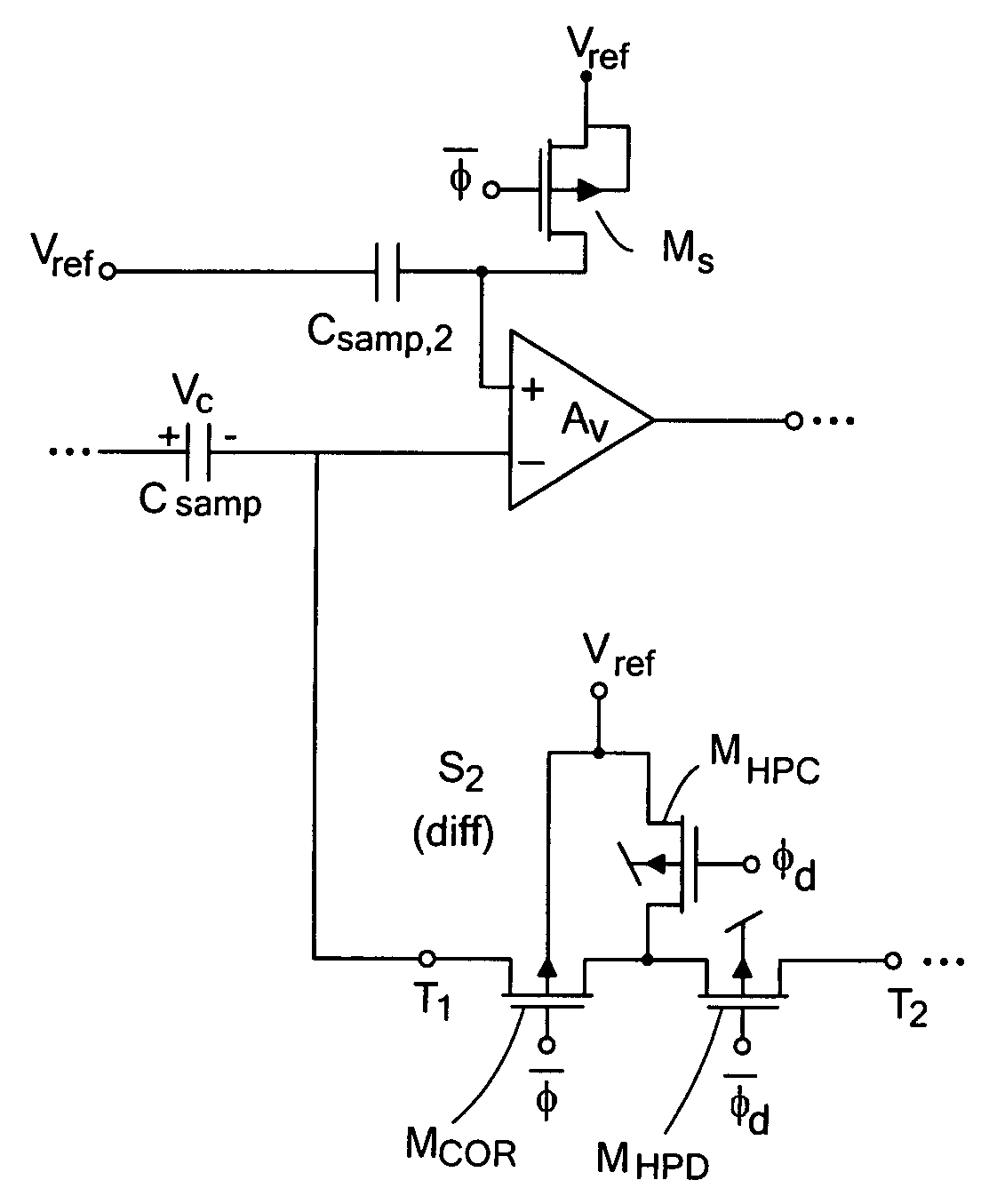

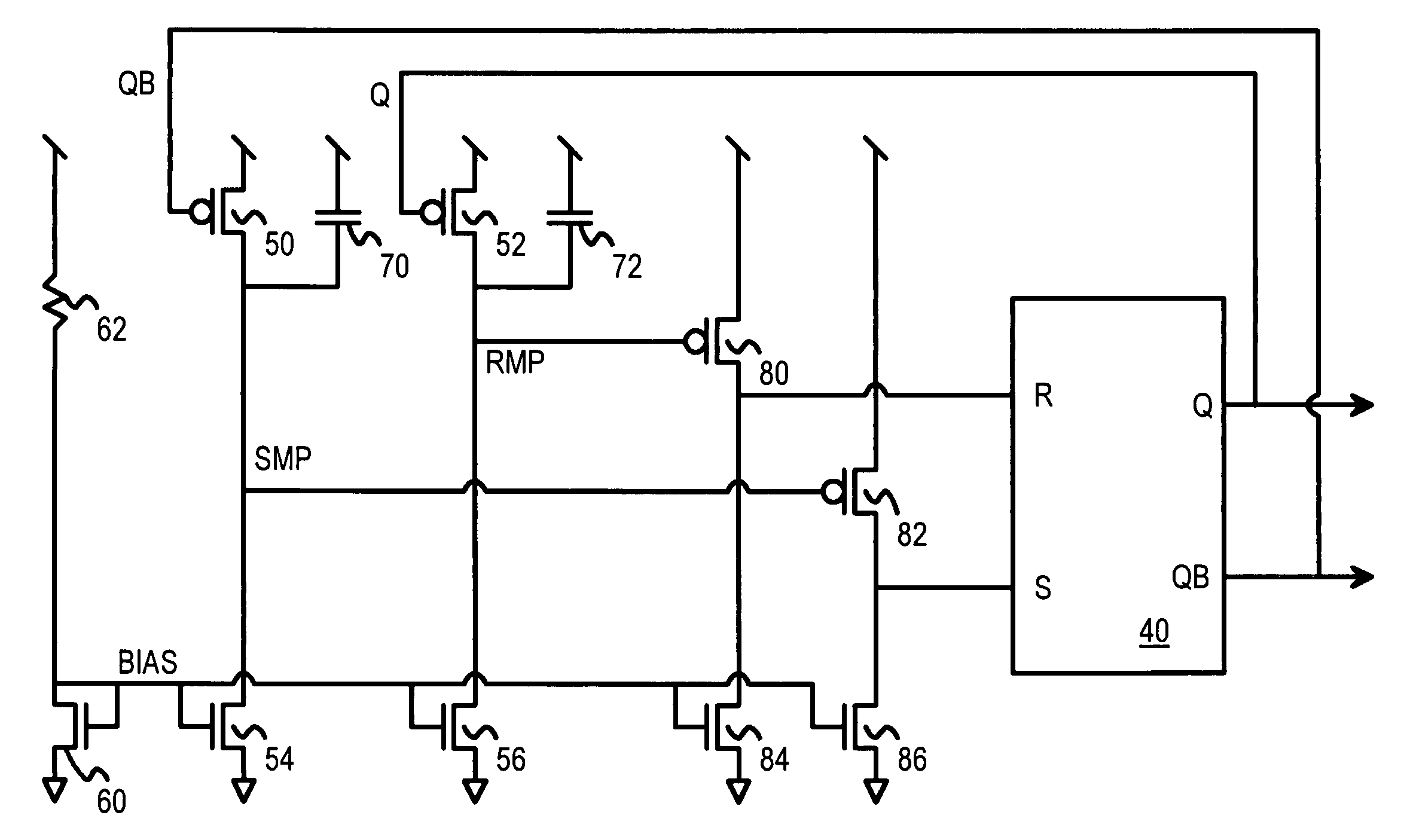

Analog storage cell with low leakage

ActiveUS20060087362A1Minimize accumulation mode conductionMinimize leakage currentElectric analogue storesElectronic switchingAudio power amplifierDevice form

An analog storage cell circuit includes a switch that minimizes subthreshold conduction and diode leakage, as well as an accumulation-mode coupling mechanism to minimize overall switch leakage to minimize accumulation-mode leakage. In one embodiment, an analog storage circuit includes a sample and hold circuit including an amplifier having first and second inputs and a switch coupled to the first input of the amplifier. The switch includes a first switching device forming a core of the switch, a second switching device coupled to the first switching device to disconnect the first switching device from a first terminal during the hold phase, and a third switching device coupled to the first switching device to connect the first switching device to a second terminal during the hold phase to minimize accumulation mode conduction in the first switching device.

Owner:MASSACHUSETTS INST OF TECH

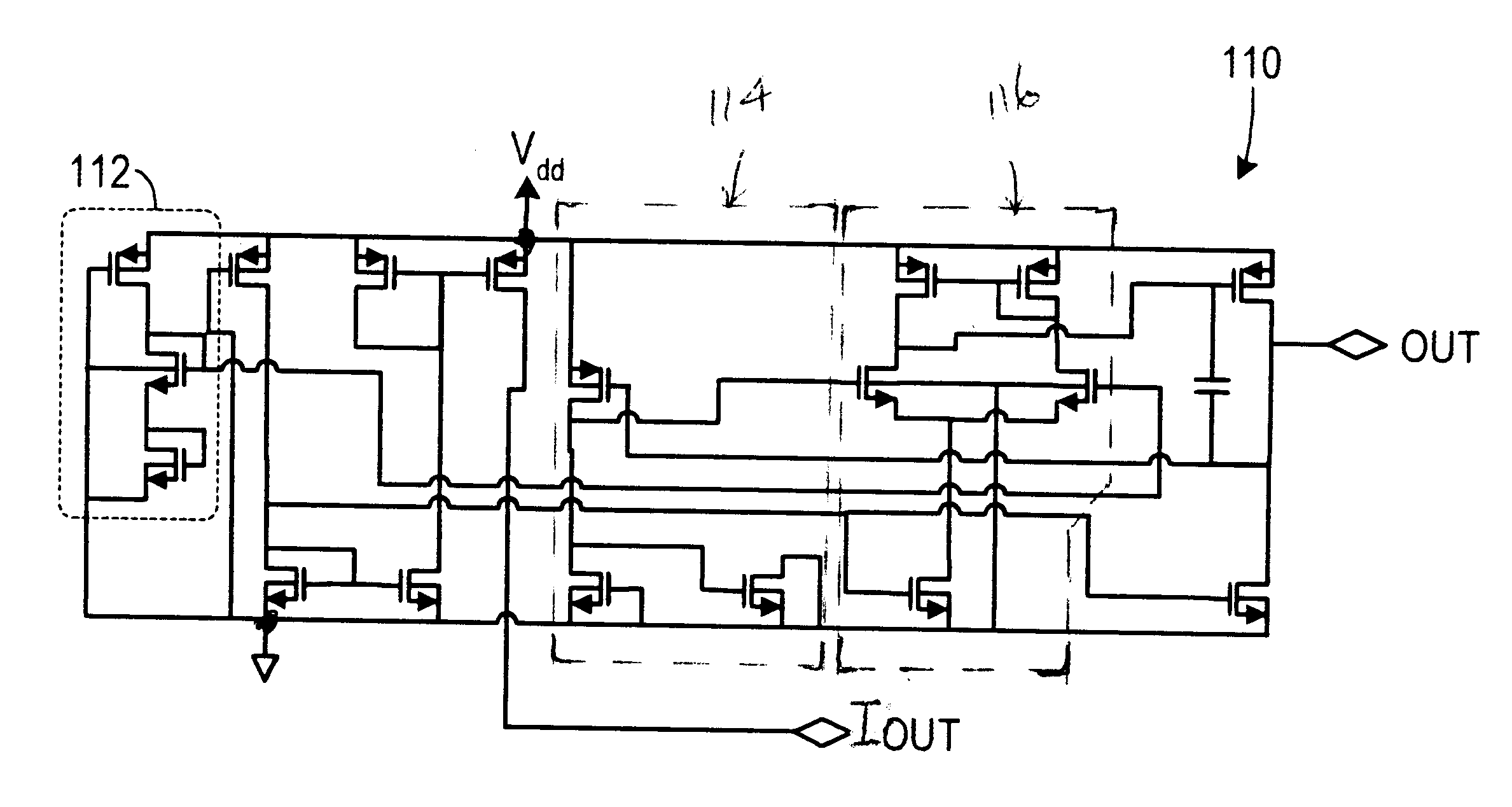

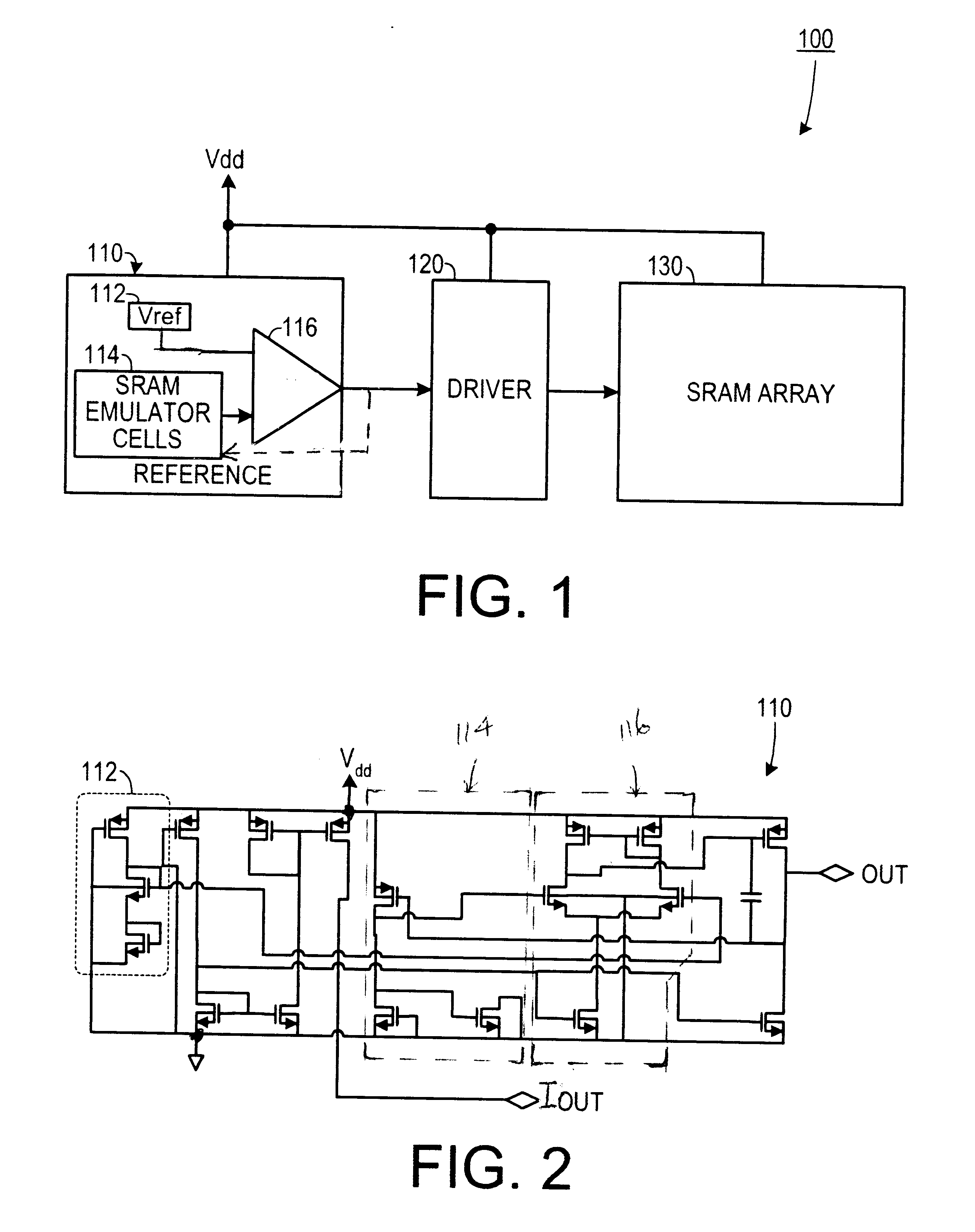

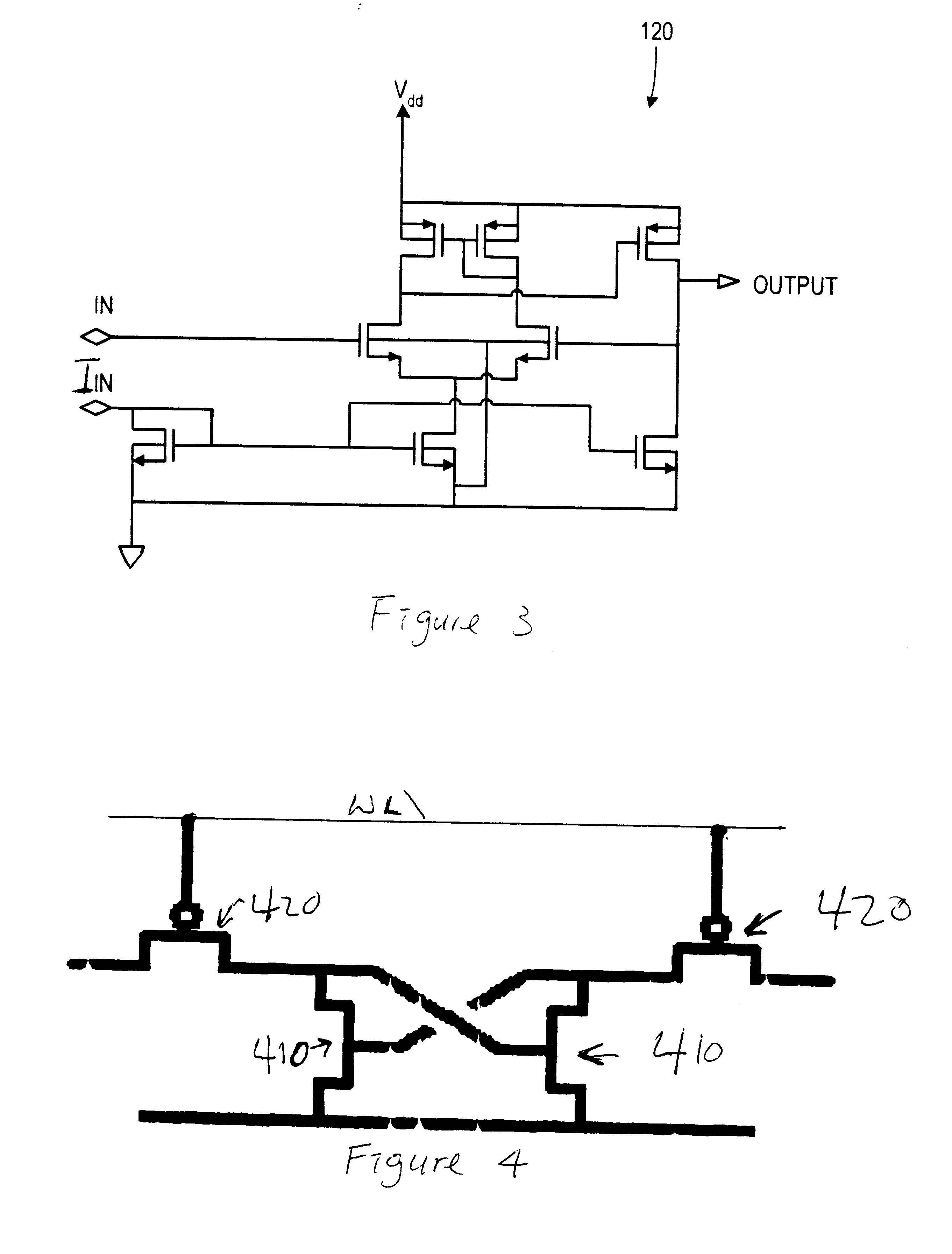

Bias cell for four transistor (4T) SRAM operation

InactiveUS6628540B2Reduce power consumptionMeet the blocking requirementsDigital storageNegative feedbackStatic random-access memory

Quiescent current drawn by an array of four-transistor loadless static random access memory (SRAM) cells is minimized by using a negative feedback loop to set a reference voltage, for the wordline driver, to a level which reduces the subthreshold current through the pass transistors to a level which is just barely sufficient to reliably retain data.

Owner:TEXAS INSTR INC

Semiconductor device and method of manufacturing the same

ActiveUS7675110B2Reduce stepsHighly integratedSolid-state devicesSemiconductor/solid-state device manufacturingSub thresholdSubthreshold conduction

After an element isolation region is formed using a field-forming silicon nitride film, the silicon nitride film and a semiconductor substrate are patterned. Thereafter, the silicon nitride film and the semiconductor substrate are patterned, thereby forming a gate trench reaching the semiconductor substrate in an active region. Next, after a gate electrode is formed within a gate trench, the silicon nitride film is removed, thereby forming a contact hole. A contact plug is buried into this contact hole. Accordingly, a diffusion layer contact pattern becomes unnecessary, and the active region can be reduced. Because a gate electrode is buried in the gate trench, a gate length is increased, and a sub-threshold current can be reduced.

Owner:LONGITUDE LICENSING LTD

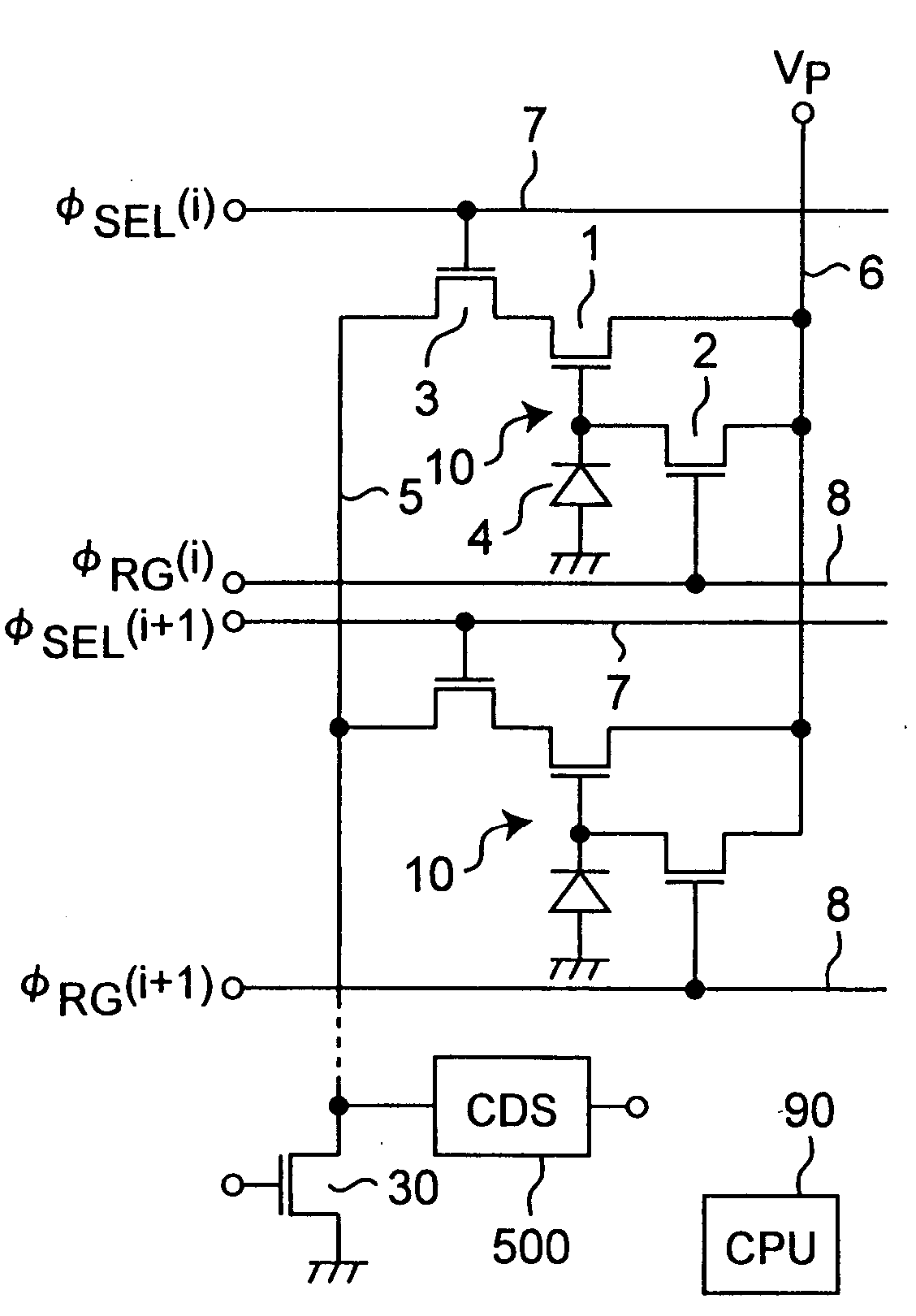

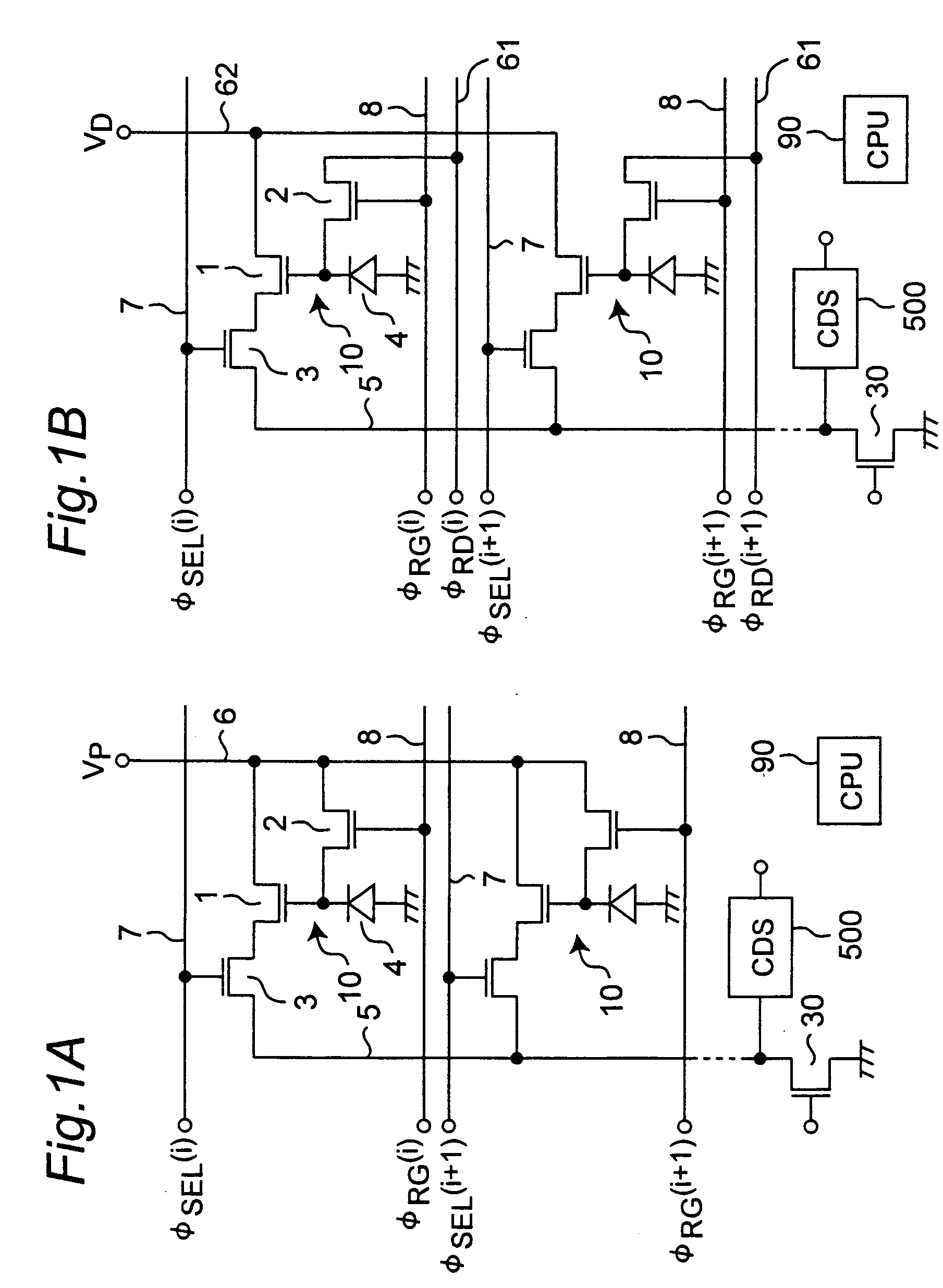

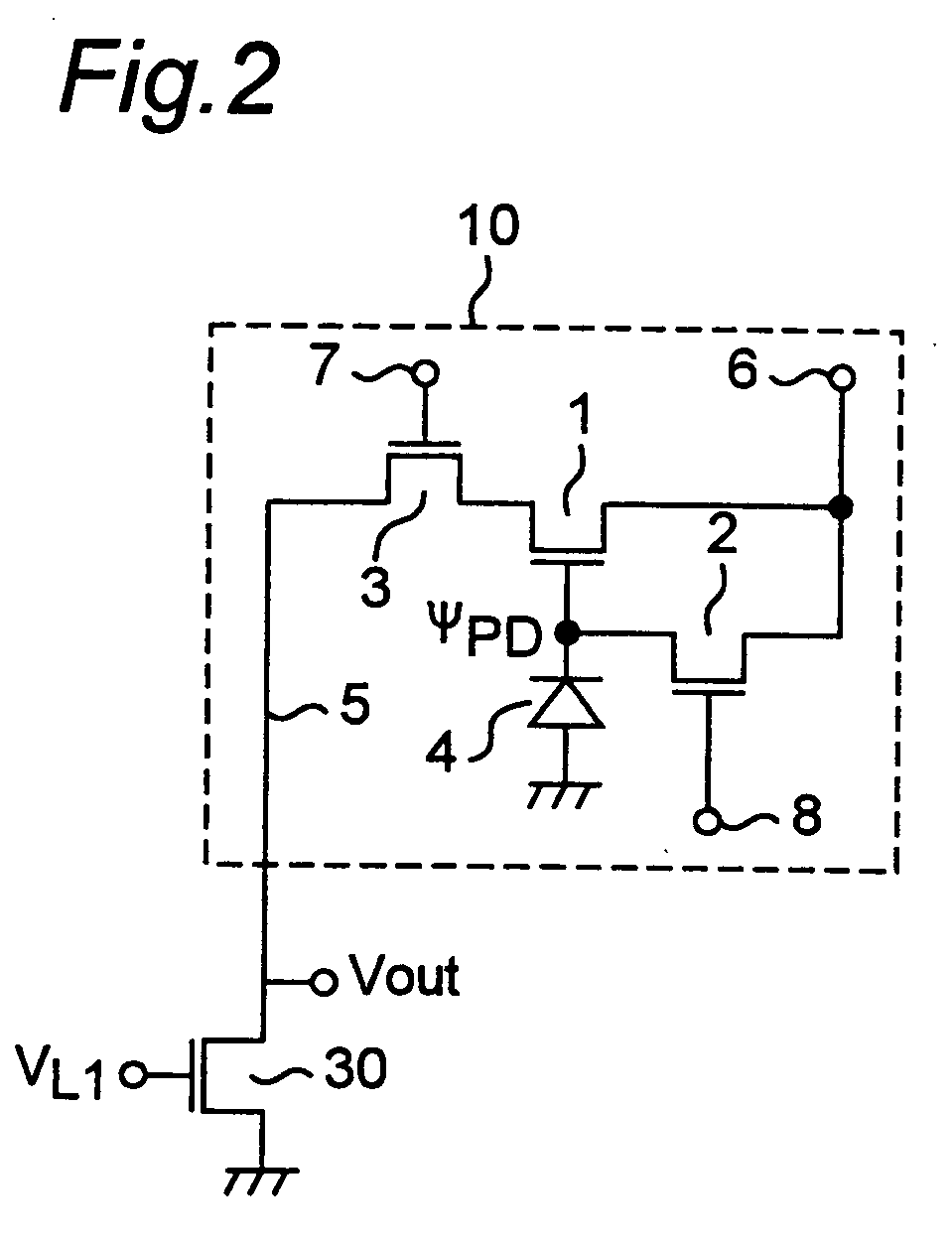

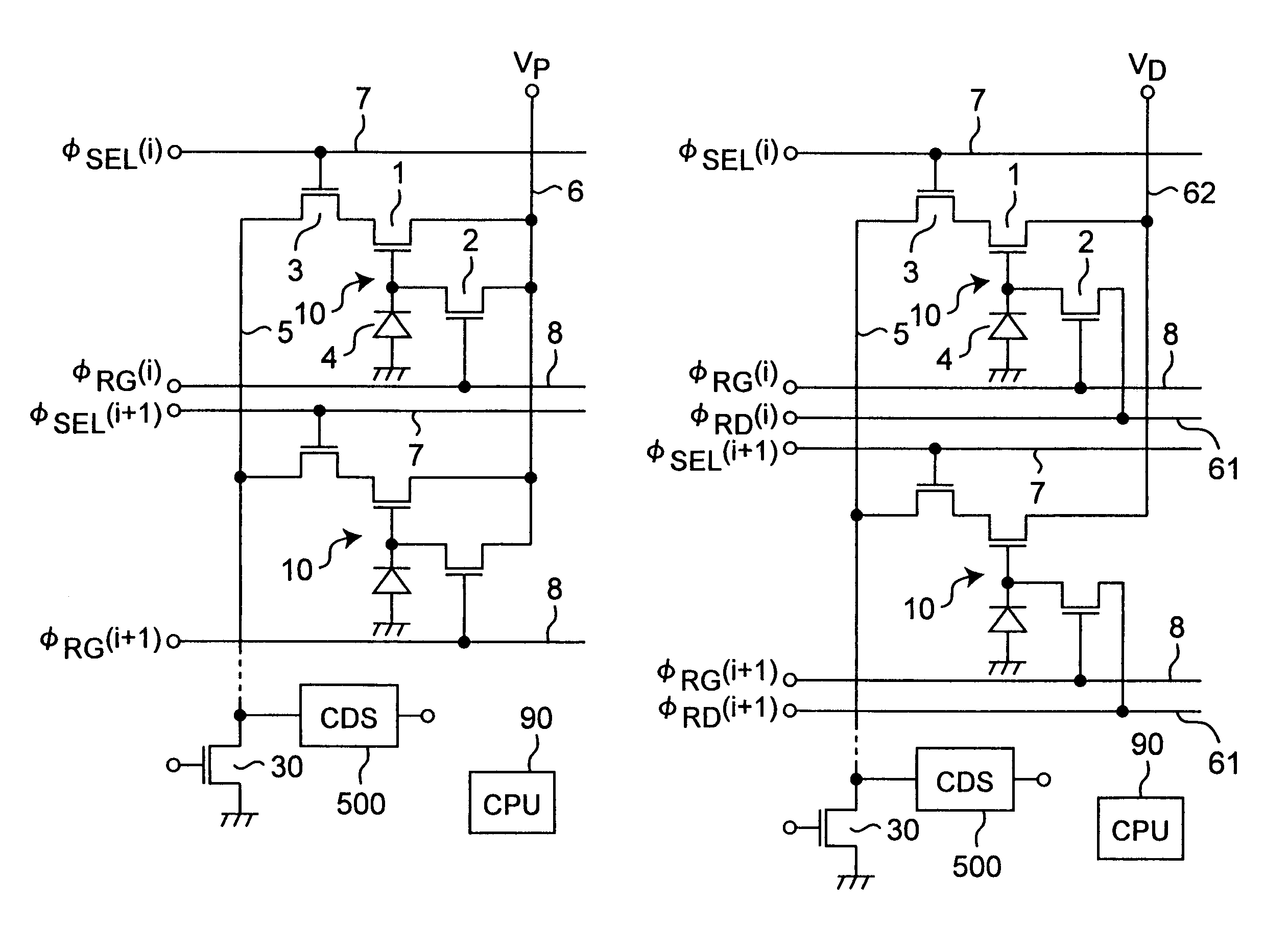

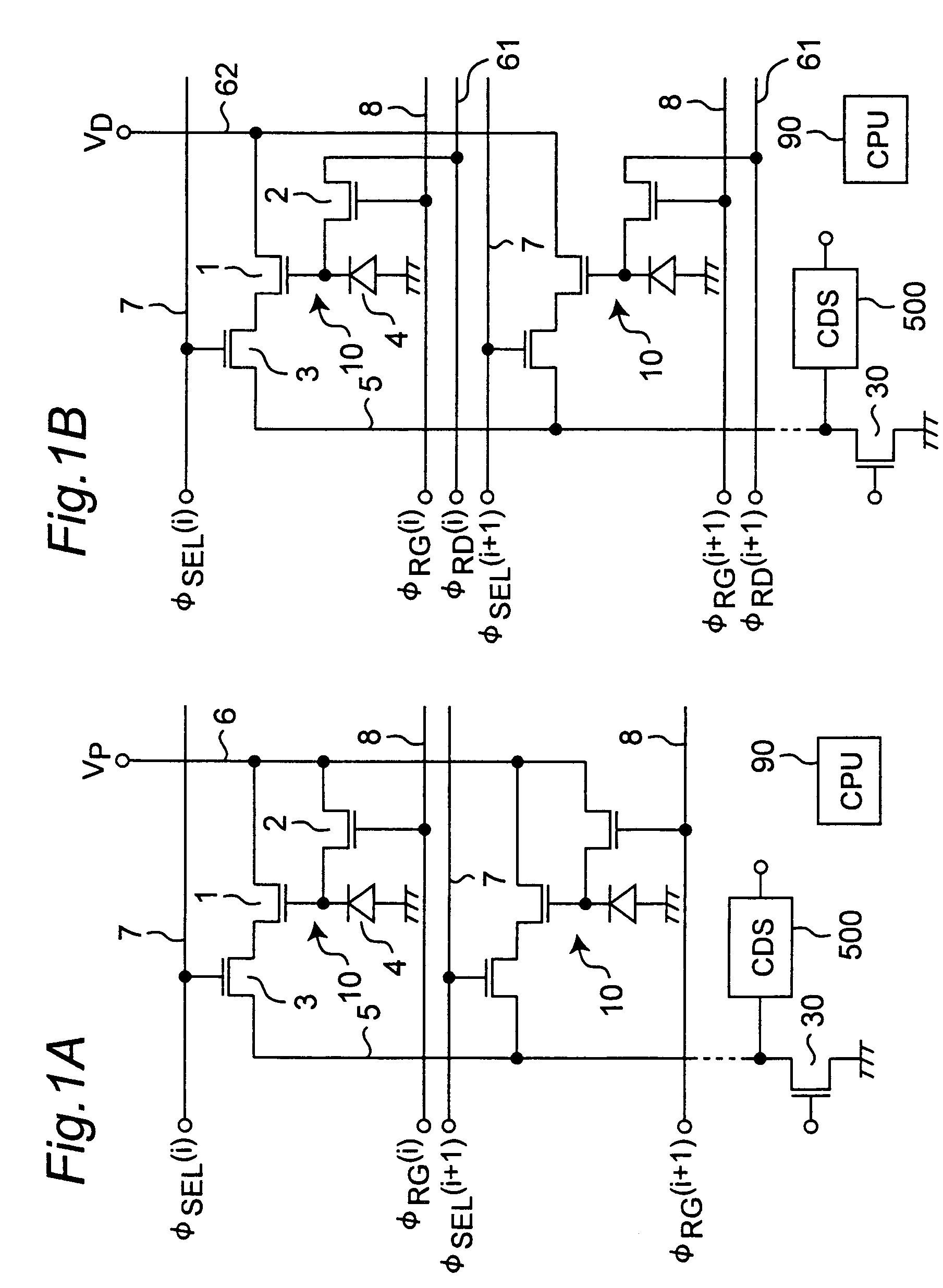

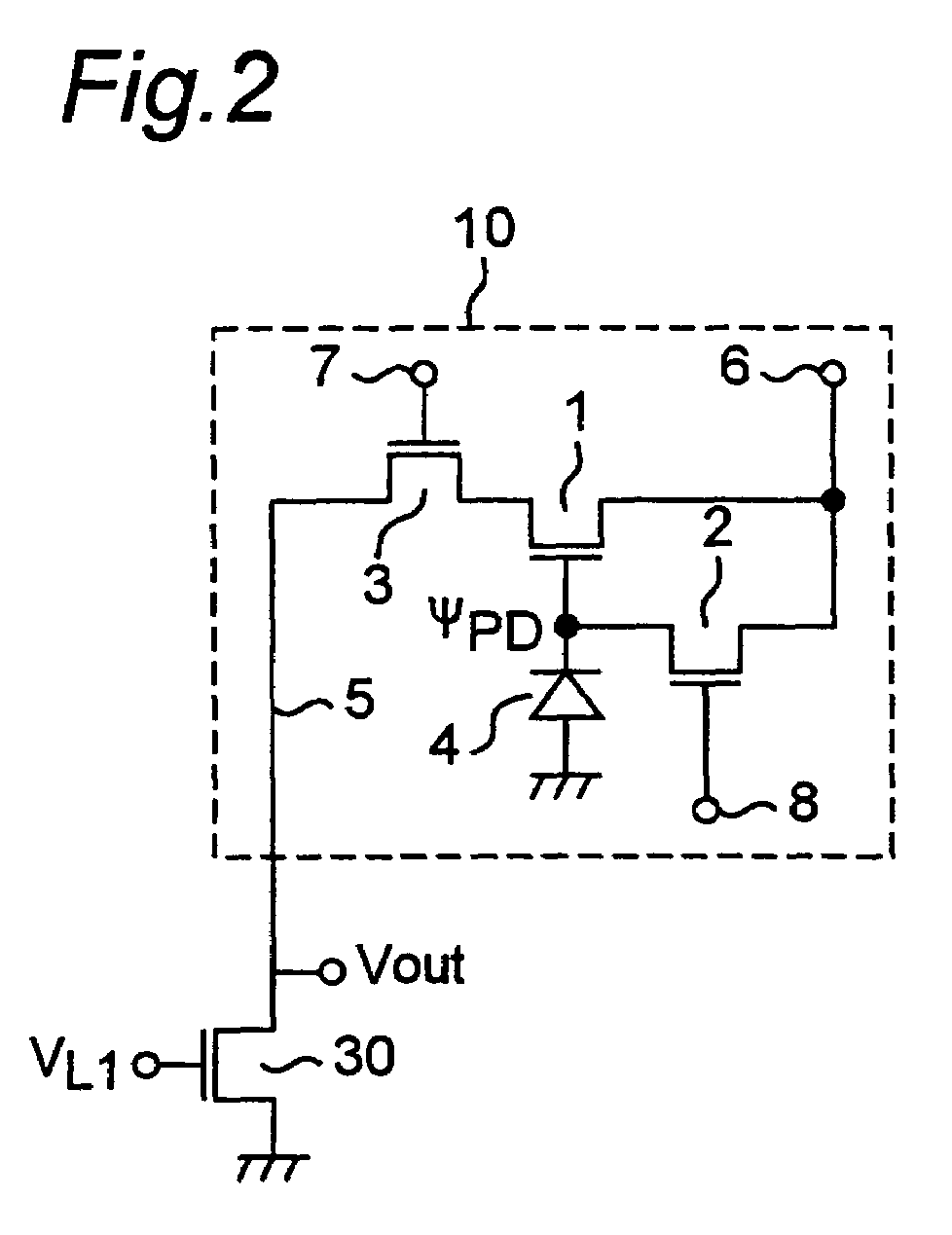

Amplification-type solid-state image pickup device incorporating plurality of arrayed pixels with amplification function

InactiveUS20050001148A1Reducing imageReduce noiseTelevision system detailsTelevision system scanning detailsSub thresholdSubthreshold conduction

An amplification-type solid-state image pickup device of the present invention repeats, in every frame, a signal level readout period, a first reset period, a reset level readout period, a second reset period, and a third reset period in this order. In the first reset period and the third reset period, a MOS transistor for reset is set to execute a soft reset operation with a sub-threshold current, while in the second reset period, the MOS transistor for reset is set to execute a hard reset operation so as to fix the potential of a photon-electron conversion region to a drain potential. This makes it possible to reduce both reset noise and image retention with a simple constitution.

Owner:SHARP KK

Methods and apparatus for ultra-low leakage analog storage

ActiveUS7436221B2Minimize leakage currentMinimizes conductionElectric analogue storesElectronic switchingAudio power amplifierDevice form

An analog storage cell circuit includes a switch that minimizes subthreshold conduction and diode leakage, as well as an accumulation-mode coupling mechanism to minimize overall switch leakage to minimize accumulation-mode leakage. In one embodiment, an analog storage circuit includes a sample and hold circuit including an amplifier having first and second inputs and a switch coupled to the first input of the amplifier. The switch includes a first switching device forming a core of the switch, a second switching device coupled to the first switching device to disconnect the first switching device from a first terminal during the hold phase, and a third switching device coupled to the first switching device to connect the first switching device to a second terminal during the hold phase to minimize accumulation mode conduction in the first switching device.

Owner:MASSACHUSETTS INST OF TECH

Semiconductor memory device

When a command is input to a semiconductor memory device, a sub-threshold current is reduced to a predetermined value corresponding to the command. After the reduction of the sub-threshold current is completed, the semiconductor memory device starts to operate corresponding to the command.

Owner:LONGITUDE LICENSING LTD

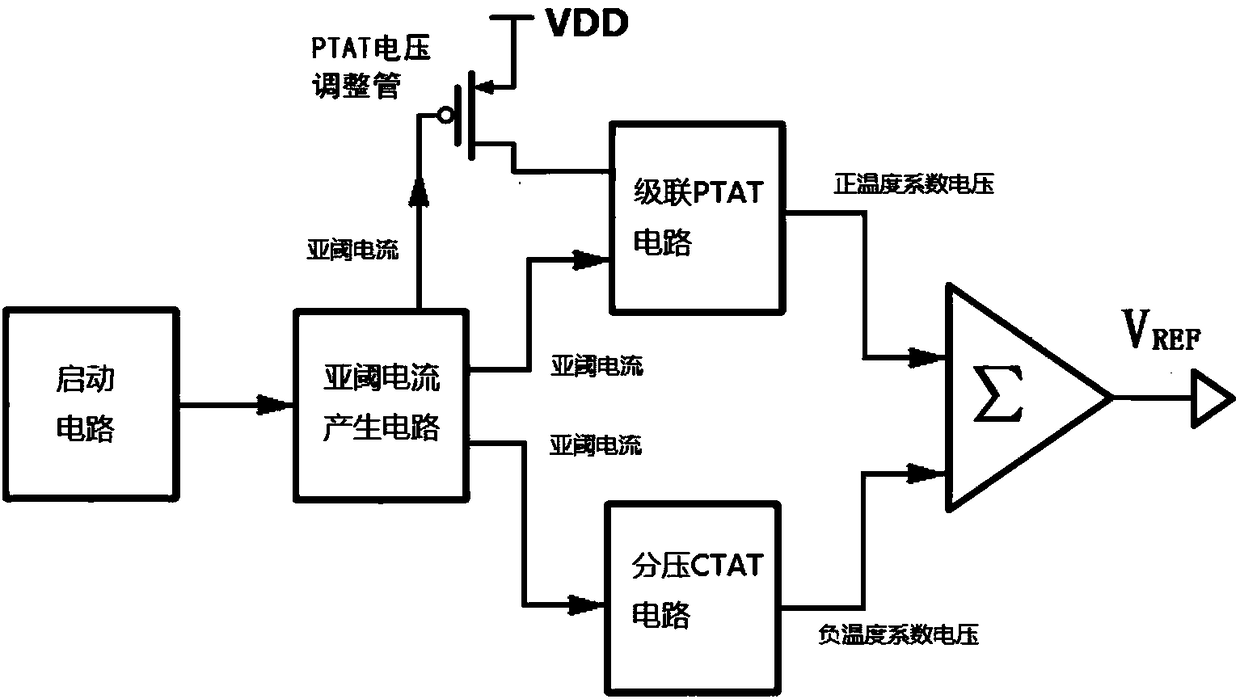

Bandgap reference voltage circuit with ultra-low power consumption under full-CMOS subthreshold work

PendingCN108594924ASmall working currentReduce power consumptionElectric variable regulationNegative temperatureCurrent generation

The invention relates to a bandgap reference voltage circuit with ultra-low power consumption under full-CMOS subthreshold work. The circuit comprises a starting circuit, a subthreshold current generation circuit, a voltage division CTAT circuit, a cascading PTAT circuit and a PTAT voltage adjustment tube. Through the starting circuit, all the circuits get rid of the null point and work at a normal work point; the subthreshold current generation circuit is used for generating subthreshold current of an MOS tube, and accordingly all the circuits work in a subthreshold state; the voltage division CTAT circuit is used for lowering the negative temperature coefficient of the circuit; the cascading PTAT circuit is used for generating PTAT voltage; the PTAT voltage can be adjusted through multi-grade segmentation, and the PTAT voltage adjustment tube 5 is used for adjusting current in the cascading PTAT circuit 4. Through the design of the full-CMOS subthreshold work, the whole working current is greatly lowered, finally the output voltage can be lower than 1 V, the temperature coefficient of the output voltage can be precisely adjusted, and accordingly the output voltage has high temperature precision.

Owner:JIANGSU COLLEGE OF INFORMATION TECH

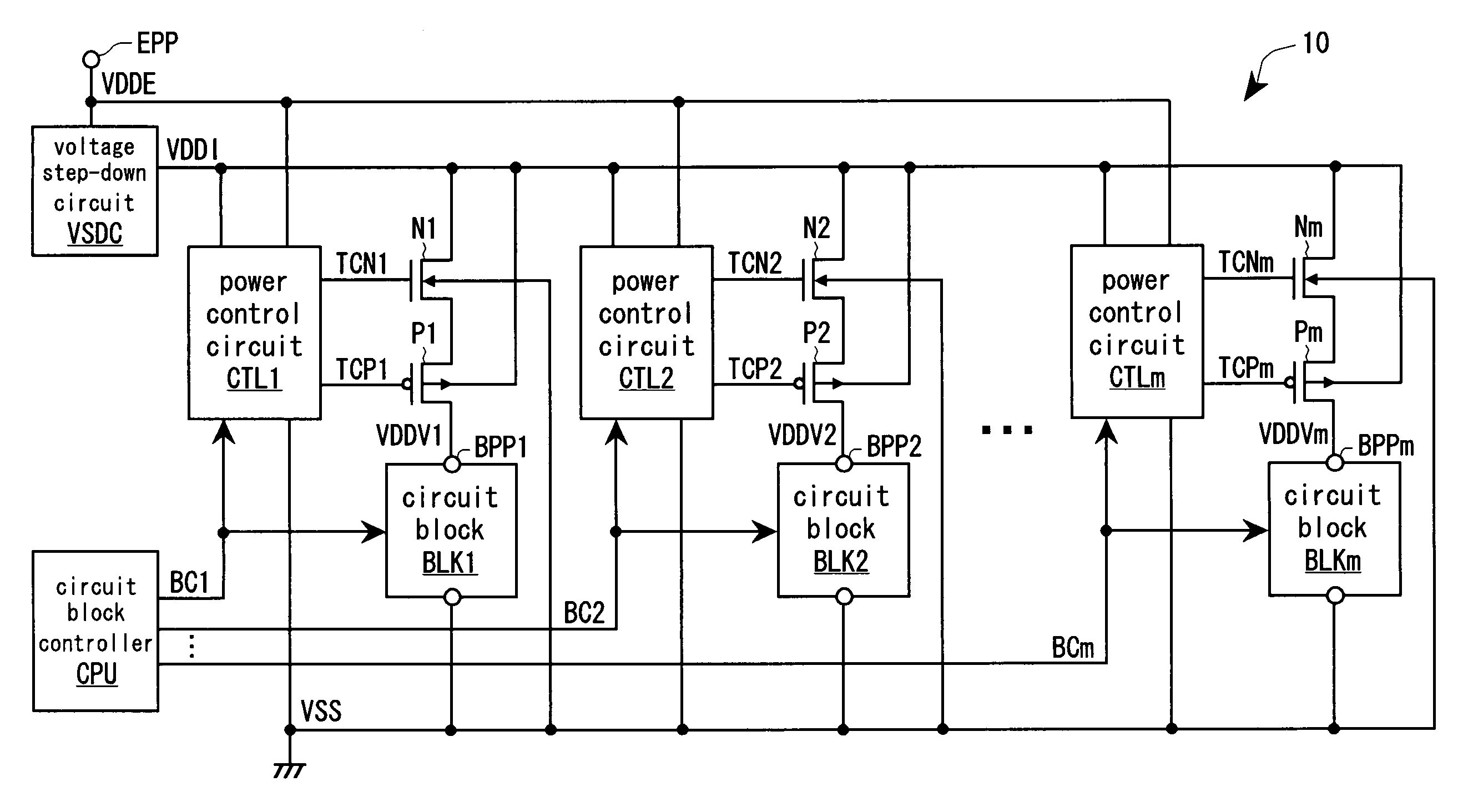

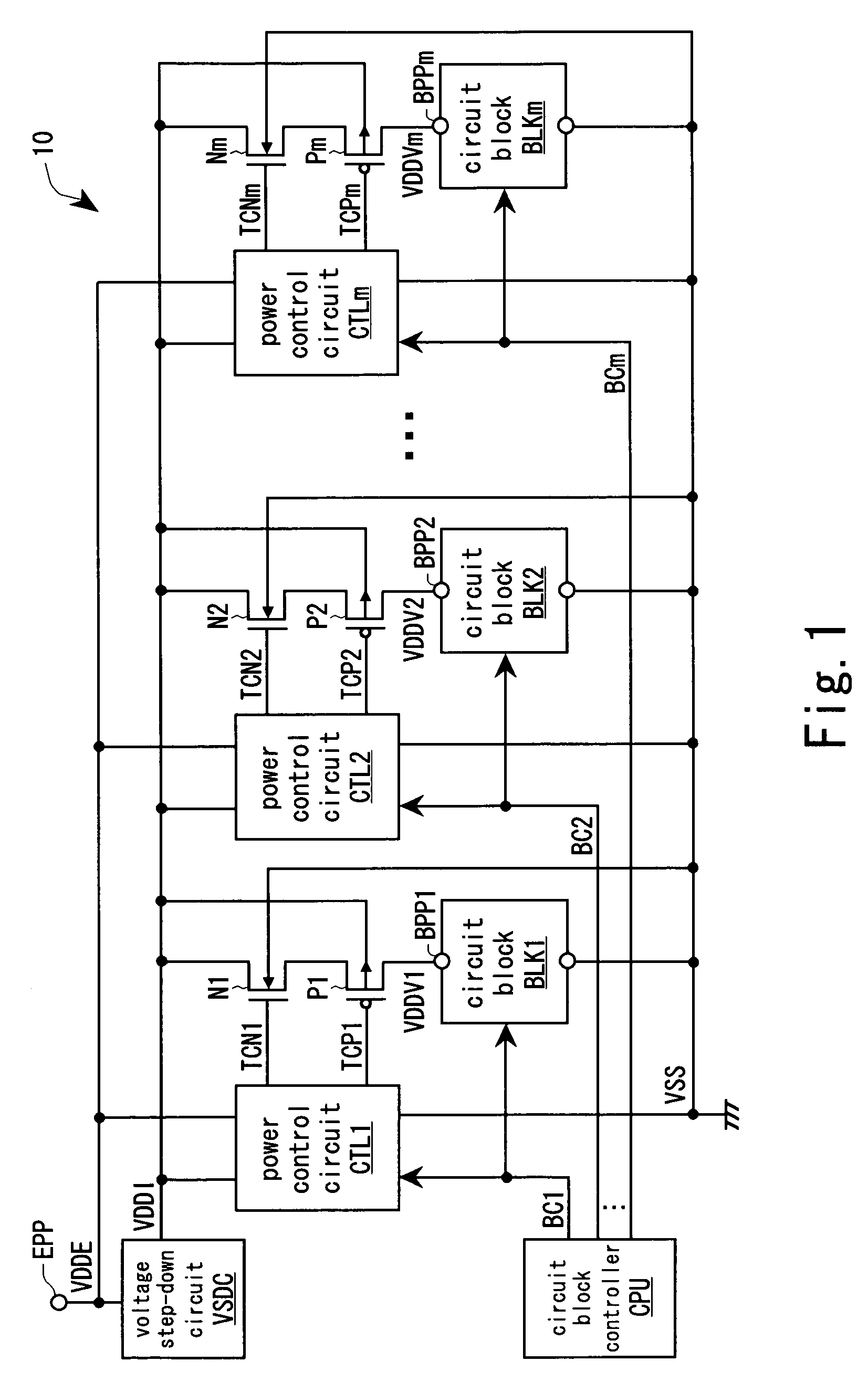

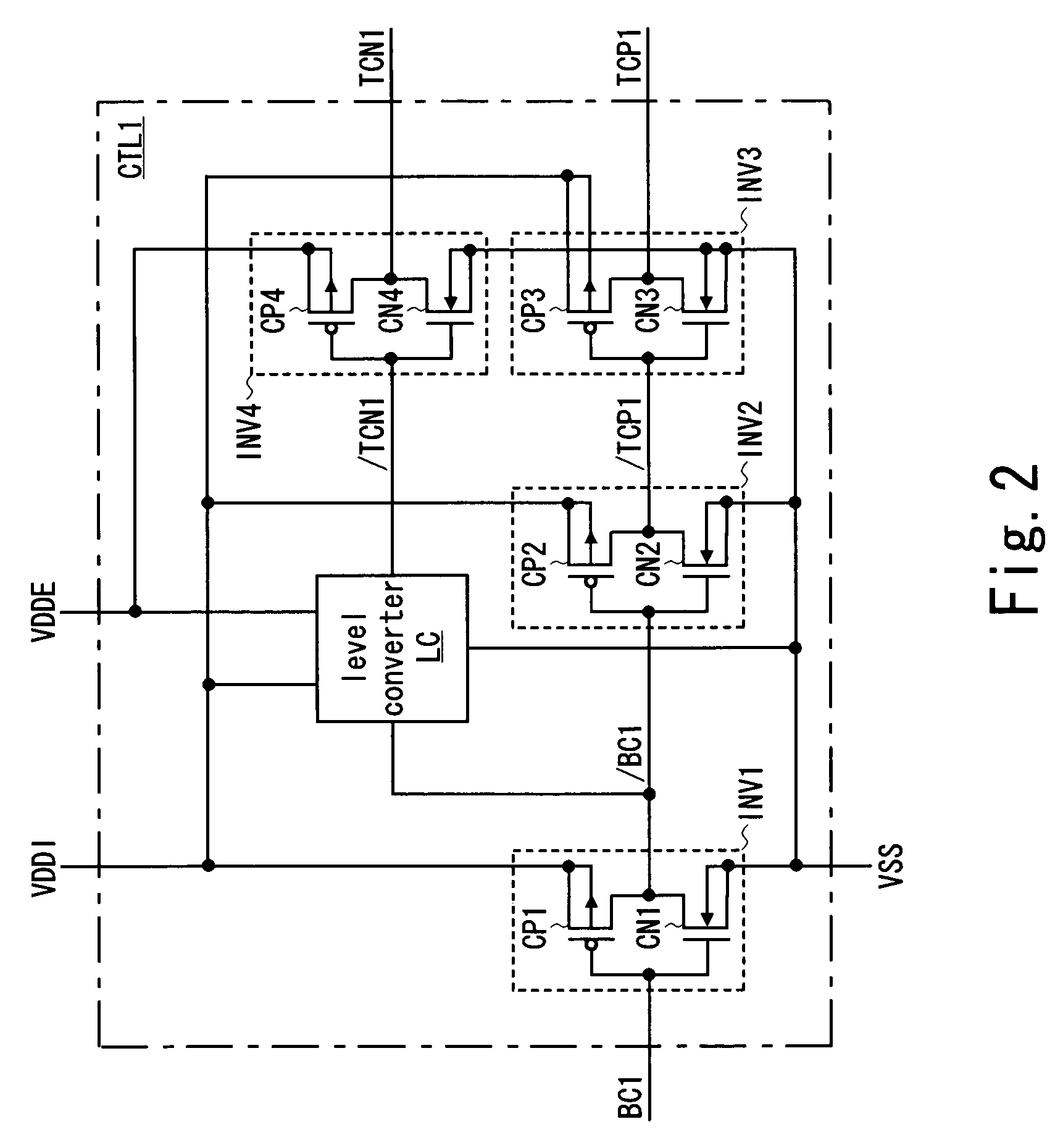

Power control circuit with reduced power consumption

InactiveUS7019418B2Reduce power consumptionSimple structureTransistorBoards/switchyards circuit arrangementsEngineeringVirtual power

Owner:SOCIONEXT INC

Amplification-type solid-state image pickup device incorporating plurality of arrayed pixels with amplification function

InactiveUS7012238B2Reducing imageReduce noiseTelevision system detailsTelevision system scanning detailsSub thresholdSubthreshold conduction

An amplification-type solid-state image pickup device of the present invention repeats, in every frame, a signal level readout period, a first reset period, a reset level readout period, a second reset period, and a third reset period in this order. In the first reset period and the third reset period, a MOS transistor for reset is set to execute a soft reset operation with a sub-threshold current, while in the second reset period, the MOS transistor for reset is set to execute a hard reset operation so as to fix the potential of a photon-electron conversion region to a drain potential. This makes it possible to reduce both reset noise and image retention with a simple constitution.

Owner:SHARP KK

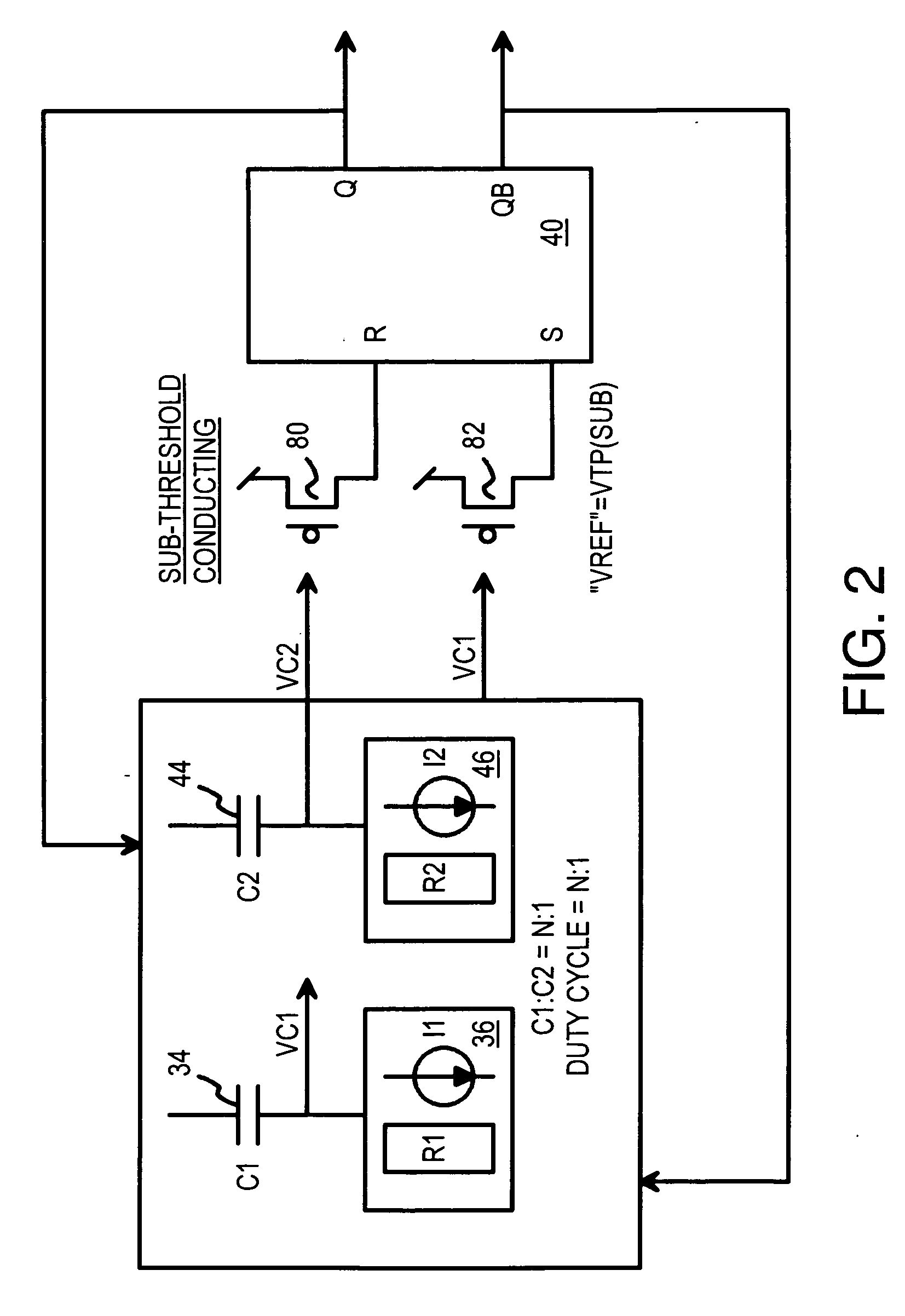

Low-Voltage Oscillator with Capacitor-Ratio Selectable Duty Cycle and Single-Input Sub-Threshold-Conducting Comparators to S-R Latch

InactiveUS20090146749A1Pulse generation by bipolar transistorsPulse generation by logic circuitsCapacitanceSub threshold

An oscillator operates at a very low voltage yet has a duty cycle that is set by a ratio of capacitors that are charged and discharged. Sub-threshold p-channel transistors conduct sub-threshold currents below the normal threshold voltage, and drive set and reset inputs of a set-reset S-R latch. The S-R latch drives the oscillator outputs. The oscillator outputs feed back to charging p-channel transistors that charge one plate of the capacitors. During half of the cycle, the charging p-channel transistor is off, allowing one plate of the capacitors to discharge through an n-channel discharge transistor. After a period of discharge determined by the capacitance of the capacitor, the gate of a sub-threshold p-channel transistor falls enough for sub-threshold current to flow, triggering the set or reset input of the S-R latch. Since sub-threshold currents are needed to toggle the S-R latch, the oscillator begins to oscillate below the threshold voltage.

Owner:HONG KONG APPLIED SCI & TECH RES INST

NMOS-based feedback power-clamp for on-chip ESD protection

ActiveUS8369054B2Emergency protective arrangements for limiting excess voltage/currentArrangements responsive to excess voltageHigh resistanceSub threshold

A power-to-ground clamp transistor provides electrostatic discharge (ESD) protection. A filter capacitor and resistor generate a filter voltage that is buffered by three stages to drive the gate of the clamp transistor. The filter capacitor is about twenty times smaller than in a conventional clamp circuit. Feedback in the circuit keeps the clamp transistor turned on after the R-C time constant of the capacitor and resistor in the filer has elapsed, allowing for a smaller capacitor to turn on the clamp transistor longer. A sub-threshold-conducting transistor in the first stage conducts only a small sub-threshold current, which extends the discharge time of the first stage. The gate of the sub-threshold-conducting transistor is driven by feedback from the second stage. A feed-forward resistor has a high resistance value to slowly raise the voltage of the second stage from the filter voltage, and thus slowly raise the gate of the sub-threshold-conducting transistor.

Owner:HONG KONG APPLIED SCI & TECH RES INST