Silicon-on-insulator chip having an isolation barrier for reliability

a technology of isolation barrier and silicon on the silicon-on-insulator chip, which is applied in the field of silicon-on-insulator chip having an isolation barrier, can solve the problems of reducing the overall manufacturing yield compromising the reliability and performance of the integrated circuit, and losing manufacturing yield, so as to reduce the processing steps, reduce the exposure to reactive ion etching, and reduce the effect of charging

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

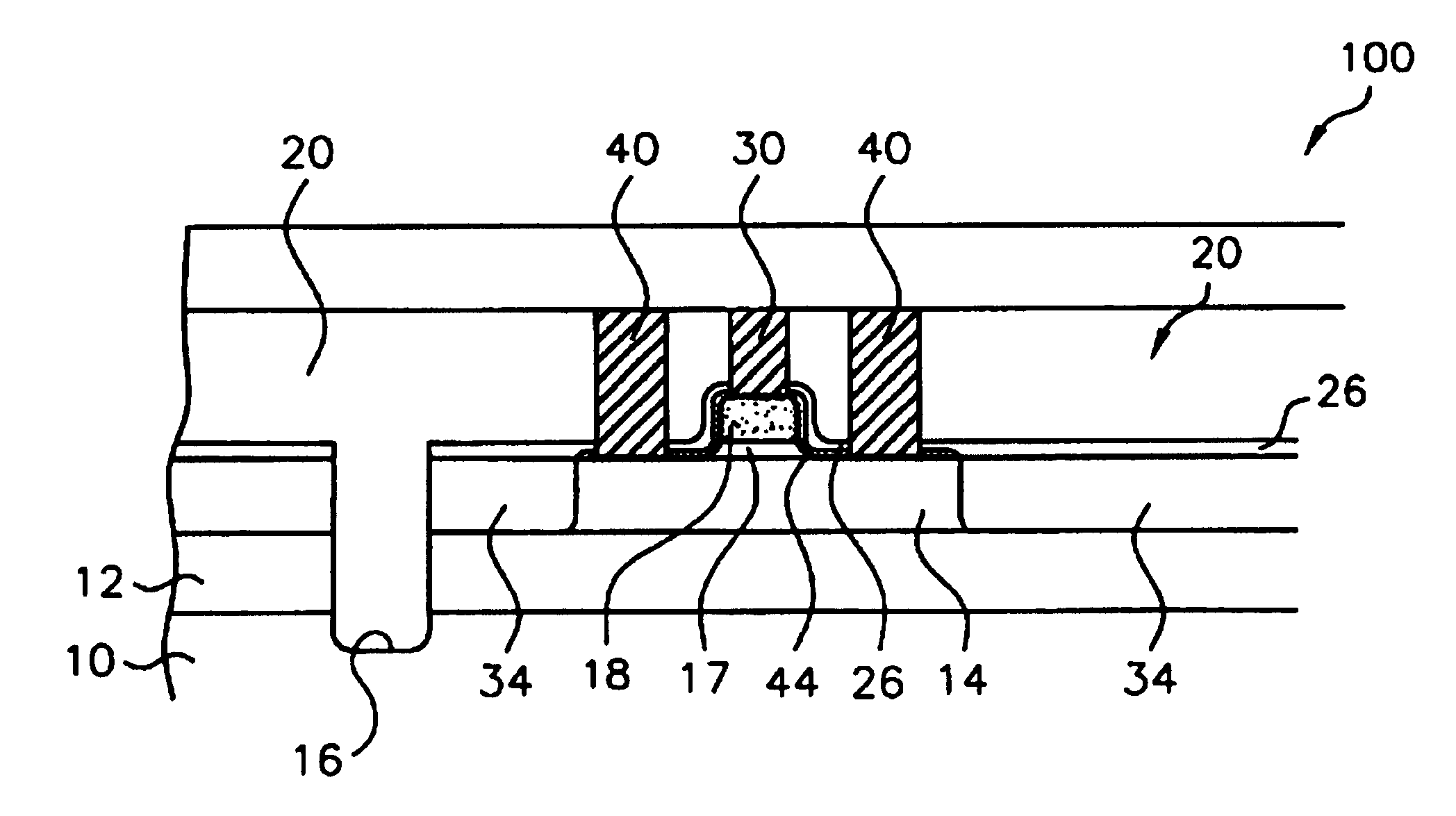

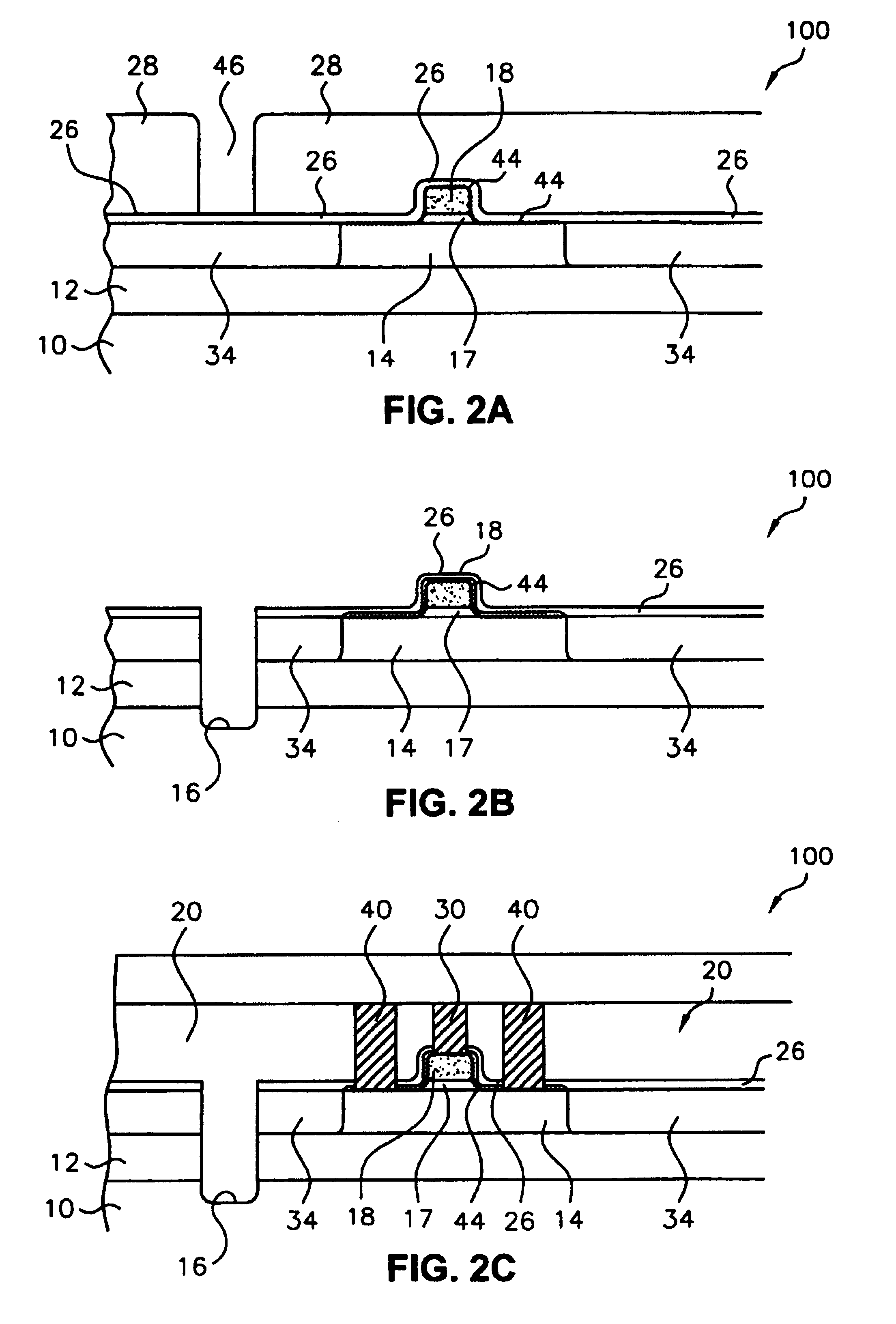

[0038]the process of manufacturing SOI chip 100 having a groove 16 as an integrated diffusion barrier includes the following steps (illustrated in FIG. 2D). First, a device having substrate 10, buried oxide layer 12, silicon layer 14 with at least one trench 34, gate 18, and silicide layer 44 is provided (Step 500). Passivation layer 26 is deposited (Step 510), resist is applied (Step 520), groove 16 is etched (Step 530), resist 28 is removed (Step 540), barrier material 20 is deposited (Step 550), barrier material 20 is polished (Step 560), metal contact lithography is performed (Step 570), and a final CMP is done (Step 580). A single photolithography mask or resist 28 is deposited (Step 520). A single reactive ion etching step is applied (Step 530). Finally, the resist 28 is stripped (Step 540).

[0039]The first embodiment of the process of manufacturing SOI chip 100 having a groove 16 as an integrated diffusion barrier requires only three extra steps over a conventional SOI chip 1 ...

second embodiment

[0042]Thus, the process of manufacturing SOI chip 101 having a groove 16 as an integrated diffusion barrier includes the following steps. First, a device having a substrate 10, buried oxide layer 12, silicon layer 14 with at least one trench 34, gate 18, and silicide layer 44 is provided (Step 500). Resist is applied (Step 520), groove 16 is etched (Step 530), and resist 28 is removed (Step 540). Then passivation layer 26 is deposited (Step 510). Subsequently, barrier material 20 is deposited (Step 550), barrier material 20 is polished (Step 560), metal contact lithography is performed (Step 570), and a final CMP is done (Step 580).

third embodiment

[0043]the SOI chip 102 of the present invention is illustrated in FIG. 4. SOI chip 102 shown in FIG. 4 is similar to SOI chip 101 of FIG. 3 in that passivation layer 24 is deposited in groove 16, and passivation layer 26 is deposited over silicon layer 14 (including trench 34) and gate 18, after groove 16 is formed in the SOI chip. Passivation layer 24 may be a dielectric such as silicon nitride or a composite of silicon dioxide and silicon nitride. Unlike the process used to manufacture SOI chip 101 of FIG. 3, however, an anisotropic etch is then applied to groove 16 of SOI chip 102. The anisotropic etch removes a portion of passivation layer 24 extending along the bottom of groove 16. Consequently, passivation layer 24 extends into groove 16 only along the side walls of groove 16 and the bottom of groove 16 is open to silicon substrate 10. Groove 16 retains the dielectric and passivation properties, however, on its side walls.

[0044]Fill material 50 is then deposited in groove 16, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More