Manufacturing method for cilicon epitaxial wafer for 6'' VDMOS tube

A technology of silicon epitaxial wafer and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of increasing parameter control difficulty, high central resistivity of epitaxial wafer, and large edge.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings:

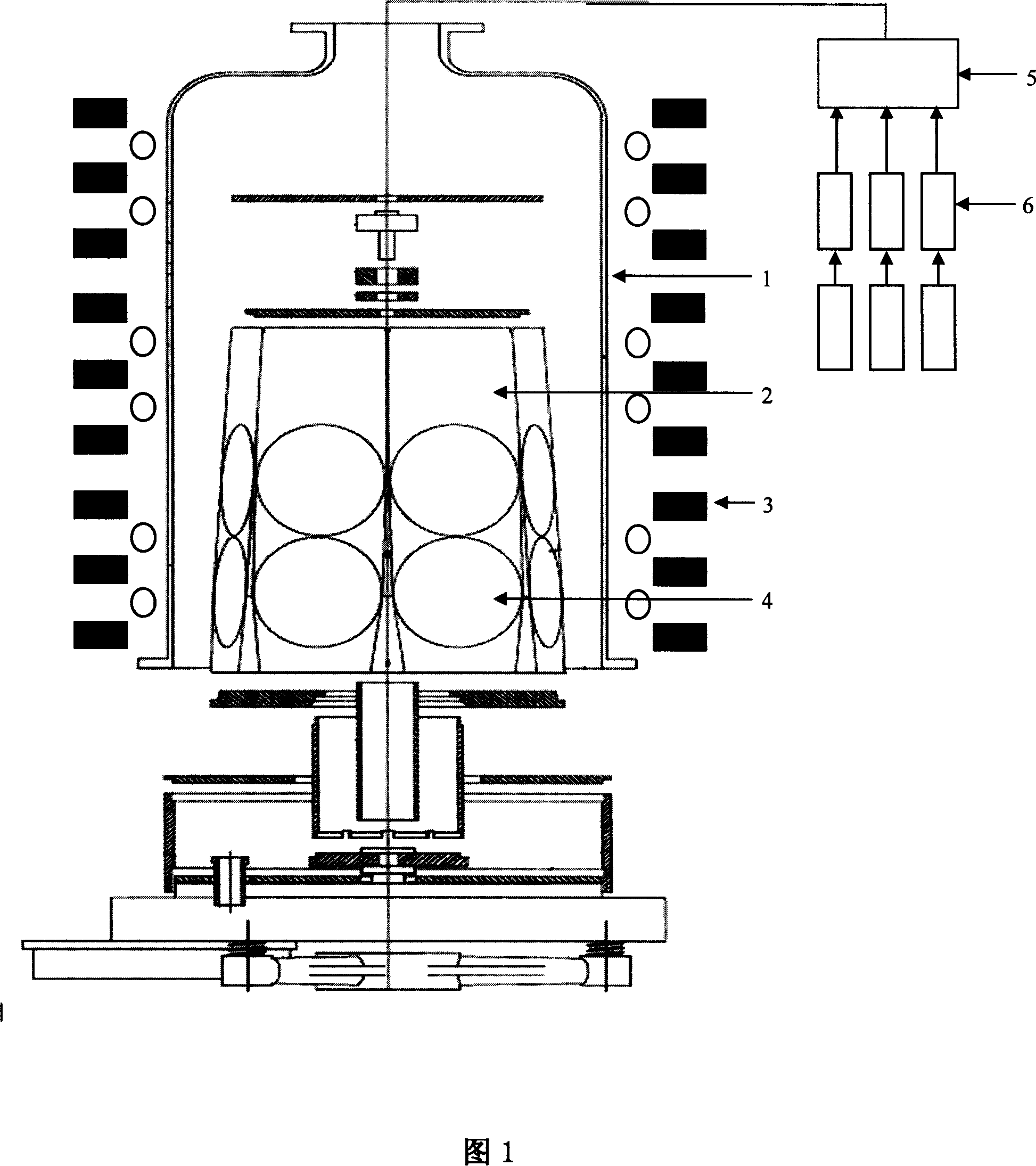

[0018] The equipment used in the present invention is a PE-2061S epitaxial furnace produced in Italy, as shown in Figure 1. The base is a high-purity graphite surface that has been cracked and encapsulated with high-purity SiC, heated by high-frequency induction, and the hydrogen purifier is adsorbed by molecular sieves. is 99.99999%. In the figure: 1 is a quartz reactor; 2 is a graphite base; 3 is a heating coil; 4 is a silicon substrate sheet; 5 is a gas distribution system; 6 is a gas flow control system.

[0019] Reactor and substrate cleaning: The quartz bell and the quartz support must be carefully cleaned before high-resistance epitaxy to remove the impurity atoms and residues adsorbed on the inner wall of the quartz reactor and quartz parts.

[0020] Graphite susceptor treatment: Before growing epitaxial wafers, the susceptor must...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More